# Performance, Reliability and Yield considerations in state-of-the-art SiC Diode and MosFET technologies during ramp-up

Thomas NEYER, tech. fellow, SiC Technology

**ON Semiconductor®**

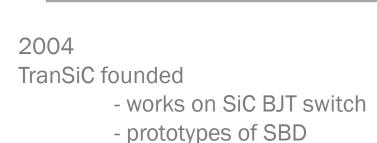

# **SiC History @ ON Semiconductor**

2011 2015

Fairchild bought TranSiC

- SBD released on 6" SiC wafer

- MosFET Gen1 start 2013

- setup Epitaxy line

- setup 6" manufacturing line

Gen1 1200V SBD

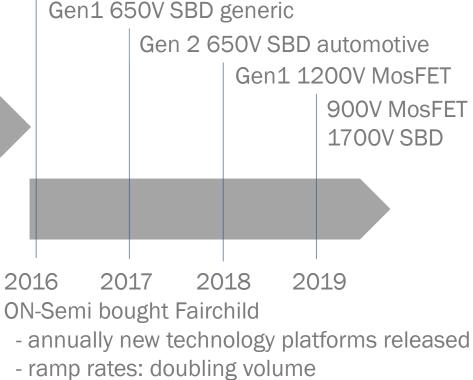

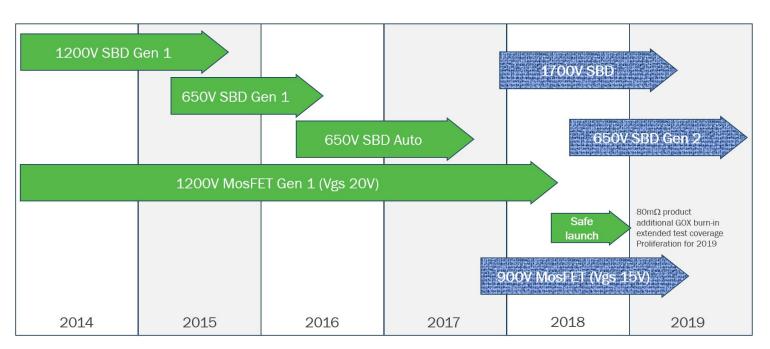

## **ON's status chart for SiC**

Product\_releasesDiodes:

4A - 50A for 650V 6A - 50A for 1200V 25A - 100A for 1700V available as discretes and in modules ... releasing shortly

#### MosFET:

80mW 1200V in T0247 released – safe launch from Q2/2019:

$20m\Omega$ ,  $40m\Omega$ ,  $160m\Omega$  in TO247-3L Q2 same products in D2PAK-7L, TO247-4L

SiC power modules will cont release 2019/20

TO-247-3L TO-247-2L TO-220-2L TO-220FP-2L D2PAK DPAK PQFN 88 TO-247-4 D2PAK-7L

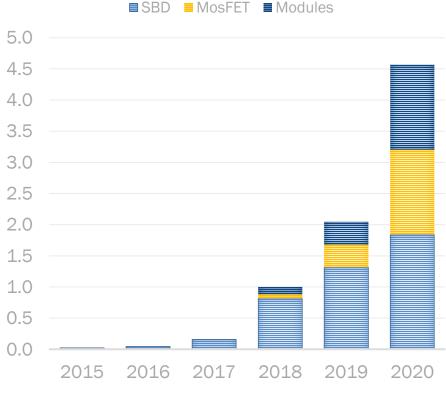

## SiC 6" Volume ramp-up

Large Fab capacity available: >10.000 WSPW Global development - 24hrs: Asia/EU/US From 2021: supply chain vertical integrated

#### SIC WEEKLY WAFER STARTS

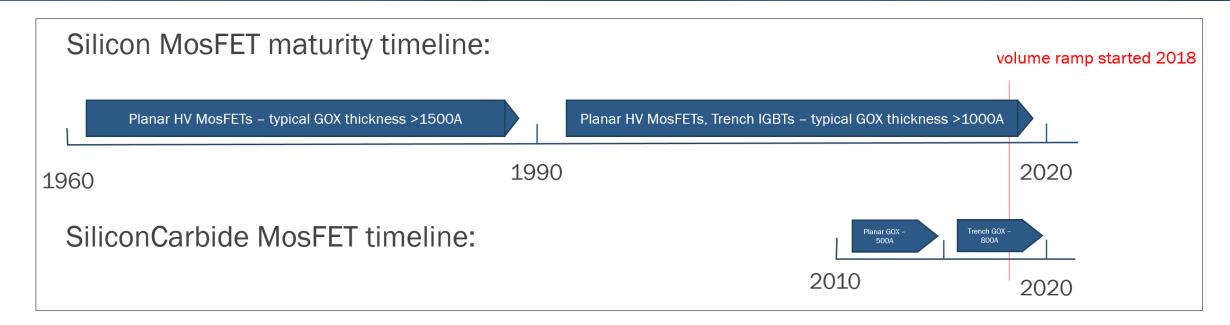

# **Challenges - SiC MosFET in its infancy**

SiC IDMs offer passive and active devices in comparable packages and modules

- ease of use

- drastic switching loss reduction

- as of today SiC technology enables system cost, weight and size reduction

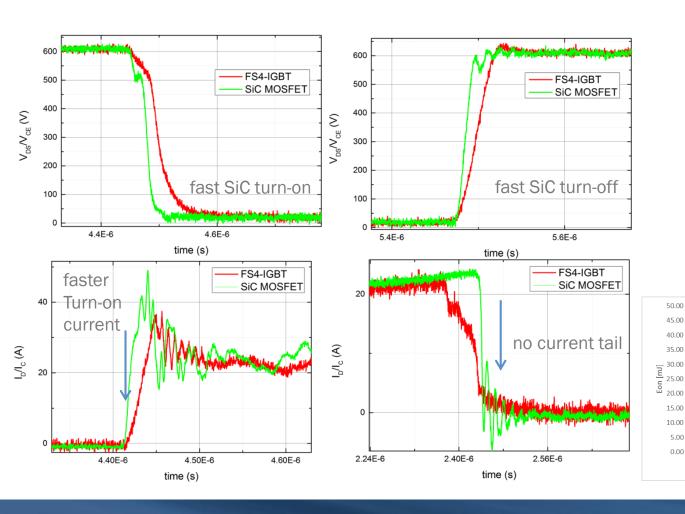

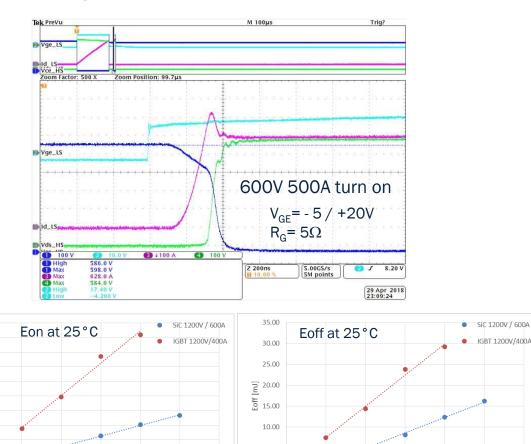

## Performance SiC MosFET vs IGBT

#### ON Semi 1200V IGBT 20A vs. SiC MOSFET

under identical drive conditions

#### Paralleling of $20m\Omega$ ON Semi SiC MosFETs vs IGBTs

0.00

5.00 0.00

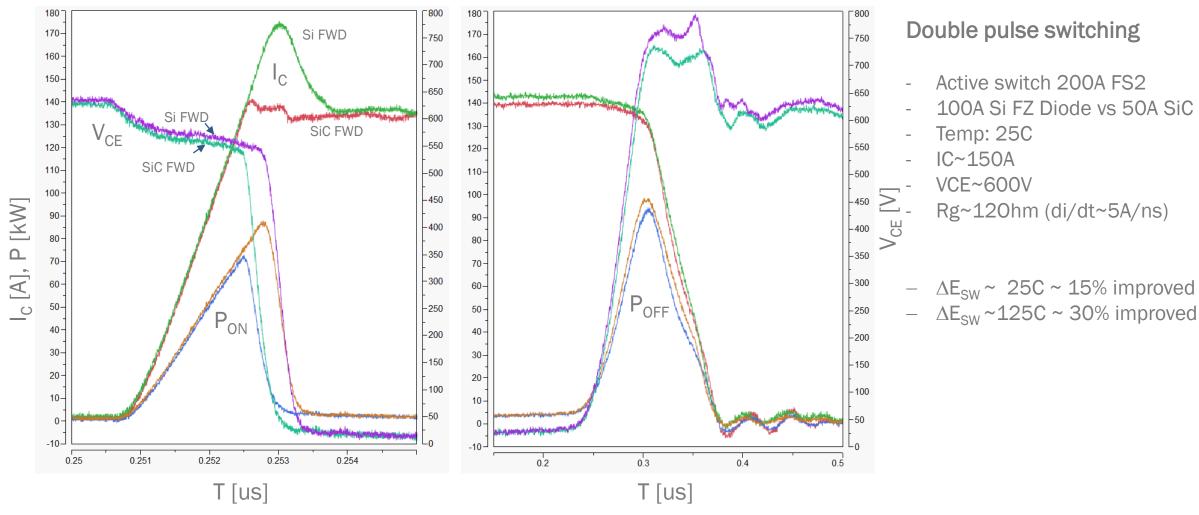

## 1200V Transient comparison FS2 IGBT with FWD Si vs SiC

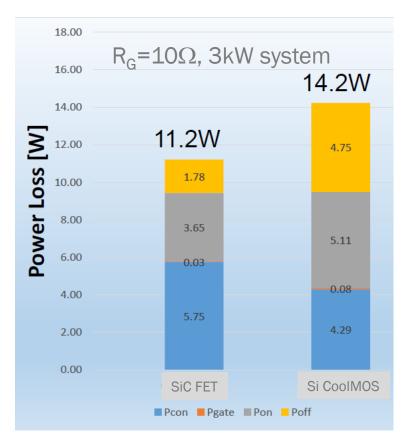

## Performance SiC MosFET vs Si SuperJunction FETs

## Example 900V SiCFET vs 600V SuperJunction FET for CCM PFC

|                            |             | NVHL060N090SC1 | IPW60R060C7   |

|----------------------------|-------------|----------------|---------------|

| R <sub>DS(ON)</sub> @ Typ. | 25°C        | 72             | 52            |

|                            | 100°C       | 82             | 84            |

| Size                       | Measurement | 2,980 x 2,980  | 3,500 x 5,700 |

|                            | Normalized  | 1.00           | 2.25          |

|                            | Die Photo   |                |               |

|                | Q     | Vgs  |  |  |  |

|----------------|-------|------|--|--|--|

|                | [nC]  | [V]  |  |  |  |

| NVHL060N090SC1 |       |      |  |  |  |

| Qgs            | 26.9  |      |  |  |  |

| Qgd            | 14.4  |      |  |  |  |

| Qg             | 72.6  | 15.0 |  |  |  |

| IPW60R040C7    |       |      |  |  |  |

| Qgs            | 25.0  |      |  |  |  |

| Qgd            | 35.4  |      |  |  |  |

| Qg             | 111.1 | 10.0 |  |  |  |

| @ 400V    | NVHL060N090SC1 | IPW60R040C7 |  |

|-----------|----------------|-------------|--|

| EOSS [uJ] | 12.1           | 12.0        |  |

| @ 400V    | NVHL060N090SC1 | IPW60R040C7 |  |

| QOSS [nC] | 87.5           | 534.0       |  |

due to low Q<sub>G</sub>, Q<sub>OSS</sub> and Q<sub>RR</sub> – SiC FET excellent in LLC as well

Public Information

# Challenges - SiC chip in discrete package

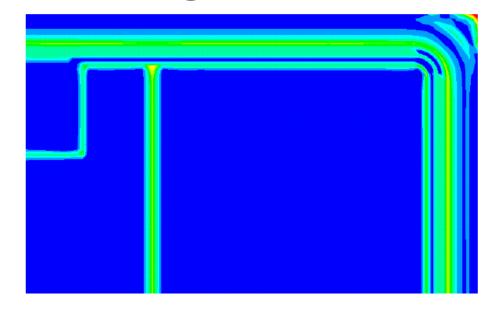

## Large SiC chips in discrete packages

| Material               | Si   | SiC  |

|------------------------|------|------|

| Elastic Modulus (Gpa)  | 130  | 410  |

| Tensile strength (Mpa) | 7000 | 3440 |

| Hardness (mohs)        | 6.5  | 9    |

| CTE (1E-6/C)           | 2.6  | 4.5  |

## Temperature cycling (-55C – 150C)

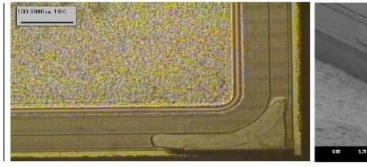

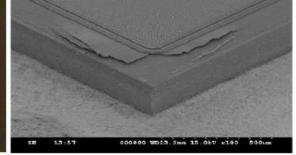

## FEA modeling discovers:

Dependent on chip design, certain locations experience >20 times stress and strain during cycling than Silicon chip

Overcame problem with patented design and optimized assembly BOM

## Stress in overmolded power modules

Package reliability (power cycling), cooling performance etc strongly dependent on material system. Fracture mechanics simulation possible

ON

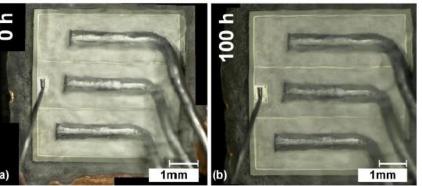

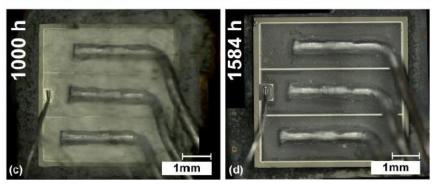

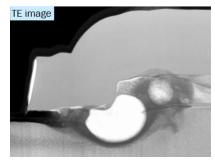

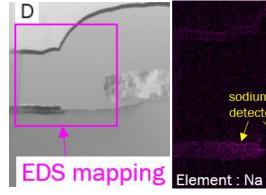

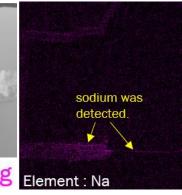

## Challenge - Edge termination in moisture

#### H3TRB stress Anodic corrosion in moist environments under stress

corrosion fails within 1<sup>st</sup> 168hrs

Proper SiC edge design survives >5000hrs under worst case H3TRB acceleration without any visible changes or electrical drifts

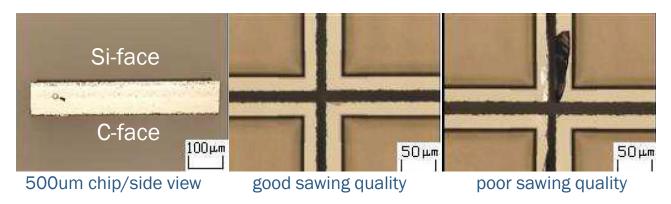

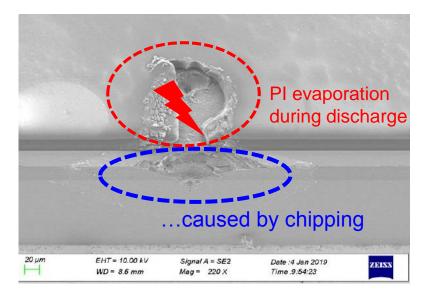

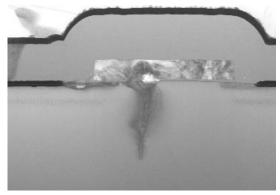

# Challenge - SiC dicing

#### SiC dicing typically done using

- diamond sawing (like Silicon but slower, more blade consumption)

- laser assisted methods

- plasma assisted methods

Trade off between dicing speed, scribe lane width, chip size and tape selection (glue thickness) much development on equipment and consumable side to optimize COO of SiC dicing strong correlation to product robustness

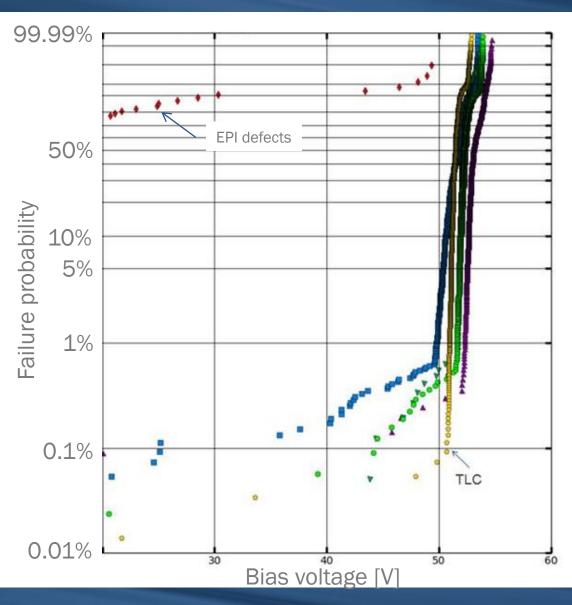

## Gate oxide integrity for SiC MosFETs and TDDB

## In mass production SiC MosFETs need

- optimized cleaning and gate oxide

- Very low electric field (<3 MV/cm)</li>

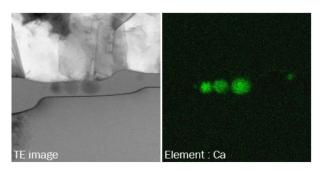

- tight Fab contamination control

- highest substrate and Epi quality

continuous monitoring of extrinsic failure rate required

## **Challenges – Gate oxide integrity**

#### Typical failure cases for GOX (HTGB – burn-in):

...caused by typical Fab contaminations and process imperfections

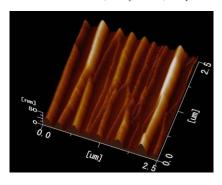

Correlation between surface morphology and breakdown characteristics of thermally grown SiO<sub>2</sub> dielectrics in 4H-SiC MOS Devices

and material defects/roughness

Yusuke Uenishi<sup>a</sup>, Kohei Kozono<sup>a</sup>, Shuhei Mitani<sup>b</sup>, Yuki Nakano<sup>b</sup>, Takashi Nakamura<sup>b</sup>, Takuji Hosoi<sup>a</sup>, Takayoshi Shimura<sup>a</sup>, Heiji Watanabe<sup>a</sup>

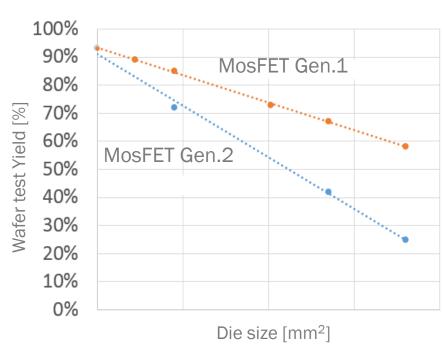

## D0 and Fab Yields for large die size

Size comparison: 200A Si IGBT and (equivalent) SiC MosFET

Substrate and Epi defects and differences in SiC Fab process lead to pronounced Yield detractors for "large" die sizes

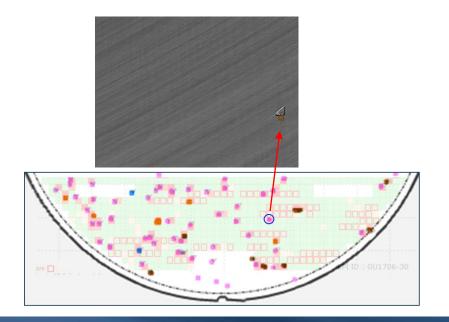

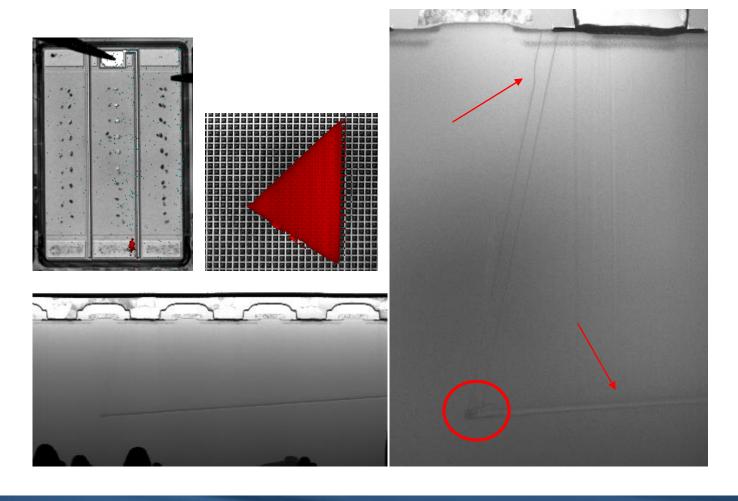

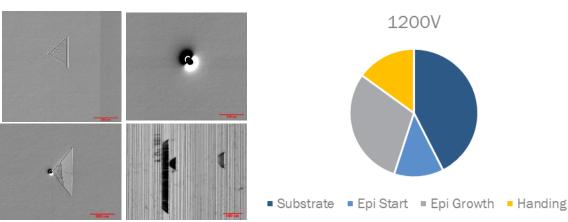

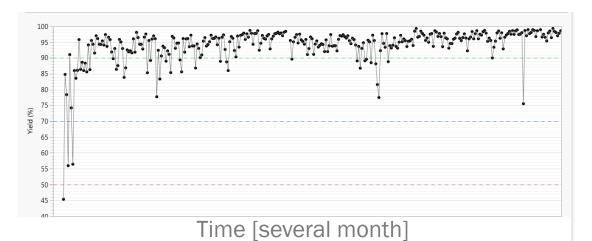

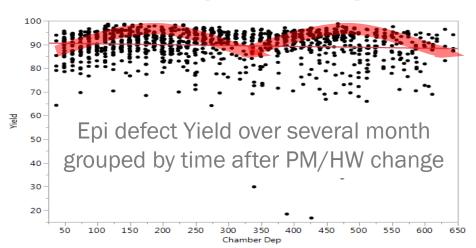

# Challenges - SiC Epitaxy and defectivity control

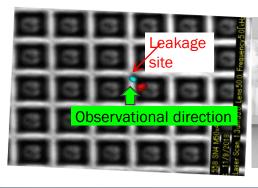

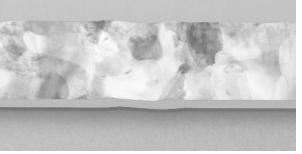

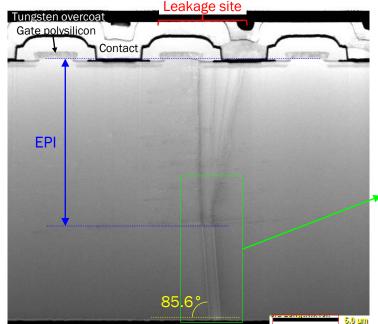

Tracing back burn-in failures to substrate defects

Made visible by post Epi scans

## **Epitaxy trend**

#### Epitaxy quality keeps improving

- high resolution Metrology

- selection of incoming substrate

- improved parts cleaning

Auto defect classification before Fab start to exclude killer defects

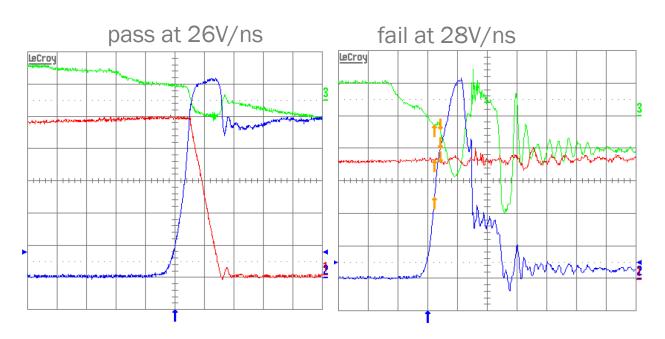

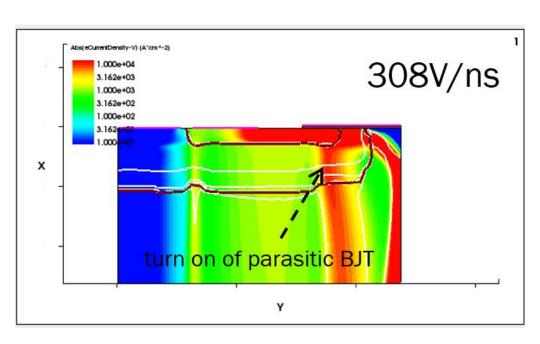

## Screening for new SiC "high dvdt" failure modes

Discrete **silicon** devices are speed-limited due to their intrinsic BJT latch-up effect (fast IGBT turn-off)

SiC MosFET dvdt simulation

Si IGBT in latch-up condition

SiC FET unit cell in latch-up condition

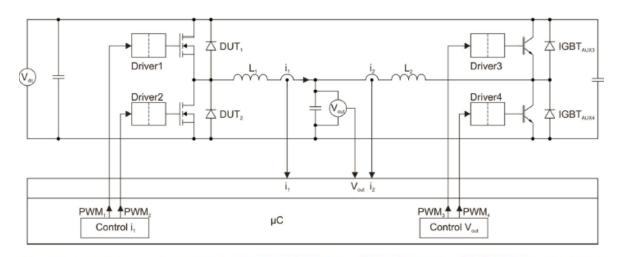

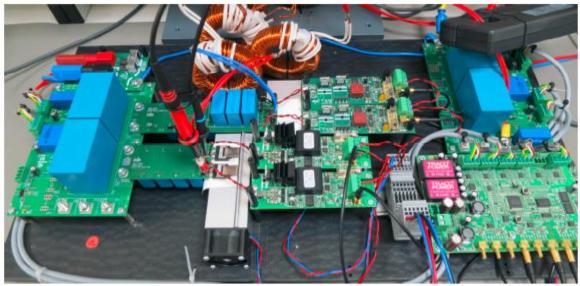

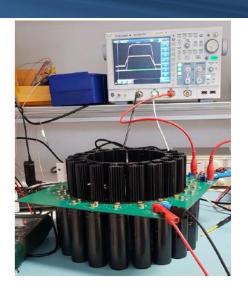

# H-bridge test – high dvdt (>100V/ns)

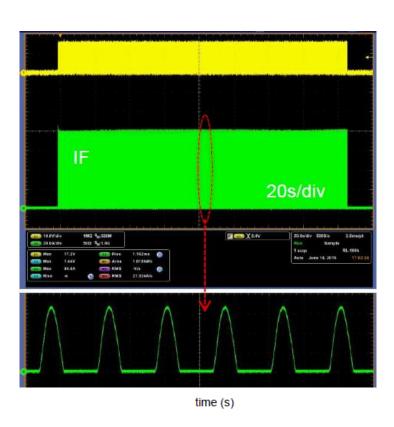

ON-Semi requires its SiC MOSFETs to undergo repetitive continuous operation tests (168 h). Where both Body-Diode and MOSFET are stressed at different dv/dt, ID and frequencies

- ➤ H-Bridge in Continuous Conduction mode

- $V_{DC} = 800 \text{ V}$

- $Frac{1}{2}$   $Frac{1}$   $Frac{1}{2}$   $Frac{1}{2}$   $Frac{1}{2}$   $Frac{1}{2}$   $Frac{1}{2}$   $Frac{1}{2}$   $Frac{1}{2}$   $Frac{1}$   $Frac{1}$   $Frac{1}{2}$   $Frac{1}$   $Frac{1}$   $Frac{1}$   $Frac{1}$   $Frac{1}$   $Frac{1}$  Frac

- $ightharpoonup T_J = 100 \, ^{\circ}\text{C}, \, I_{LOAD} \, \text{controlled}$

- > Test duration = 168 hrs

- $ightharpoonup R_{gon} = 1 22 \text{ Ohm}$

- $ightharpoonup R_{goff} = 1 5 Ohm$

- $V_{GS} = +20/-5 \text{ V}$

- ➤ 3 Lots 12 devices per Lot

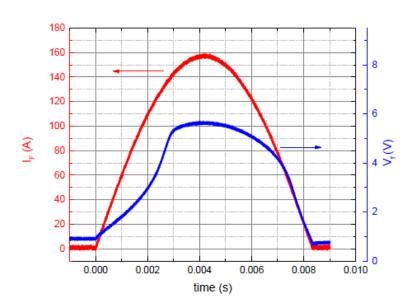

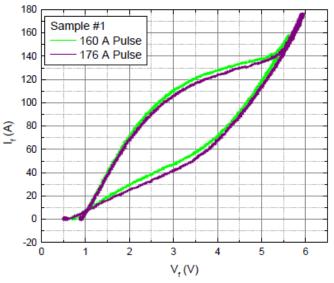

# SiC - Surge current testing

- Pulse shape and length can be freely controlled

- Useable for Diodes and MosFETs (1st and 3rd quadrant)

- Single and repetitive surge testing

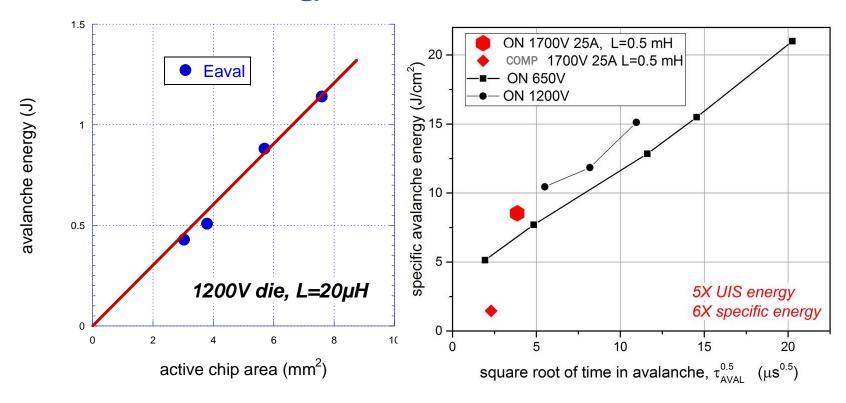

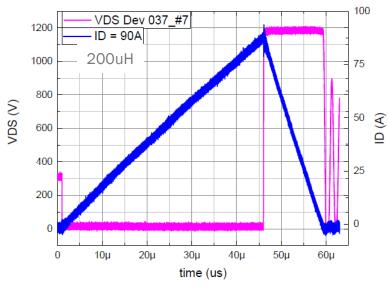

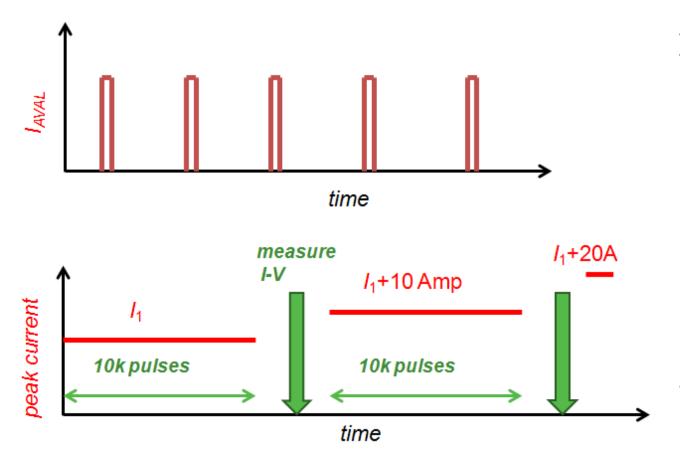

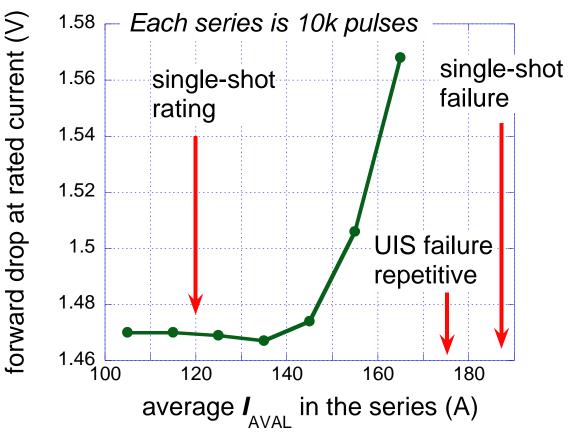

## Avalanche capability for SiC

### SiC devices in very strong in avalanche

- Avalanche energy scales well with die area

ON 900V SiC MosFET –  $20m\Omega$

In hybrid setup SiC SBD can project Si IGBTs from voltage overshots.

For SiC FETs less overvoltage margin required

ON

## Diode avalanche robustness

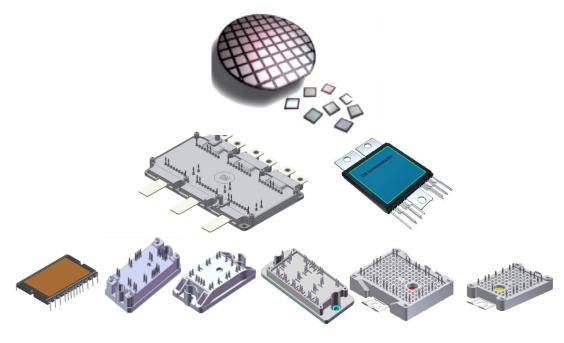

# **ON SiC Vertical Integration**

emiconductor®

# Summary

- Silicon carbide product ramp-up accelerated due high MosFET demand

- Multiple package and module setups are available/under rollout

- SiC devices can replace Si Diodes, SuperJunction MosFETS and IGBTs

- Challenges:

- SiC stress in discrete and module packages can be solved

- GOX integrity failure modes can be screened well

- Large SiC chips vs Yield still inhibitive

- Epitaxy, dicing improvements in conjunction with equipment supplier

- Robustness

- SiC allows extreme transient dvdt and didt failure modes can be screened well

- SiC surge, short circuit and avalanche

- SiC needs vertical integration for cost, quality and supply

**ON Semiconductor**

# **Thank You**

any questions:

thomas.neyer@onsemi.com