# Meeting Industry Requirements for GaN Device Reliability

Tim McDonald Infineon Technologies

> MARCH 17-21 | ANAHEIM, CA. ANAHEIM CONVENTION CENTER

PEC

Copyright © Infineon Technologies AG 2019. All rights reserved.

# Agenda

1

2

3

4

## GaN and Silicon structures

Qualification model for Infineon CoolGaN™

Key failure mechanism and degradation models

# Agenda

## GaN and Silicon structures

2

3

4

1

Qualification model for Infineon CoolGaN™

Key failure mechanism and degradation models

## Why it is important to talk about GaN Quality and Reliability?

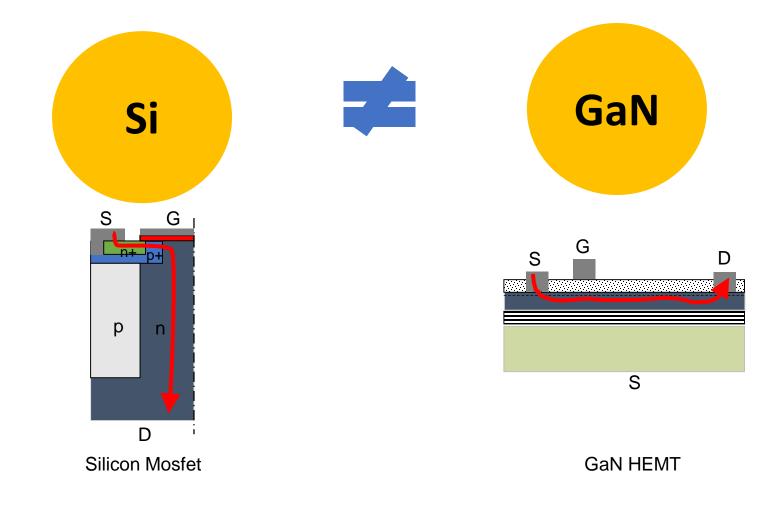

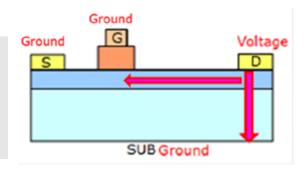

• GaN HEMT structure is different in many aspects from Silicon MOSFET

# Product qualification standard Stress Tests, based on JEDEC JESD47

JEDEC applies ~9 different procedures based on Stress type, Conditions, Duration and Sample size

| Stress                                                      | Conditions                                          | Duration | Sample Size                     |

|-------------------------------------------------------------|-----------------------------------------------------|----------|---------------------------------|

| Temperature Cycling<br>JESD22 A104                          | With PC <sup>*</sup> ,<br>-55 °C / +150 °C          | 1000x    | 3 lots x 77 pcs                 |

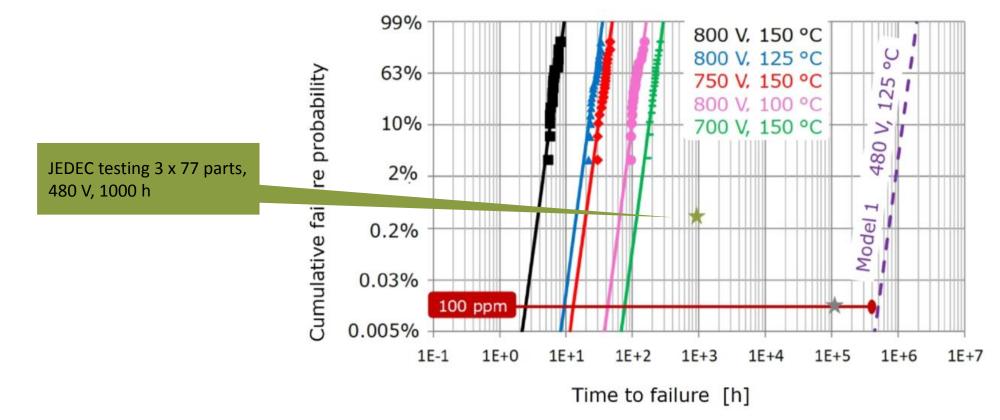

| High Temperature Reverse Bias<br>JESD22 A-108               | With PC <sup>*</sup> ,<br>150 °C / 600 V            | 1000 h   | 3 x 77                          |

| High Temperature Storage Live<br>JESD22 A-103               | With PC <sup>*</sup> ,<br>150 °C                    | 1000 h   | 3 x 45                          |

| Positive High Temperature Gate Stress<br>JESD22 A-108       | With PC <sup>*</sup> ,<br>150 °C / 50 mA            | 1000 h   | 3 x 77                          |

| Negative High Temperature Gate Stress<br>JESD22 A-108       | With PC <sup>*</sup> ,<br>150 °C / -10 V            | 1000 h   | 3 x 77                          |

| High Humidity High Temperature Reverse Bias<br>JESD22 A-101 | With PC <sup>*</sup> ,<br>85 °C / 85 % r.h. / 100 V | 1000 h   | 3 x 77                          |

| Intermittent Operational Life Test<br>MIL-STD 750/Meth.1037 | With PC*,<br>ΔT = 100 K                             | 15,000x  | 3 x 77                          |

| ESD-HBM<br>JS-001                                           | Without PC                                          | -        | 1 lot x 3 pcs per voltage level |

| ESD-CDM<br>JS-002                                           | Without PC                                          | -        | 1 lot x 3 pcs per voltage level |

\*: Preconditioning acc. JEDEC-MSL3

Though many or most of these also apply to GaN devices, this cannot be considered as a sufficient list for consideration to qualify GaN devices!

### Qualification method must address the device/structure specific failure modes of GaN Si MOSFET

Existing qual plan addresses mature Si technology/structure

#### **GaN HEMT**

New Structure: what tests will stress them? Standards yet to be defined

Agenda

### GaN and Silicon structures

2

3

4

1

Qualification model for Infineon CoolGaN™

Key failure mechanism and degradation models

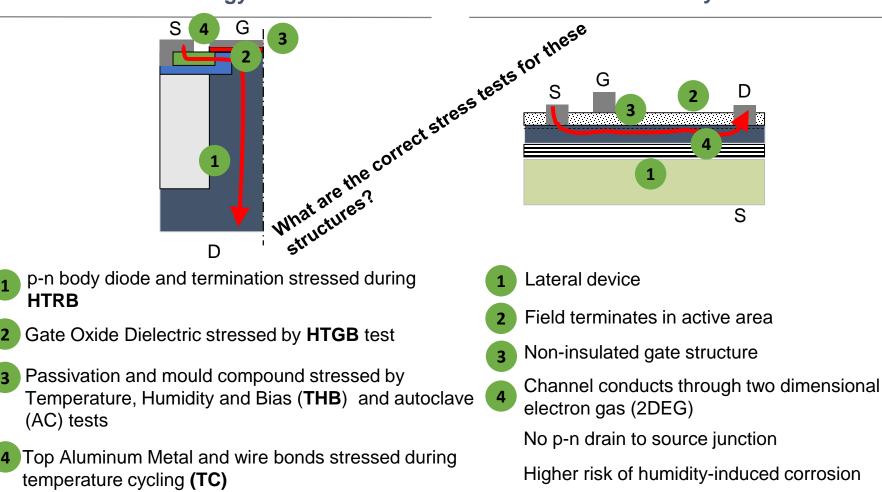

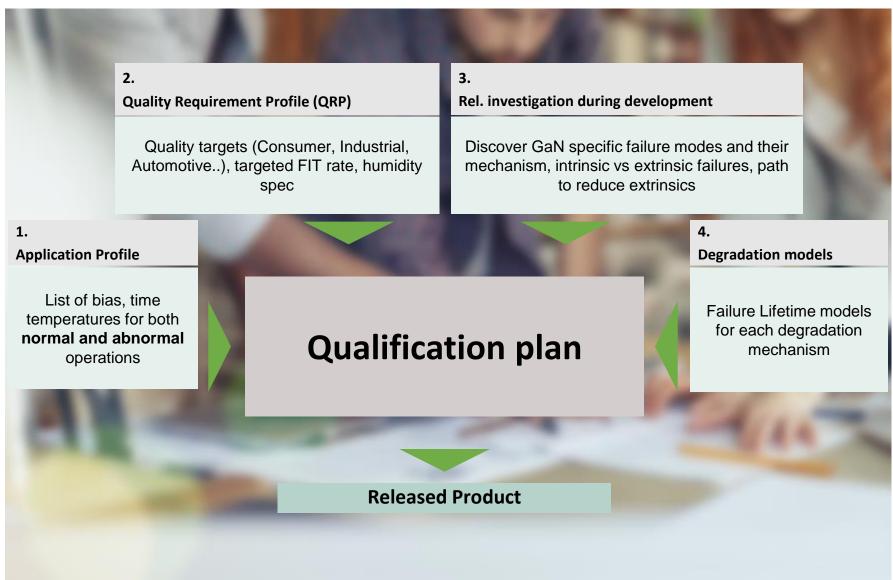

### How did Infineon determine a new qualification plan for 600 V CoolGaN™?

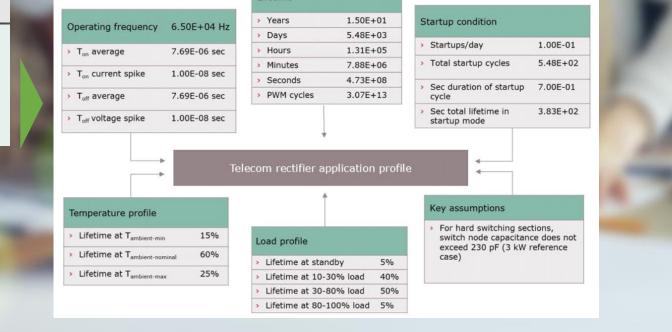

## 1. Application Profile

- Application lifetime

- Operating hours by mode

- > Currents, voltages and temperatures at different load conditions

Lifetime

- > Time of abnormal use conditions within lifetime

- Currents/voltages at peak and spikes during switching

| 1.          |         |

|-------------|---------|

| Application | Profile |

List of bias, time temperatures for both **normal and abnormal** operations

## 2. Quality Requirement Profile

#### 2.

**Quality Requirement Profile (QRP)**

Displays the development targets (Consumer/Industrial, FIT rates, Humidity specs,...) of a new technology or product in what concerns its reliability, performance and target applications

- General definition of the target

- 2 Definition of the product components

- 3 Maximum operation voltages and currents

- Operation temperature range

- 5 Electro Static Discharge classification

- Moisture Sensitivity Level class definition

- 7 Lifetime targets and failure rates for device, dielectrics and metallization

- > Drift limits parameter definition:

- V<sub>th</sub>

- Drain leakage

- R<sub>on</sub>

- Time to failure

6

0

## 3. Reliability investigations during development

#### 3.

Rel. investigation during development

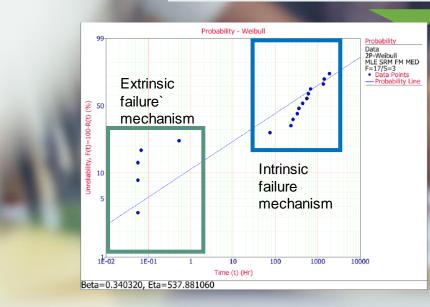

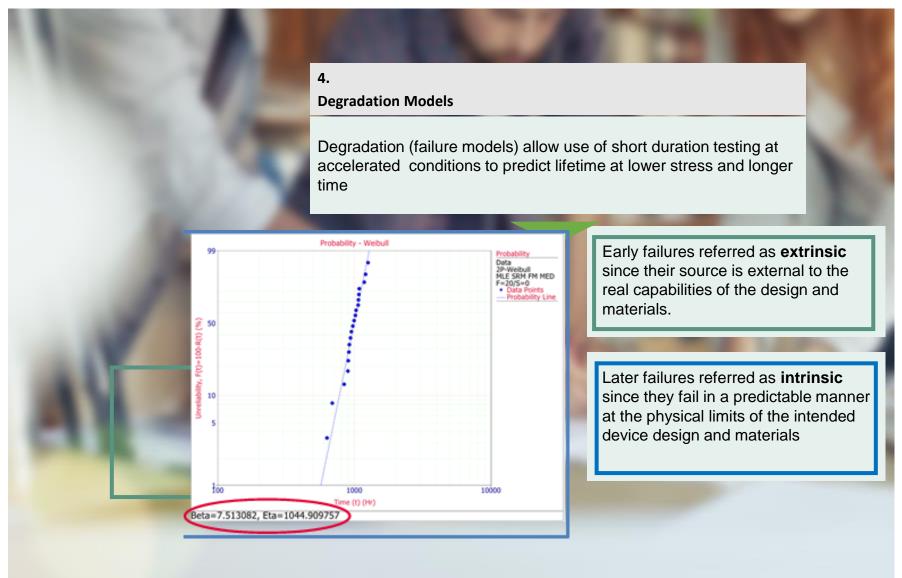

Reliability investigations during development aims to discover *intrinsic and extrinsic failure mechanisms*

**Purpose**: find path of process, design or test changes to <u>minimize</u> <u>occurence of extrinsic failures</u>

Early failures referred as **extrinsic** since their source is external to the real capabilities of the design and materials.

Later failures referred as **intrinsic** since they fail in a predictable manner at the physical limits of the intended device design and materials

## 4. Degradation models for predicting reliability/lifetime

# Agenda

## GaN and Silicon structures

4

1

Qualification model for Infineon CoolGaN™

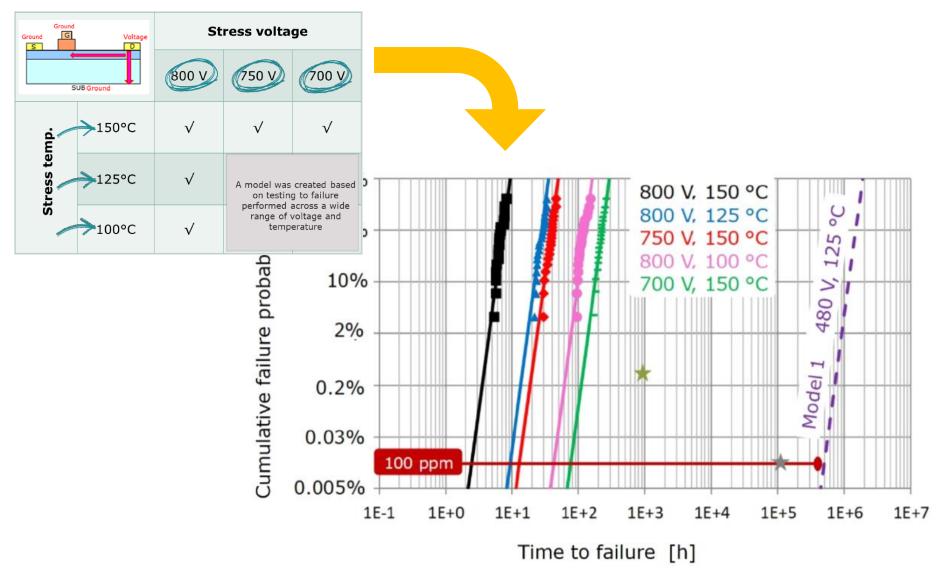

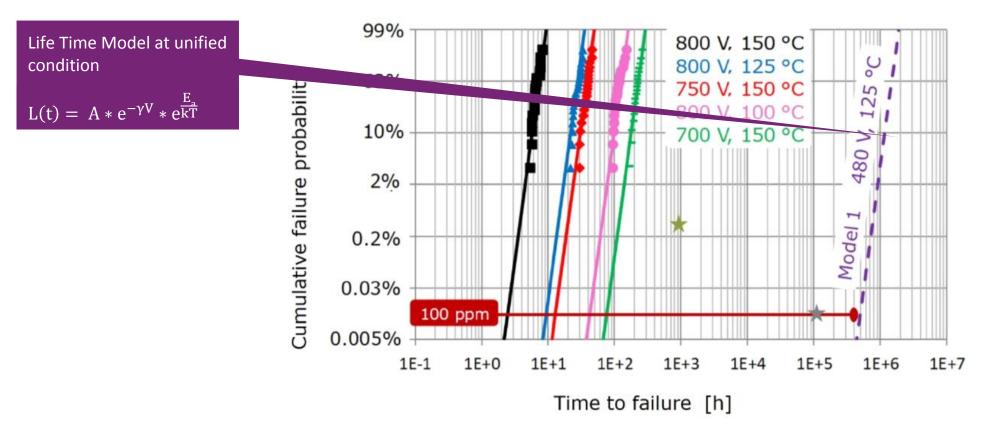

## DC Bias Failure: TDDB

#### TDDB:

#### Time Dependent Dielectric Breakdown

Polar molecules lead to asymmetrical lattice distortion when subject to electric fields

Chemical bonds strain will break over time generating failure

#### Silicon

- Silicon-Silicon structure are not subject to TDDB

- Silicon-SiO2 and Si-other polar materials are subject to TDDB

#### GaN

GaN is highly polar in nature, then subject to TDDB

Degradation of Silicon devices responds almost only to

Temperature

GaN devices respond strongly and primarily to temperature and **applied bias** (accelerated voltage stress testing required)

Copyright © Infineon Technologies AG 2019. All rights reserved.

Copyright © Infineon Technologies AG 2019. All rights reserved.

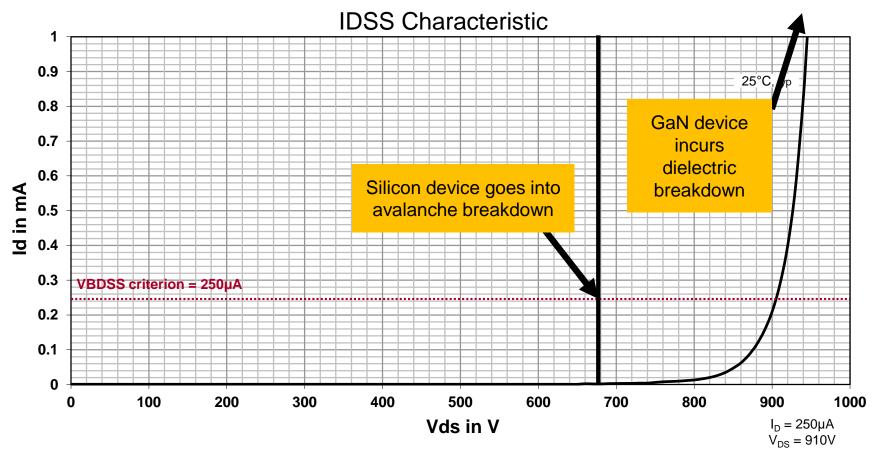

# GaN Device breakdown at higher voltage than Si MOSFET but mechanism is different

- > GaN can withstand much higher voltage stress than silicon

- ...but lifetime at such high voltage is limited

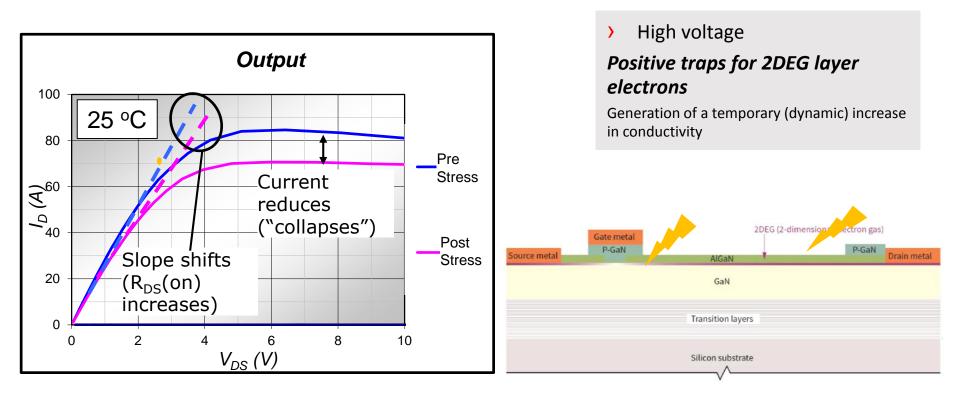

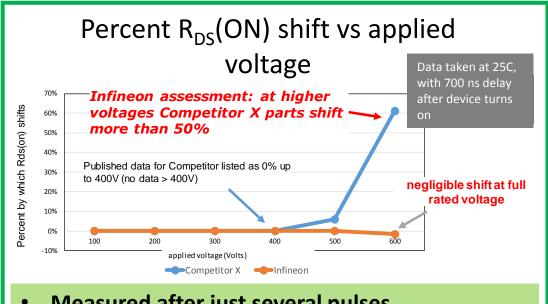

# Dynamic Rdson

- > Post application of DC bias Stress, RDS(ON) shifts (increases) and peak output current reduces.

- > This phenomenon is attributed to surface states and trapping in the device

- > The result is an unstable increase in conduction losses than can change in time (device could fail).

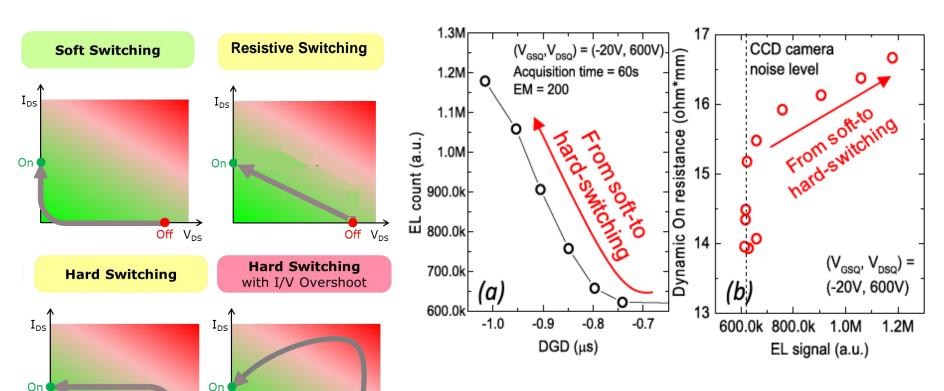

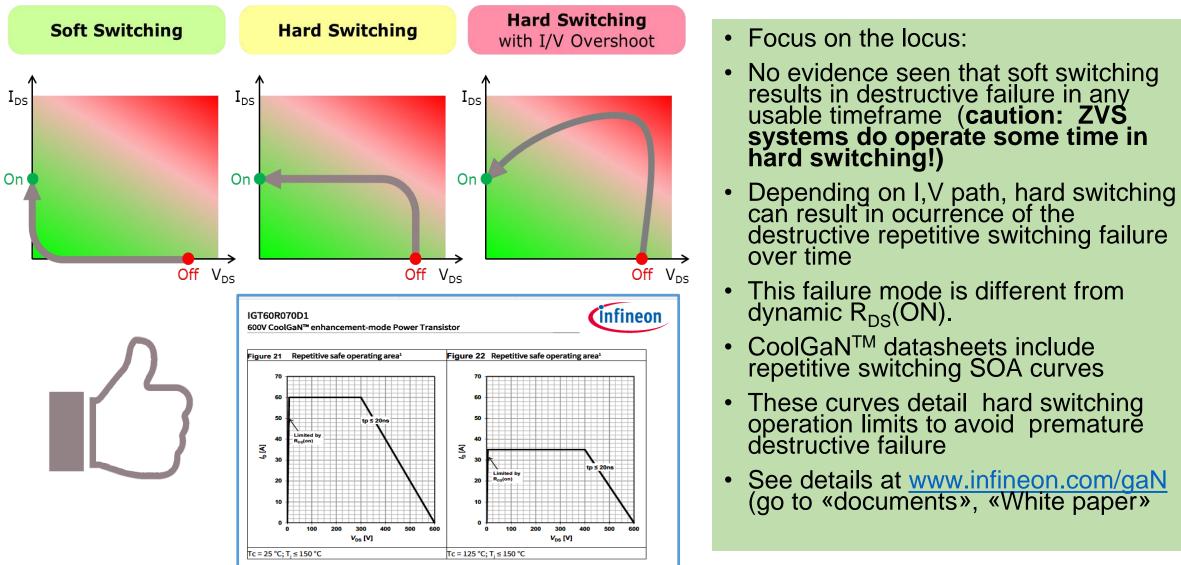

# Dynamic R<sub>ds</sub>ON shift increases with degree of hard switching : focus on the I,V locus

Off V<sub>DS</sub>

From: I. Rossetto et al, "Evidence of Hot Electron Effects During Hard Switching of AlGaN/GaN HEMTs", IEEE Transactions on Electron Devices, Vol. 64, No, 9, September 2017

- Dynamic RDS(ON)

increases with

Electro luminescence (EL)

count –(proxy for hot

electrons)

- Electro-luminescence increases with degree of hard switching (Higher peak I,V point)

- Worst case Dynamic RDS(ON) occurs in hard switching (inductive load)

Off V<sub>DS</sub>

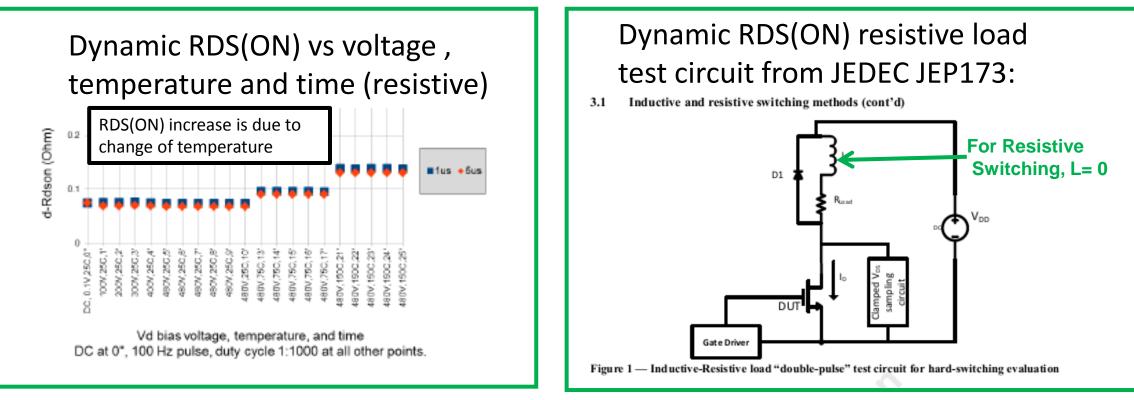

# 600V CoolGaN<sup>™</sup> technology reliability dynamic R<sub>DS</sub>ON over time – Very low in resistive load condition

Tested over voltage (from 100 to 480V) and temperature (from 25C to 150C)

RDS(ON) measured 1 and 5 microseconds after voltage stress ends

Stress held at 5 minutesTotal test duration = 1 hour and 40 minutes, little to no increase: resistive switching is not highest stress condition

## 600V CoolGaN<sup>™</sup> dynamic R<sub>DS</sub>(ON) – also very low in (worst case) inductive hard switching out to 600V

- Testing ramped voltage (from 100 to 600V)

- More hot electrons produced during hard switching at high simultaneous I,V (eg: inductive load)

- Most stressful test condition for dynamic  $R_{DS}(ON)$ . ٠

- Measured after just several pulses. •

- Hard switching (inductive) is strongest stress

- Infineon: 100% tested at 700V, 700 nsec delay

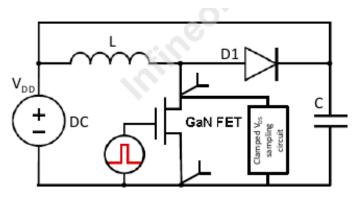

Dynamic  $R_{DS}(ON)$  inductive load boost test circuit from JEDEC JEP173:

Figure 2 — Depiction of the hard-switching "double-pulse" test circuit (showing its similarity to a boost converter)

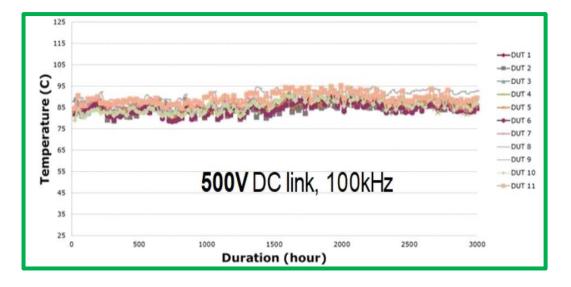

## What about reliability of hard switching over time?

- 11 devices tested under boost (inductive load) hard switching topology

- 3,000 Hrs operation without evidence of increased power dissipation

- No evidence of shifting RDS(ON)

- Is this test sufficient?

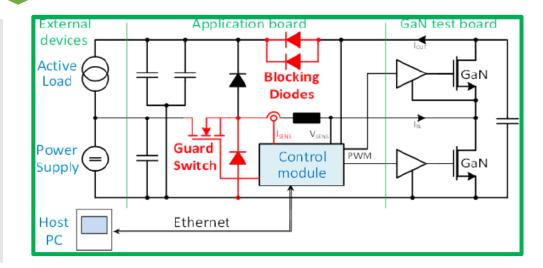

- Infineon created an accelerated test vehicle

- Switching up to 700V (vs use at ~410V)

- High current and elevated temperature

- Switching related failures do occur at accelerated conditions: need for a model to predict useful life

## Results of repetitive switching-SOA (D-HTOL) degradation model

Copyright © Infineon Technologies AG 2019. All rights reserved.

# Agenda

## GaN and Silicon structures

3

4

1

Qualification model for Infineon CoolGaN™

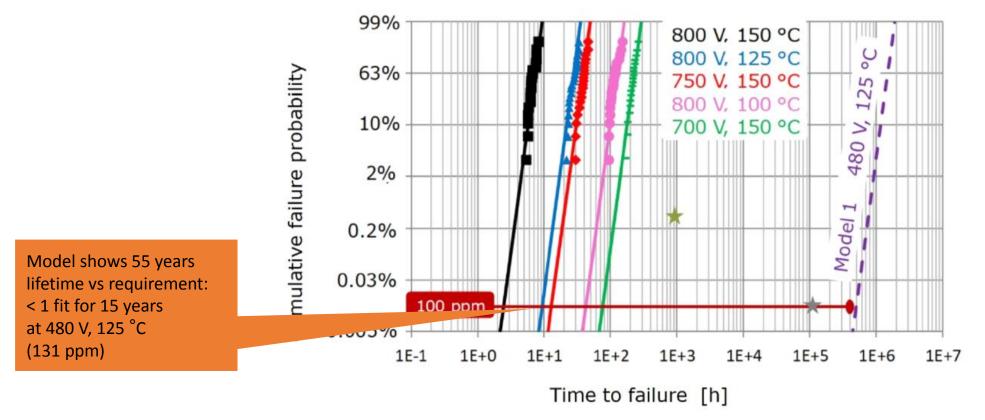

- GaN Devices have different material and device structure compared to silicon superjunction transistors; there is a need for a different qualification and reliability evaluation criteria

- Infineon has completed an application specific qualification with 4 elements which uses Telecom rectifier base station as the initial application (can be used to cover a wide variety of applications)

- There are failure modes which occur in GaN but not in silicon. Important among these is DC Bias and repetitive switching SOA. Infineon has developed models which ensure robust operation in targeted applications

- Full info available at : www.Infineon.com/gan

## Thank you!

This work is the result of the efforts of many colleagues. Thanks are due to:

Oliver Haeberlen, Gerhard Prechtl, Olaf Schmeckebier, Marco Silvestri, Alain Charles, Deepak Veereddy, Thomas Detzel, Michael Glavonics, Mohamed Imam, Andrea Merello.