# Wide Bandgap Quality and Reliability Standards: JEDEC Delivers!

Tim McDonald, JEDEC JC-70 Chair, JC-70.1 Vice Chair Stephanie Watts Butler, founding past Chair JC-70, IEC TC47 WG 8 co-convenor

#### With contributions from:

Peter Friedrichs, Infineon, JC-70.2 Vice Chair, IEC TC47 WG 8 co-convenor Kurt Smith, VisIC, JEDEC JC-70.1 Chair Jeffrey Casady, Wolfspeed, JEDEC JC-70.2 Chair

IS21.2 APEC 2022, Houston, TX

### **Outline**

- Introduction: what's all this about wide bandgap and JC-70?

- Is JC-70 making an impact?

- Growing JC-70 membership

- Quickening the document creation process

- Influencing Industry and research

- Collaborating for wider impact

- What's next? Document Roadmaps

- Example topic from current efforts: Dynamic Capacitive losses

- Key Takeaways

### Introduction: What's all this about wide bandgap and JC-70?

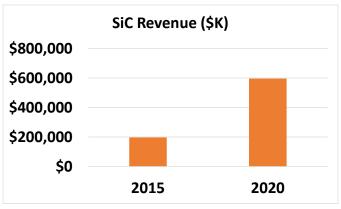

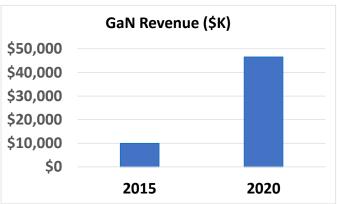

- IN 2015, at the genesis to form JC-70, SiC and GaN were known as fast growth market opportunities

- GaN has grown ~4.5x in revenue and SiC by ~3x based on revenue estimates from Yole's 2015 and 2021 reports.

- JC-70 has helped accelerate adoption into the new applications forming these markets

# JC-70 Structure: Wide Bandgap (GaN & SiC)

JC-70 Wide Bandgap Power Electronic Conversion Semiconductors

JC-70.1 Subcommittee

<u>GaN</u> Power Electronic Conversion

Semiconductor Standards

JC-70.2 Subcommittee

<u>SiC</u> Power Electronic Conversion

Semiconductor Standards

### JEDEC Committee JC-70.1 Task Group structure (GaN)

Global Standards for the Microelectronics Industry

Task Group TG701\_1

GaN Power Electronic Conversion

Semiconductor Reliability and

Qualification Procedures

JC-70.1 Subcommittee

GaN Power Electronic

Conversion

Semiconductor

Standards

Task Group TG701\_2

GaN Power Electronic Conversion

Semiconductor Datasheet

Elements and Parameters

Task Group TG701\_3

GaN Power Electronic Conversion

Semiconductor Test and

Characterization Methods

### JEDEC Committee JC-70.2 (SiC) Task Group Structure

Global Standards for the Microelectronics Industry

Task Group TG702\_1

SiC Power Electronic Conversion

Semiconductor Reliability and

Qualification Procedures

JC-70.2 Subcommittee

SiC Power Electronic

Conversion

Semiconductor

Standards

Task Group TG702\_2

SiC Power Electronic Conversion

Semiconductor Datasheet

Elements and Parameters

Task Group TG702\_3

SiC Power Electronic Conversion

Semiconductor Test and

Characterization Methods

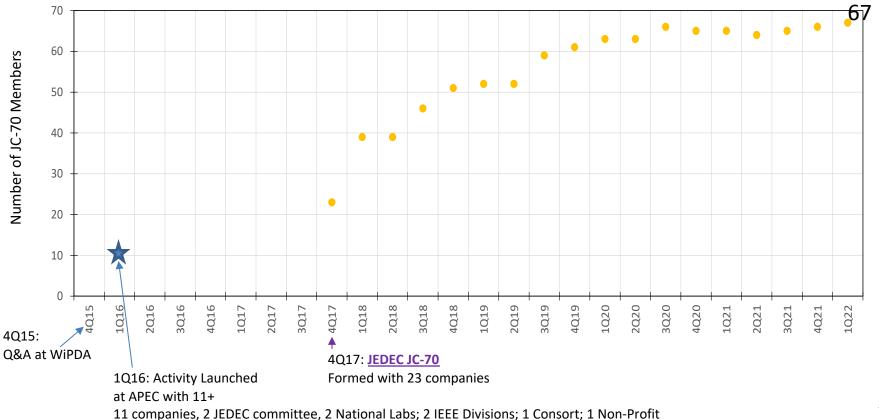

## JC-70 Membership 3rd Largest and Fastest Growing JEDEC Committee

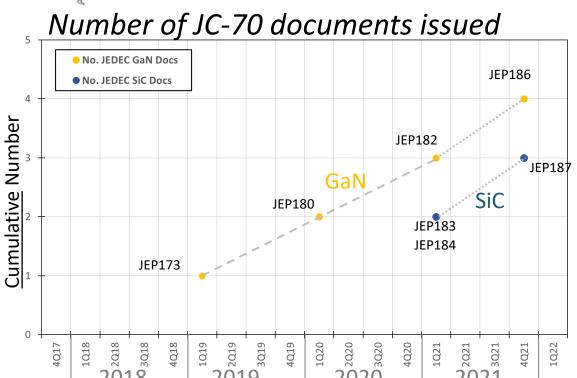

## Increasing speed of JC-70

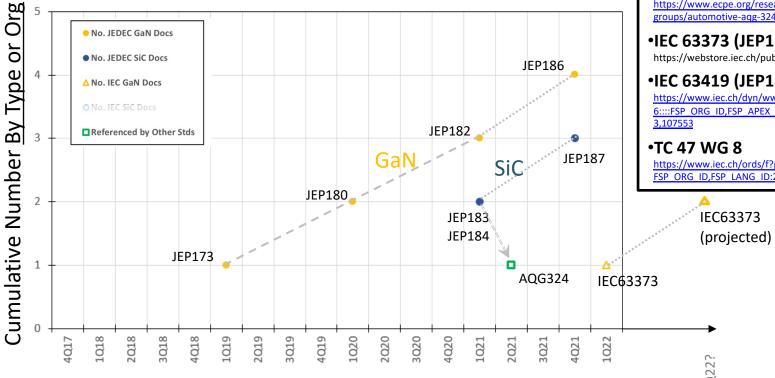

## Increasing productivity of JC-70 with organizations across the world

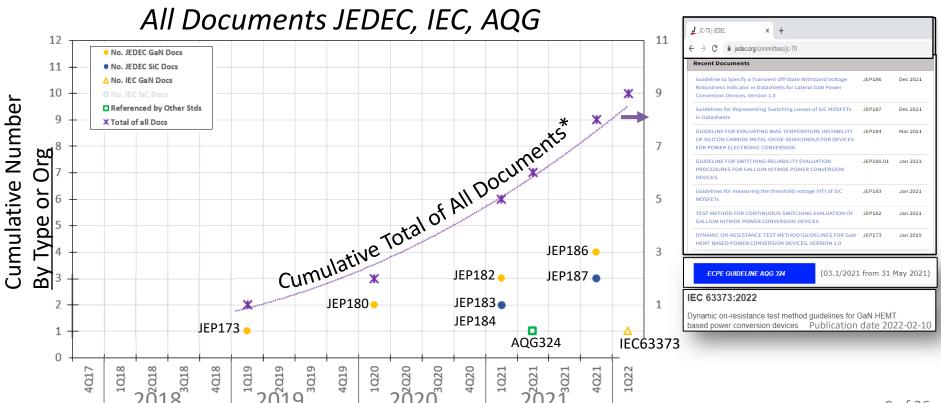

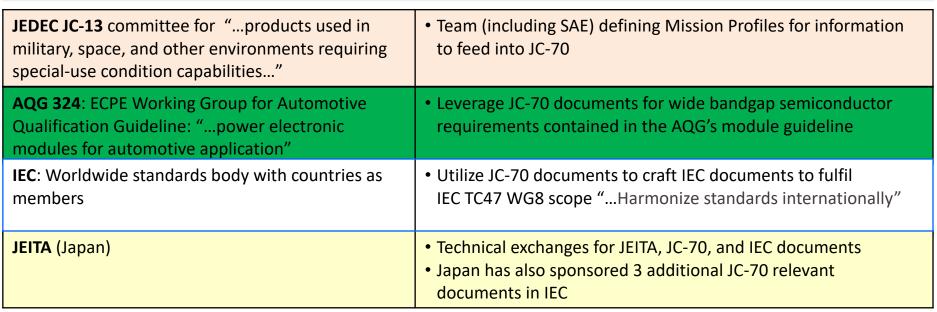

## JC-70 Collaborative Work & Engagement Models

Different organizations

- Different Timings

- Different Purposes

- Different Engagement Models

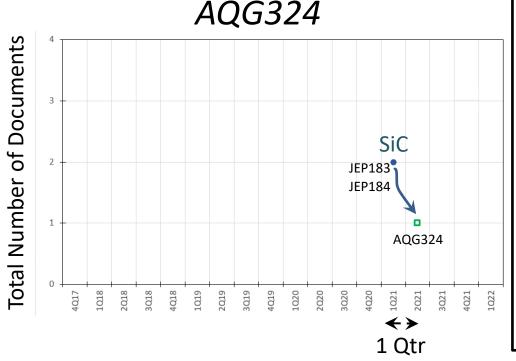

## Collaborating quickly

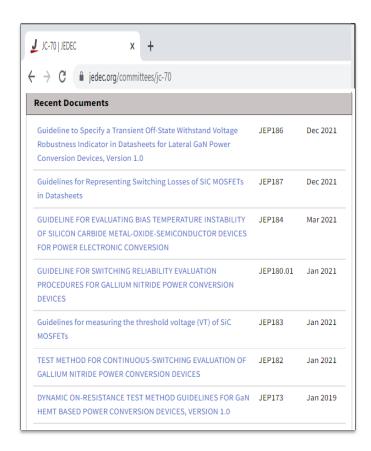

- JEP183 and JEP184 are required references in AQG324

- Active exchanges and leverage company membership in both Orgs

- From AQG324 Scope: "Future releases of the AGQ 324 Guideline will address further wide bandgap power semiconductors (e.g. GaN),"

- AQG324: https://www.ecpe.org/research/workin

g-groups/automotive-agg-324/

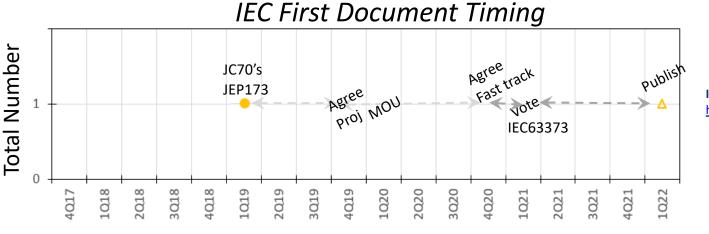

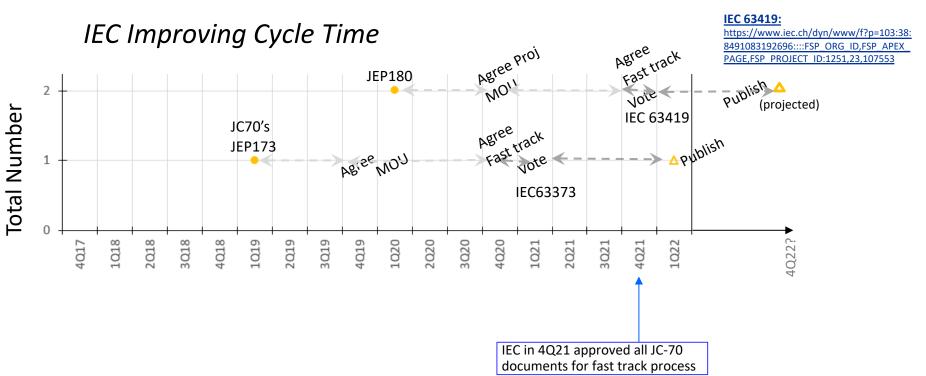

## Harmonizing effectively

- IEC deploys a formal staged process

- Includes vote to agree for project

- MOU if existing document from another org

- (and several more phases if not fast tracked)

- Vote on document

- (and additional votes if required technical content revisions)

IEC 63373: https://webstore.iec.ch/publication/68515

## Harmonizing efficiently

## **Demonstrating increasingly** efficient and effective engagement with organizations across the world

https://www.jedec.org/committees/jc-70

#### •AQG324 (JEP183, JEP184):

https://www.ecpe.org/research/workinggroups/automotive-agg-324/

#### •IEC 63373 (JEP173):

https://webstore.iec.ch/publication/68515

#### •IEC 63419 (JEP180):

https://www.iec.ch/dyn/www/f?p=103:38:849108319269 6::::FSP ORG ID,FSP APEX PAGE,FSP PROJECT ID:1251,2

https://www.iec.ch/ords/f?p=103:14:500507554697761:::: FSP ORG ID.FSP LANG ID:27401.25

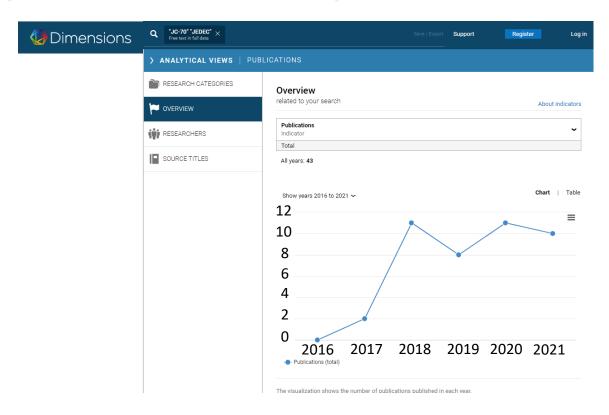

## The scholarly literature are recognizing JC-70: 43 publications reference (JC-70 AND JEDEC)

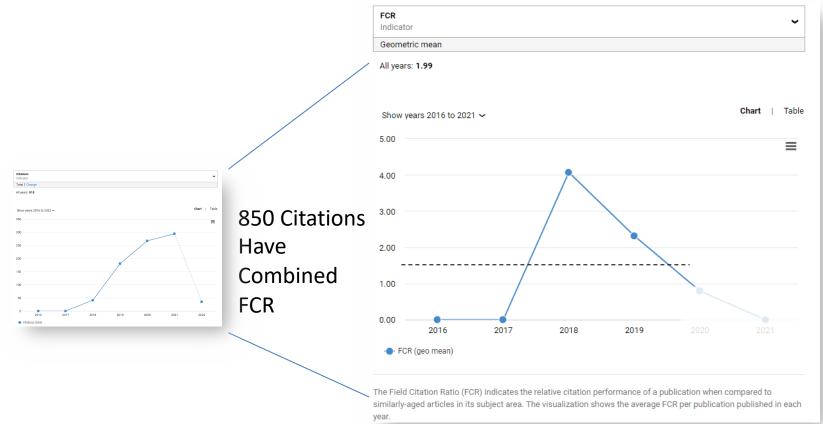

## Impact seen in publications: Citations to articles which reference (JC-70 AND JEDEC)

## Referencing (JC-70 AND JEDEC) publications as a group have ABOVE average (citation) impact

#### Field Citation Ratio (FCR)

The Field Citation Ratio (FCR) indicates the relative citation performance of a publication when compared to similarly-aged articles in its subject area. A value of more than 1.0-1.5 indicates higher than average citation, when defined by FoR subject code, and publication year. The FCR is calculated for all publications in Dimensions which are at least 2 years old...

## Status from APEC 2020

## Proposed Items for GaN Guidelines/Standards

#### **REL**

- JEP122-like catalog of Failure Mechanisms/Mode (summarizing literature)

- Offstate voltage/Temp Rel (ALT-HTRB)

- ✓ Switching Reliability

- Stress Procedures

& Acceleration

- Continue to Add to list of Failure Mechanisms

#### **Test**

- ✓ Dynamic  $R_{DS}(ON)$

- Switching reliability test methods

#### **Datasheet**

- Include effect of Dynamic R<sub>DS</sub>(ON)

- GaN power transistors specific voltage ratings

- Transistor circuit symbol to reflect distinctive operation GaN HEMTs

Caution: Work in Progress

Caution: Work in Progress

• Transient Voltage Aspects

## Proposed Items for GaN Guidelines/Standards

## Status for APEC 2022

#### **REL**

Stress

- JEP122-like catalog of Failure Mechanisms/Mode:

-TDB, Charge trapping, Switching

- ✓ Switching Reliability

- Reverse Bias stress procedure guideline

- Transient Reliability Topic

- Stress Procedures& Acceleration

- Continue to Add to list of Failure Mechanisms

#### **Test**

- ✓ Dynamic R<sub>DS</sub>(ON)

- ✓ Switching Reliability test methods

- Dynamic capacitive loss

- Thermal Characterization

- Test for effective R<sub>DS</sub>(ON) drift

- Test for surge capability

- Test for maximum V<sub>DS(tr)</sub>

#### **Datasheet**

✓ Transient Voltage Rating

Caution: Work in Progress

Items in Green with check mark: document completed, with no check mark: document in progress, black text: planned for consideration as future work

## Proposed Items focus for SiC Guidelines/Standards

Status for APEC 2020

#### Liaisons between Task Groups to be fine tuned

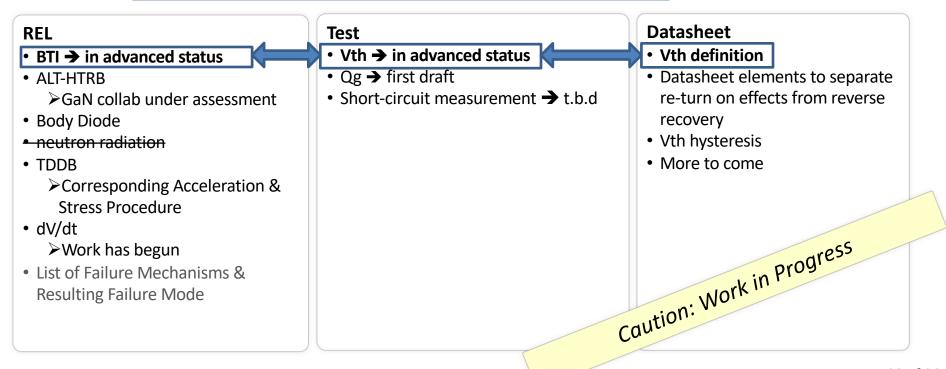

### Proposed Items for SiC Guidelines/Standards

#### Status for **APEC 2022**

#### REL

- **Evaluating BTI**

- ALT-HTRB

- Gate Oxide Reliability and Robustness **Fvaluation**

- SiC stress procedures

- SiC qual procedures

- Power Cycling

- Failure Mechanism and Models:

- dV/dt Events

- HV Switching instability

- Gate Switching Instability

- Bipolar Instability

- HTRB

- Application Level Switching Instability

#### **Test**

- Vth measurement

- **Qg** Measurement

- Body Diode-reverse recovery test

- Eon/Eoff- double pulse set up

- Avalanche Breakdown

- Short-circuit measurement

- S-parameter measurement

- Dynamic capacitive loss (with 701 3)

#### **Datasheet**

- Parasitic Turn on (status?)

- Bipolar and capacitive charges in SiC devices

- Representing switching losses in SiC MOSFFT datasheets

Caution: Work in Progress Items in Green with check mark: document completed, with no check mark: document in progress, black text: planned for consideration as future work

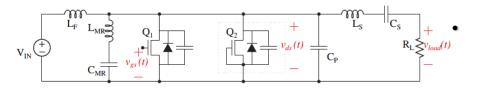

## Current topic: Dynamic Capacitive Losses

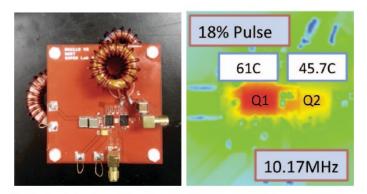

**Fig. 3:** A  $\Phi_2$  inverter with two transistors.

(a) A  $\Phi_2$  inverter tuned (b) Thermal image of this with at 10.17MHz. inverter at 18% pulse.

Efficiency was measured 5-10% lower than expected in GaN based high frequency (Φ-2 topology) converters

- f = 3-30 MHz (beyond range of commercialized applications today)

- Adding a second GaN HEMT (Q2) in diode mode (G to S shorted) unexpectedly adds to losses

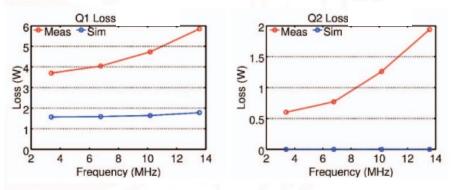

K. Surakitbovorn and J. Rivas Davila, "Evaluation of GaN Transistor Losses at MHz Frequencies in Soft Switching Converters" COMPEL 2017

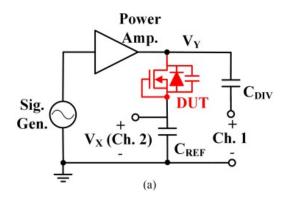

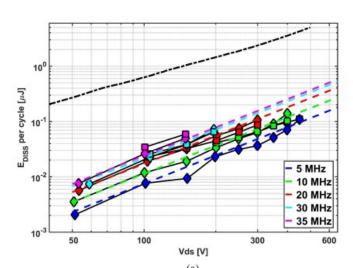

## Measuring Dynamic Capacitive Losses

- For isolating energy lost due to dynamic hysteresis of device capacitance, several measurement methods have been investigated (shown is Tower-Sawyer circuit)

- Unexpected increase in energy dissipated (E<sub>DISS</sub> on curve shown) during switching

- Increases with both frequency  $(f^{1.6})$  and voltage

- Not just C<sub>OSS</sub> (recoverable energy)

- Topic is on the roadmap for test method task groups from both 70.1 (GaN) and 70.2 (SiC)

Zulauf, G., et al, "COSS Losses in 600 V GaN Power Semiconductors in Soft-Switched, High- and Very-High-Frequency Power Converters", IEEE IEEE Transactions on Power Electronics, Vol. 33, No. 12, December 2018

## **Key Takeaways**

- JC-70 is getting it done:

- Accelerating document production

- Influencing the user community

Collaborating to maximize impact

Come join us!

## How to Join

- Interested companies worldwide are welcome to join JEDEC to participate in this important standardization effort.

- Find more information about membership

- https://www.jedec.org/join-jedec

- or contact <u>Emily Desjardins</u> to learn more

- emilyd@jedec.org

Global Standards for the Microelectronics Industry

## Acknowledgments

- JEDEC Staff

- Mikhail Guz, JEDEC Secretary to JC-70, Consultant, IP and Technology Experts

- JC-70.1 chair and vice chair (Kurt Smith and Tim McDonald) and Task Group Leaders:

TG701 1 (REL) Co-Chairs:

- Ron Barr (Transphorm)

- Sandeep Bahl (TI)

- Sameh Khalil (Infineon)

TG701\_2 (Datasheet) Co-Chairs

- Peter Di Maso (GaNSystems)

- Nick Fichtenbaum (Navitas)

TG701 3 (Test) Co-Chairs:

- Deepak Veereddy (Infineon)

- Jaume Roig (ON)

• JC-70.2 chair and vice chair (Jeff Casady and Peter Friedrichs) and Task Group Leaders:

TG702 1 (REL) Co-Chairs:

- Don Gajewski (Wolfspeed)

- Thomas Aichinger (Infineon)

TG702\_2 (Datasheet) Co-Chairs

- Christian Mueller (Infineon)

- Alexander Bolotnikov (ON Semi)

TG702\_3 (Test) Co-Chairs:

- Ryo Takeda (Keysight)

- Christian Strenger (Infineon)

- Entire Membership of JC-70, JC-70.1, and JC-70.2 and their Task Groups

- The University and National Lab Community