# Getting the most performance out of the latest generation SiC cascode FETs

## Pete Losee (UnitedSiC is now) Qorvo

## Outline

- SiC cascode introduction

- Gen 4 SiC FETs set new performance benchmarks

- Design examples with new 750V SiC FETs, TPPFC, LLC

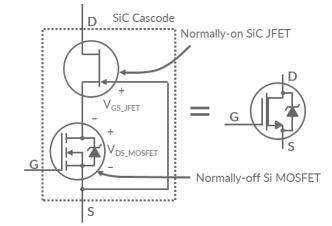

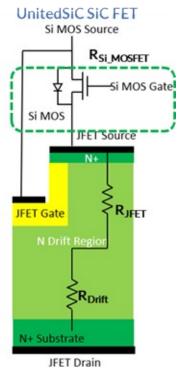

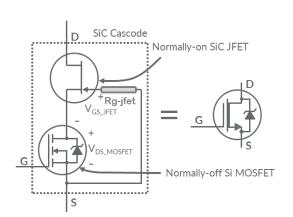

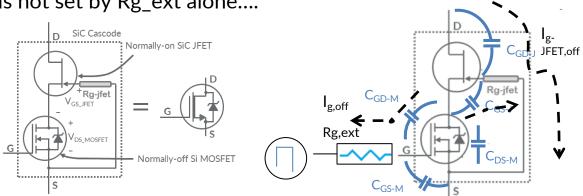

## SiC cascode FET

- Cascode is a source-switched SiC JFET

- Inverse of the MOSFET drain-source voltage across the JFET gate-source

- Blocks forward current when MOSFET gate is off

- JFET is fully on with its  $V_{GS}\thickapprox 0$

- When MOSFET is on

- When reverse current flows, regardless of MOSFET gate voltage

- Low voltage (20-30V) Si MOSFET Rds is <10% of the JFET resistance

- Lowest R<sub>On</sub> x A

- Compatible with Si or SiC gate drive, 0-12V, 0-15V etc. drive,  $V_{th}$ =5V

- Reduced die size, low E<sub>oss</sub>, C<sub>oss</sub>

- Excellent integral diode with low V<sub>F</sub> (1.0-1.5V typical) and low Q<sub>rr</sub>

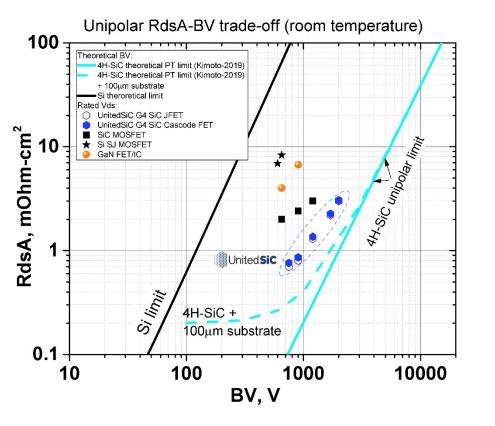

## Qorvo/UnitedSiC technology approaching "unipolar limit"

#### Gen 4 JFETs

- Trench structure with reduced cell pitch

- Optimized drift/spreading layers

- Reduced substrate

thickness

750V SiC JFET:  $R_{On,sp} = 0.7mOhm-cm^2$

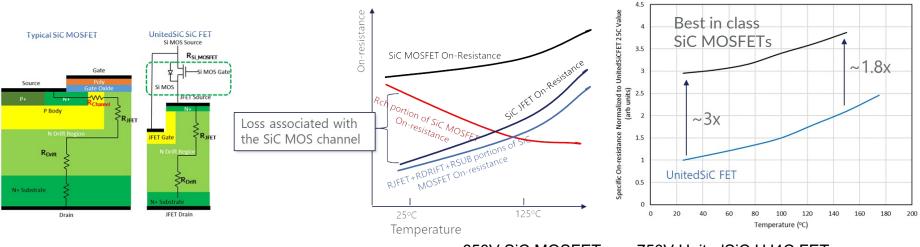

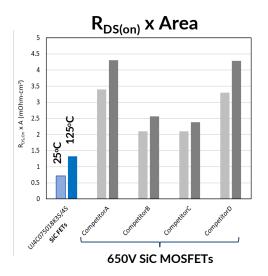

# Gen 4 750V SiC FETs Best in class $R_{On,sp}$ across temperature

650V SiC MOSFETs vs. 750V UnitedSiC UJ4C FETs

- Gen 4 FETs exhibit stronger positive temperature coefficient (TC) vs. SiC MOSFET competitors but offer lower R<sub>DS,On</sub> per unit area across useful temperature range

- Smaller SiC die size for given on-resistance -> Lower Q<sub>oss</sub>

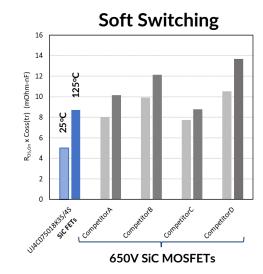

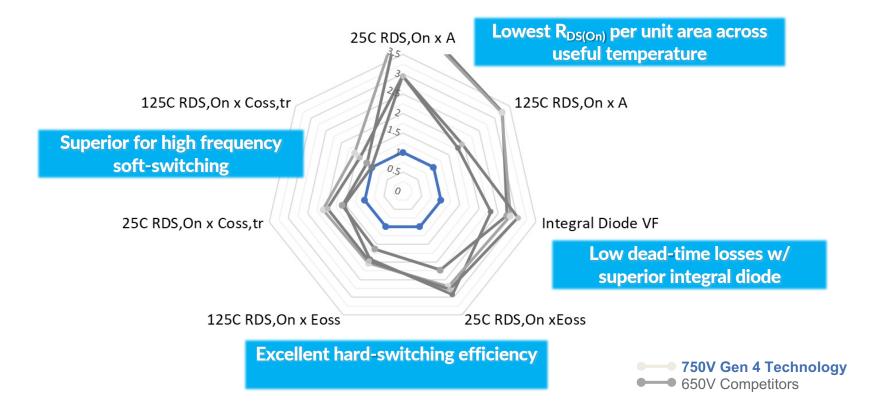

## Gen 4 750V SiC FETs - Figures of Merit

#### Benefit

Lowest conduction losses across useful temperature range, for a given footprint or package type

#### Hard Switching 800 700 600 R<sub>Ds,on</sub> x Eoss (mOhm-uJ) 125°C 500 400 25°C 300 200 100 UNCOTO SCIENS CompetitorA . Petitor® PetitorC ompetitorD 650V SiC MOSFETs

- Benefit

- Lowest total E<sub>oss</sub> / Q<sub>oss</sub> x R<sub>DS(on)</sub> FoM

- Nearly 2X better than competitors

#### Benefit

- Maintaining low R<sub>DS(on)</sub> x C<sub>oss,tr</sub> enables higher power density in soft-switched applications

- + **5-10X** lower gate drive losses by  $Q_g x V_{Drive}$

- Excellent body diode enables reliable operation out of resonance

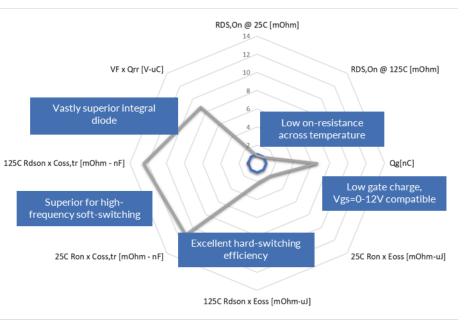

## Gen 4 SiC FETs - Industry's best Figures of Merit

## Gen 4 750V SiC FETs vs Si superjunction

IS11.6

| Specification                       | Fast Diode SJ | SJ Best-in-class | UJ4C075018K4S |

|-------------------------------------|---------------|------------------|---------------|

| Irated_Tc100 [A]                    | 64            | 62               | 60            |

| Voltage Rating [V]                  | 600           | 650              | 750           |

| RDS,On @ 25C<br>[mOhm]              | 15.0          | 17               | 18            |

| RDS,On @ 125C<br>[mOhm]             | 29.0          | 33.5             | 31            |

| Tj,max [C]                          | 150.0         | 150              | 175           |

| Rth,j-c(max)[C/W]                   | 0.3           | 0.28             | 0.39          |

| Qg[nC]                              | 251           | 215              | 38            |

| Qrr [nC]                            | 1560          | 20000            | 102           |

| VFSD@25C[V]                         | 1.0           | 0.9              | 1.7           |

| 125C Rdson x Eoss<br>[mOhm-uJ]      | 826.5         | 911.2            | 372.0         |

| 125C Rdson x Coss,tr<br>[mOhm - nF] | 108.2         | 111.2            | 8.7           |

| VF x Qrr [V-uC]                     | 1.6           | 18               | 0.18          |

Normalized to UJ4C075018K4S parameters (smaller is better for each)

650V Competitors

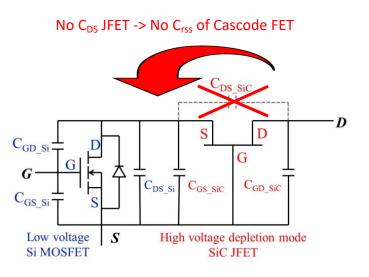

## SiC cascode FET: Low C<sub>rss</sub>

Good for fast switching, low losses, immune to dv/dt induced shoot through in bridge circuits....

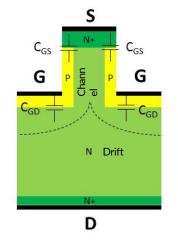

SiC Vertical JFET is "0"  $C_{DS}$ structure, formed with PN Junctions from G-S and G-D JFET:  $C_{GS}$  and  $C_{GD}$

## SiC cascode FET: Low C<sub>rss</sub>

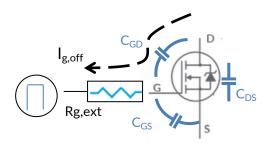

But turn-off is not set by Rg\_ext alone....

Turn-Off Voltage Transition of Conventional MOSFET

$V_{\rm g}$  in plateau region

$I_{g,off} = I_{C,GD} \alpha C_{GD} dV_D/dt$

$I_{g,off}$  varied easily via:

$[\mathsf{V}_{\mathsf{g},\mathsf{plateau}} - \mathsf{V}_{\mathsf{g},\mathsf{off}}\,] \; / \; \mathsf{R}_{\mathsf{g},\mathsf{ext}}$

In Cascode,  $R_{g,ext}$  alone does not limit the turn-off voltage transition dV/dt..... voltage transition is <u>also dictated by ( $I_{g-JFET}$ )</u> Rg-jfet once JFET Vgs is in its plateau region... this is built into JFET.

Small RsCs or Cs device snubbers are **EFFECTIVE** method to manage fast switching waveforms, minimize delay times and maintain low switching losses

See "Minimizing EMI and Switching Loss for SiC FETs" at www.unitedsic.com

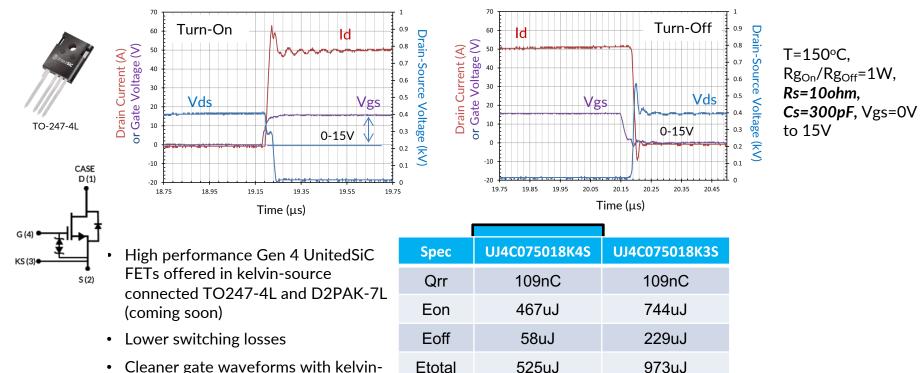

#### Gen 4 SiC FETs in kelvin-source packages

Cleaner gate waveforms with kelvin-• source connected packages

E<sub>snub</sub> = 10-12uJ at 50A/400V switching with Rg=10hm

Etotal

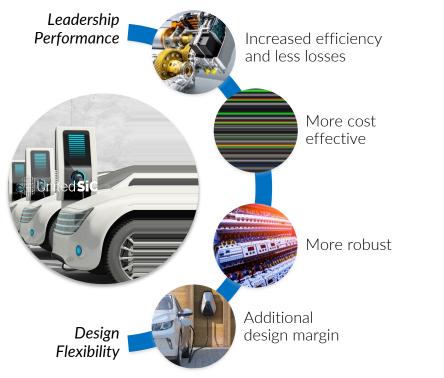

# SiC: More applications, more design considerations

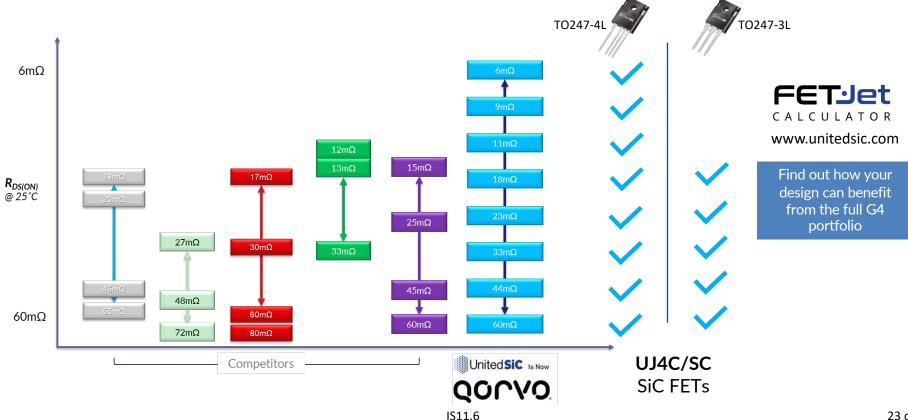

### **UJ4C/SC** 750V SiC FET Series

## SiC FET options enable more design flexibility

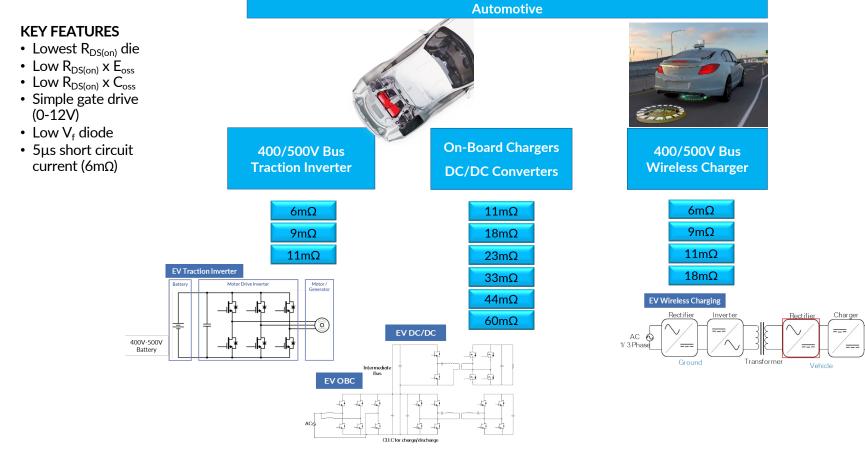

#### Gen 4 SiC FETs - Design Flexibility in Automotive

Output

## Design Flexibility in IT infrastructure

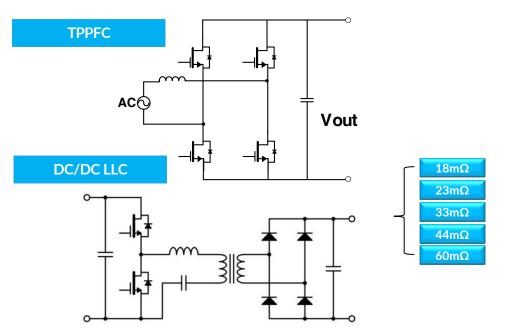

Power Factor Correction DC/DC Converters

#### **KEY FEATURES**

- + Low  $R_{DS(on)} \times E_{oss}$

- Low R<sub>DS(on)</sub> x C<sub>oss</sub>

Simple gate drive

- Simple gate drive (0-12V)

- $\bullet \ Low \ V_f \ diode$

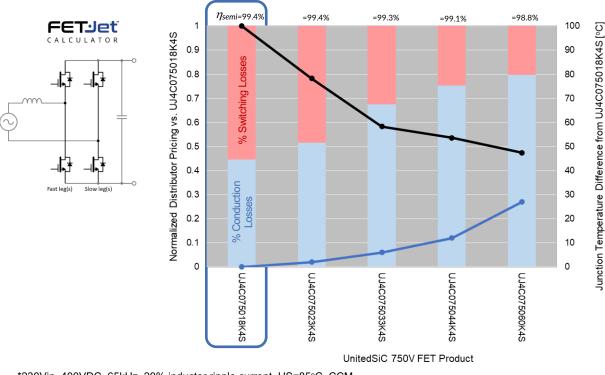

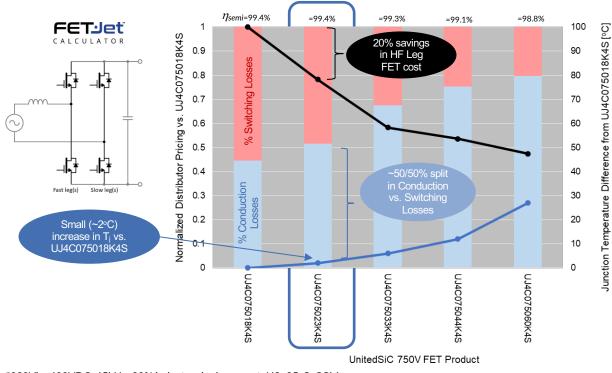

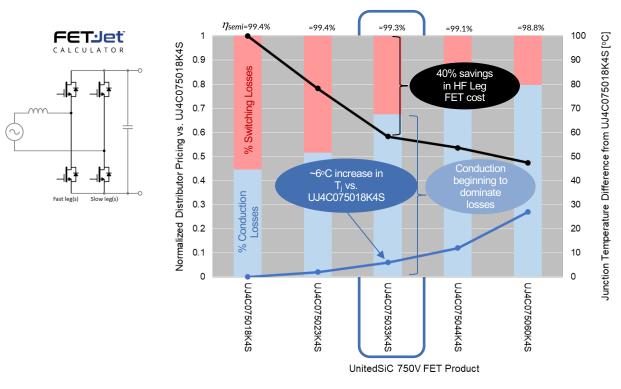

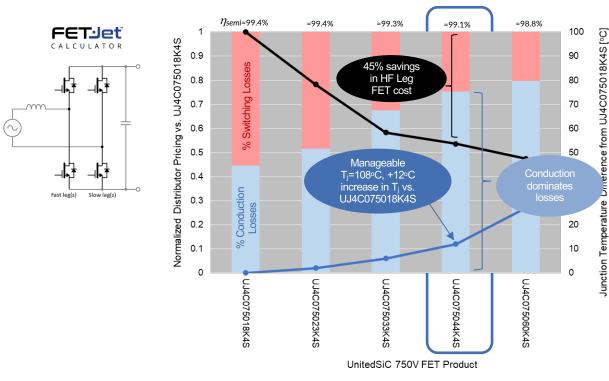

#### UJ4C075018K4S:

- Highest performance at full and 50%-load, semiconductor efficiency = 99.4%

- Low Rthjc + Low Losses yield a low temperature rise, T<sub>i</sub>=96°C @ full load

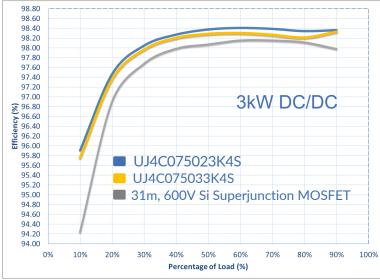

#### UJ4C075023K4S:

- Excellent Cost/Performance tradeoff

- Low R<sub>thjc</sub> + Low Losses yield a low temperature rise, T<sub>i</sub>=98°C @ full load

#### UJ4C075033K4S:

- Excellent Cost/Performance tradeoff

- Good performance, semiconductor efficiency 99.3%

- Conduction dominates losses at full load, 67%

#### UJ4C075044K4S:

- Good choice where partialload efficiency is important, 99.1% @ 3.6kW, 99.4% @ 1.5kW

- Conduction dominates losses at full load, 75%

- +12°C Tj compared to UJ4C075018K4S

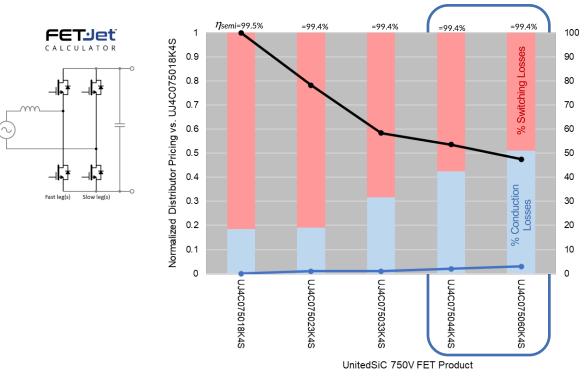

#### UJ4C0750<u>44</u>K4S & UJ4C0750<u>60</u>K4S

Difference from UJ4C075018K4S [°C]

Junction Temp

Offer Excellent Options at 1.5kW:

- Comparable semiconductor efficiency (99.4%) as the lower on-resistance parts, despite ~47-53% of FET cost

- Balanced conduction & switching losses with low T<sub>j</sub> rise (93°C, within 3°C of UJ4C075018K4S)

Full portfolio offers designers new choices allowing better system optimization

### Flexibility in TPPFC

Efficiency at Vin 230Vac

Optimize Full-Load

Efficiency

--2X UJ4C075018K4S

3000

2X UJ4C075023K4S

3500

---

---

2500

100.0

99.8

99.6

99.4

99.2

99.0

98.8

98.6

98.4

98.2

98.0

97.8

97.6

0

Efficiency: Percentage

Optimal cost-

performance

mid load

efficiency

solution for light-

**Optimize Cost-**

Performance

500

Value

1000

1500

• DC/DC Converters

2000

Pout: (W)

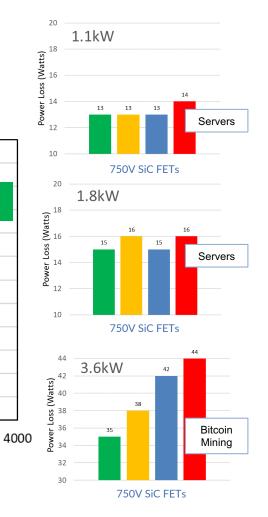

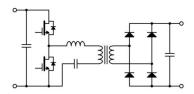

### Flexibility in LLC

#### SiC FET vs. Si Superjunction

- Power Factor Correction

- DC/DC Converters

#### Drop-in replacement results

750V SiC FETs

## SiC FET options enable more design flexibility

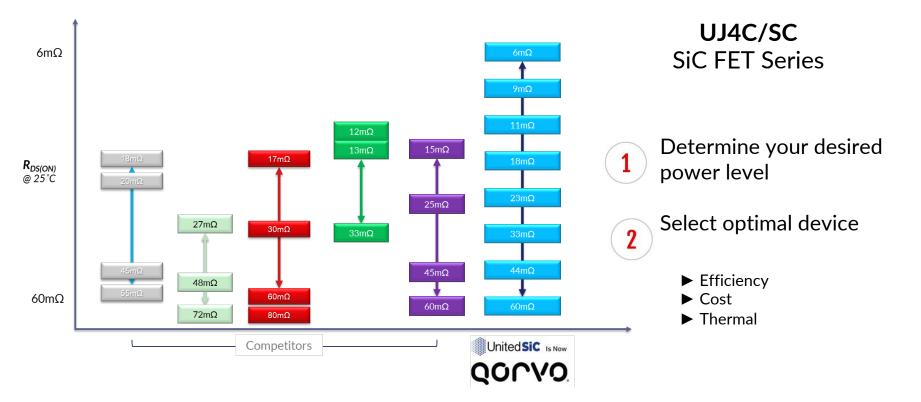

# Summary

- SiC Cascode FETs offer the lowest RDSON switches in 650V+ class

- Gen 4 750V SiC FETs are excellent options for hard, soft-switched applications

- Broad portfolio from 6mohm 60mohm allow designers to select best system cost-performance in front end rectifier and dc-dc converters