**Electronics**

#### Heraeus

#### ADVANCED INTERCONNECTION TECHNOLOGIES IN POWER ELECTRONICS FOR IMPROVED RELIABILITY AND PERFORMANCE

PSMA Packaging Industry Session, APEC 2022 Aarief Syed-Khaja, Habib Mustain

### CONTENT

#### HERAEUS GROUP

- > Heraeus A globally Successful portfolio company

- > Heraeus Business Portfolio

- > Heraeus Electronics

#### CHALLENGE PERFORMANCE

- DTS<sup>®</sup>, sintering and Cu bonding technology for increased lifetime and current/power density

- > Si<sub>3</sub>N<sub>4</sub> AMBs for enhanced heat dissipation and reliability

# 2 HERAEUS AND CHALLENGE OF NEW PACKAGING SOLUTIONS

#### CHALLENGE QUALITY AND YIELDS

- > DTS for reduced production complexity

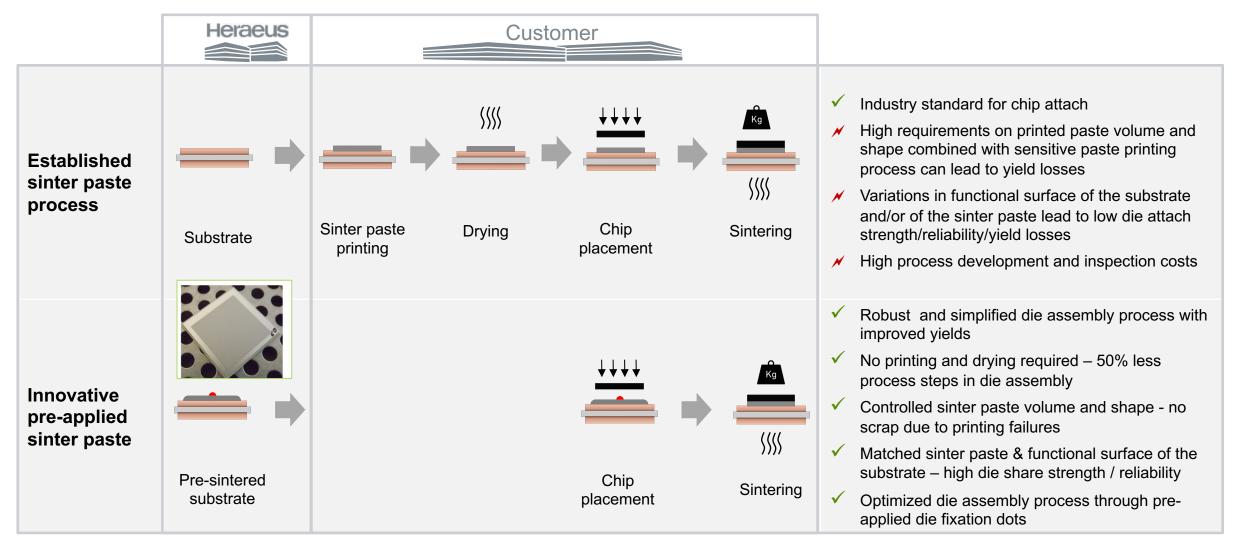

- Pre-applied sinter paste for reduced complexity and improved yields

### GLOBALLY SUCCESSFUL PORTFOLIO COMPANY

Advanced Interconnect Technologies in Power Electronics | Heraeus Electronics | PSMA Packaging Industry Session

#### **BUSINESS PORTFOLIO – LEADING IN GLOBAL MARKETS**

Advanced Interconnect Technologies in Power Electronics | Heraeus Electronics | PSMA Packaging Industry Session

#### PROVIDING MATERIALS TO THE ELECTRONICS INDUSTRY FOR MORE THAN 60 YEARS

| Roll Clad Strips<br>for electrical<br>contacts                  | Precision Stamped Parts<br>(Leadframes) and<br>Bonding Wires                                                        | Launch of<br>mAgic <sup>®</sup> Sinter Paste | Formation of<br>Global Business Unit<br>Heraeus Electronics<br>and Launch of DCB | Launch of Welco AP5112<br>for SiP Application               | Launch of AMB<br>Production  |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------|

| 1960 1970                                                       | 1980 1990                                                                                                           | 2000                                         | 2010                                                                             |                                                             | 2020                         |

| Development of<br>Thick Film Materials<br>for hybrid technology | <ul> <li>&gt; Solder Paste</li> <li>&gt; SMT Adhesiv</li> <li>&gt; Bondable Ro</li> <li>&gt; Solder Powd</li> </ul> | ve<br>II Clad Strips                         | Solder Wire<br>and Paste for<br>Die Attach* Die                                  | Launch of the first<br>Material System<br>Top System (DTS®) | Launch<br>of AgCoat<br>Prime |

|                                                                 |                                                                                                                     |                                              | *established at Umicore in<br>1990s, acquired in 2009                            | n                                                           |                              |

Advanced Interconnect Technologies in Power Electronics | Heraeus Electronics | PSMA Packaging Industry Session

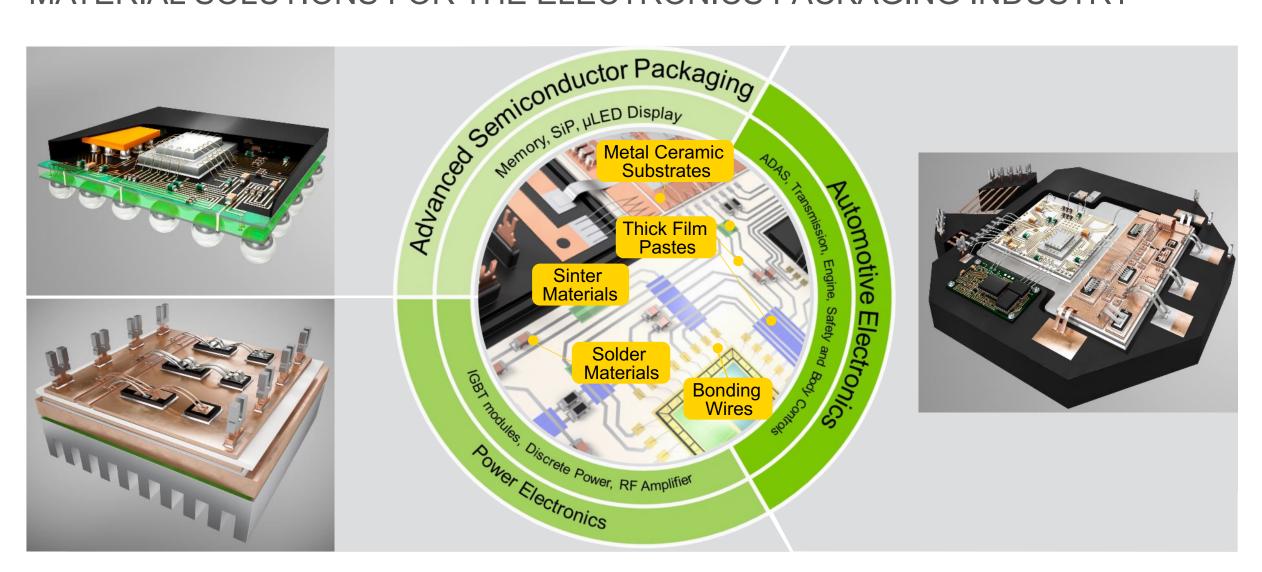

#### MATERIAL SOLUTIONS FOR THE ELECTRONICS PACKAGING INDUSTRY

### CONTENT

#### HERAEUS GROUP

- > Heraeus A globally Successful portfolio company

- > Heraeus Business Portfolio

- > Heraeus Electronics

#### CHALLENGE PERFORMANCE

- DTS<sup>®</sup>, sintering and Cu bonding technology for increased lifetime and current/power density

- > Si<sub>3</sub>N<sub>4</sub> AMBs for enhanced heat dissipation and reliability

2 HERAEUS AND CHALLENGE OF NEW PACKAGING SOLUTIONS

#### CHALLENGE QUALITY AND YIELDS

- > DTS for reduced production complexity

- Pre-applied sinter paste for reduced complexity and improved yields

**Electronics**

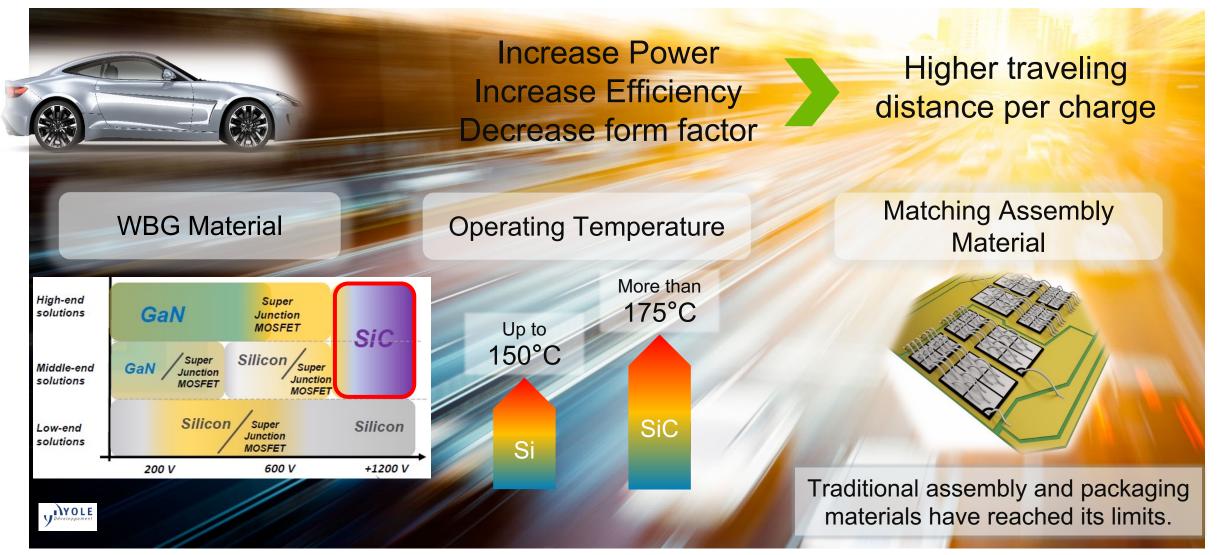

#### **REVOLUTION OF POWER ELECTRONICS PACKAGING**

Advanced Interconnect Technologies in Power Electronics | Heraeus Electronics | PSMA Packaging Industry Session

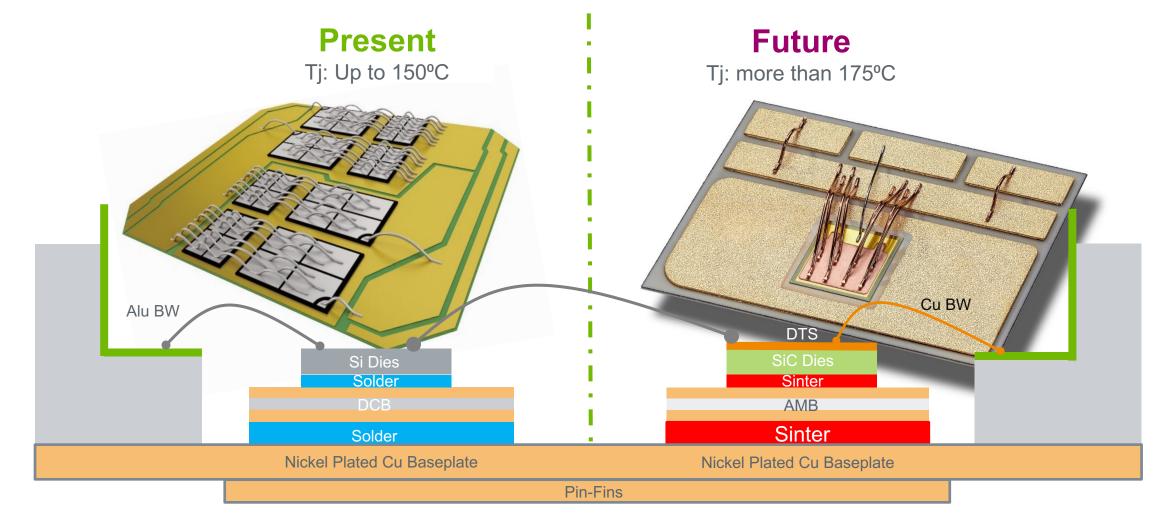

### **REVOLUTION OF POWER ELECTRONICS PACKAGING** TRANSITION TO HIGH POWER DENSITY MODULE PACKAGING

### POWER SEMICONDUCTORS AND NEED FOR NEW PACKAGING MATERIALS SOLUTIONS

#### **Benefit through smaller dies**

- > Reduction of chip size / cost

- > Lower losses / higher efficiency

- > Increase of power & current density per chip

#### **Packaging challenges**

- > Increased power loss per chip area requires materials with better heat dissipation

- > More power needs better current carrying capability of packaging materials

- > Increased operating temperatures and **reliability** challenges

Source: Innovative Material Packaging Solutions for superior Power Electronics Devices, EDPC Conference Nov. 2016, Nürnberg, A. Miric, Dr. Frank Osterwald, P. Dietrich, A.S. Klein, A. Hinrich

200 C

175°C

150°C

25°C

25°C

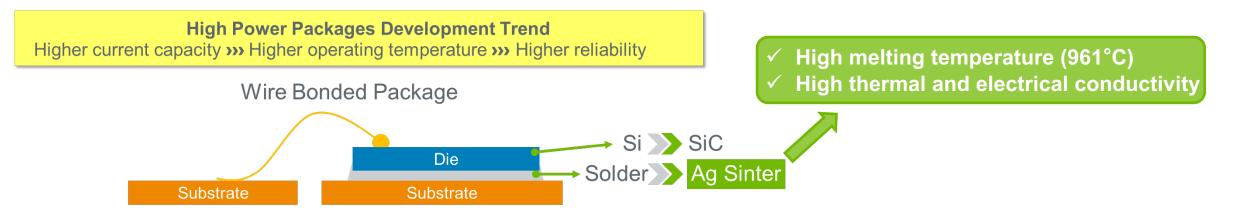

#### WHY SINTERING?

Integration of new materials and technologies with increase in reliability **?**

| Die Attach Materials           | Lead-free solder<br>Sn <sub>96.5</sub> Ag <sub>3.5</sub> | High-lead solder<br>Pb <sub>92.5</sub> Sn <sub>5</sub> Ag <sub>2.5</sub> | Silver sinter |

|--------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------|---------------|

| Max. operation temp.<br>(°C)   | 220                                                      | 296                                                                      | > 380         |

| Thermal conductivity<br>(W/mK) | 60                                                       | 25                                                                       | > 150         |

| Electrical conductivity (MS/m) | 8                                                        | 5                                                                        | 40            |

| CTE (ppmK <sup>-1</sup> )      | 25                                                       | 29                                                                       | 20            |

| Youngʻs modulus<br>(kN/mm²)    | 30                                                       | 23.5                                                                     | 40-55         |

1. Peiner, Die Attach Using Pressure-Assisted Sintering for High-Temperature Applications, Braunschweig, University of Technology Germany 2013

Advanced Interconnect Technologies in Power Electronics | Heraeus Electronics | PSMA Packaging Industry Session

#### **PRESSURE SINTER PASTE PROCESS & APPLICATION**

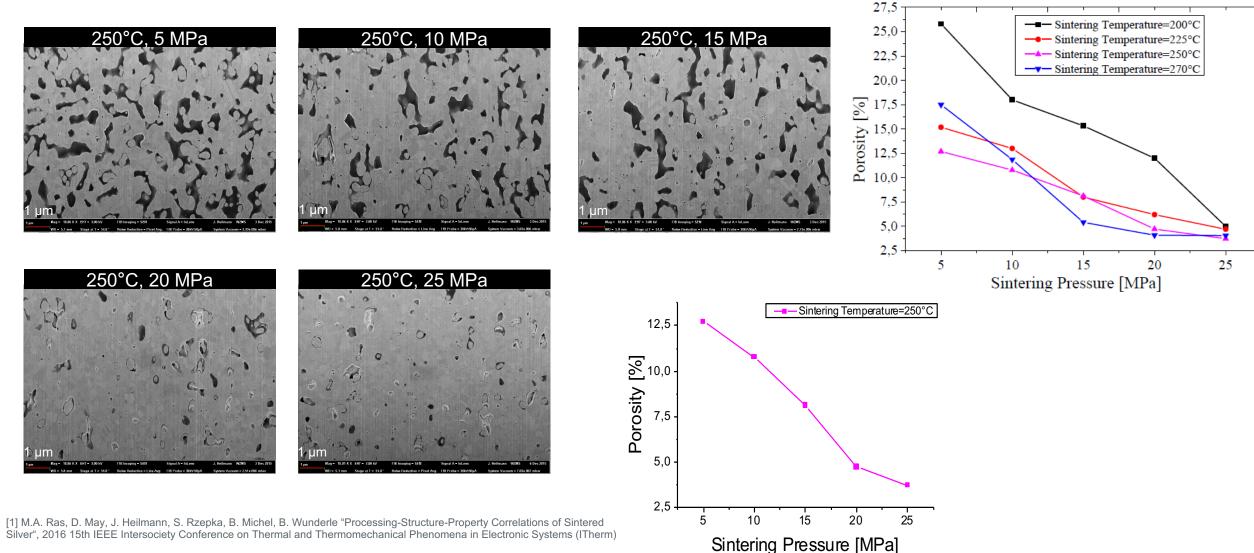

#### POROSITY AS FUNCTION OF SINTERING PRESSURE

Porosity as a function of sintering parameters

Silver", 2016 15th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm)

Advanced Interconnect Technologies in Power Electronics | Heraeus Electronics | PSMA Packaging Industry Session

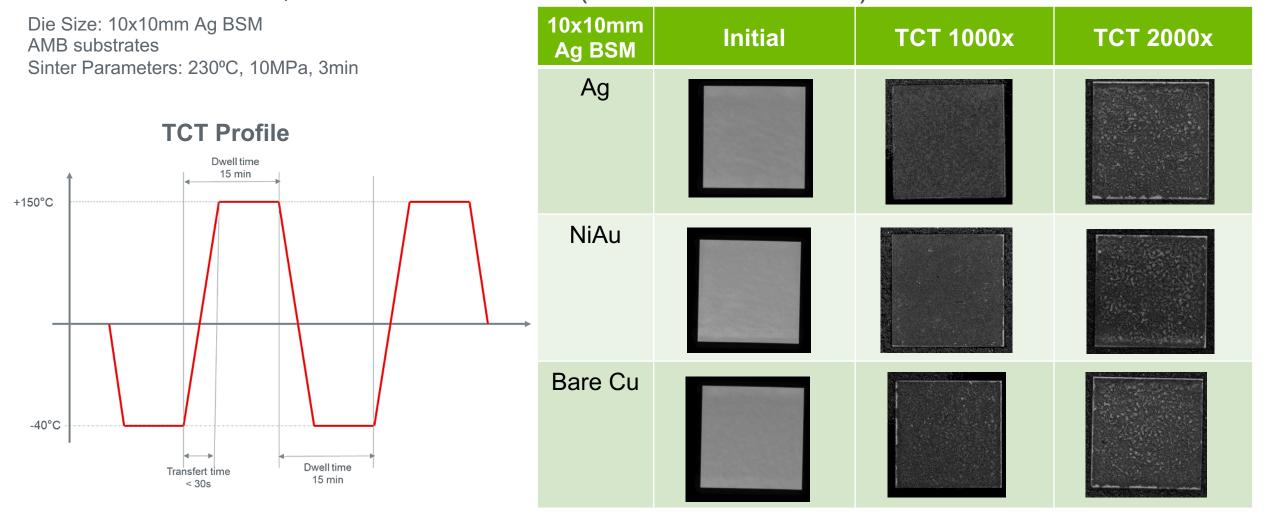

### PE338 SINTERING ON DIFFERENT SURFACES CSAM AT INITIAL, 1000X AND 2000X (TCT -40°C/+150°C)

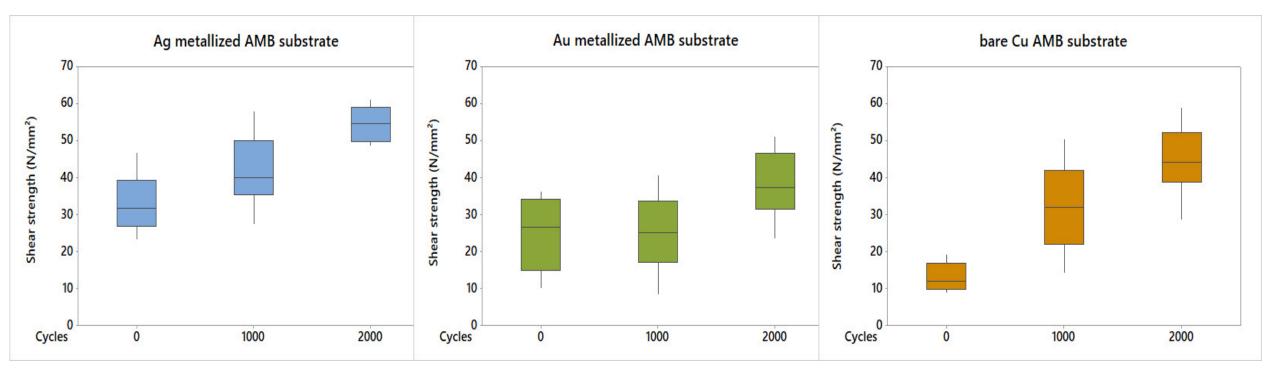

### **PE338 SINTERING ON DIFFERENT SURFACES** DIE SHEAR STRENGTH BEFORE AND AFTER TCT (-40°C/+150°C)

Die Size: 4x4mm Ag BSM Sinter Parameters: 230°C, 10MPa, 3min

#### HERAEUS GROUP

- > Heraeus A globally Successful portfolio company

- > Heraeus Business Portfolio

- > Heraeus Electronics

#### CHALLENGE PERFORMANCE

3

- DTS<sup>®</sup>, sintering and Cu bonding technology for increased lifetime and current/power density

- > Si<sub>3</sub>N<sub>4</sub> AMBs for enhanced heat dissipation and reliability

# 2 HERAEUS AND CHALLENGE OF NEW PACKAGING SOLUTIONS

#### CHALLENGE QUALITY AND YIELDS

- > DTS for reduced production complexity

- Pre-applied sinter paste for reduced complexity and improved yields

Electronics

## Key benefits

Die protection to enable Cu wire bonding with high yield

#### **Best Performances**

- Die current capability increases >50% vs. aluminum wire

- Significantly longer lifetime vs. solder die attach and Al-wire on system level

- Enables higher junction temperatures of more than 200°C

- Significant reduction of power derating or reduction of chip size

<sup>®</sup> Trademark registered in EU, JP Picture: substrate layout by courtesy of Fraunhofer IISBs

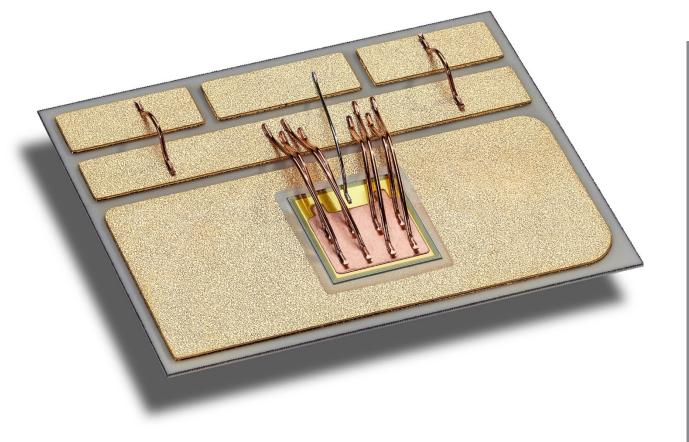

#### DIE TOP SYSTEM

#### Die Top System®

- Silver-sintering Copper foil on top of each die

- Die protection against high bond forces during thick Copper wire bonding

- Spreads current flow

- Heat spreader  $\rightarrow$  lowers hot spot

- Significant increase of lifetime

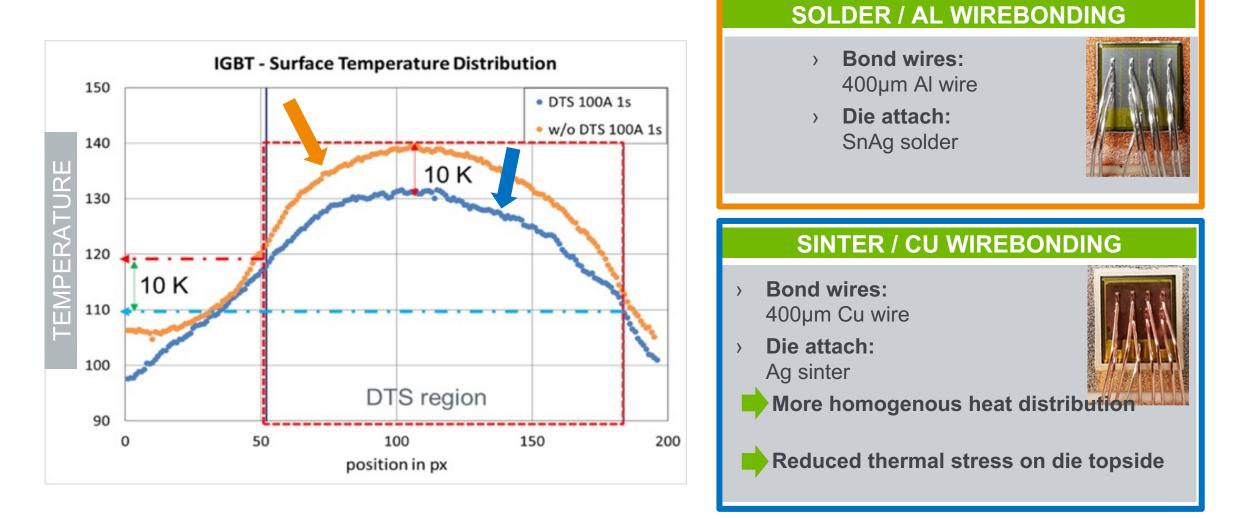

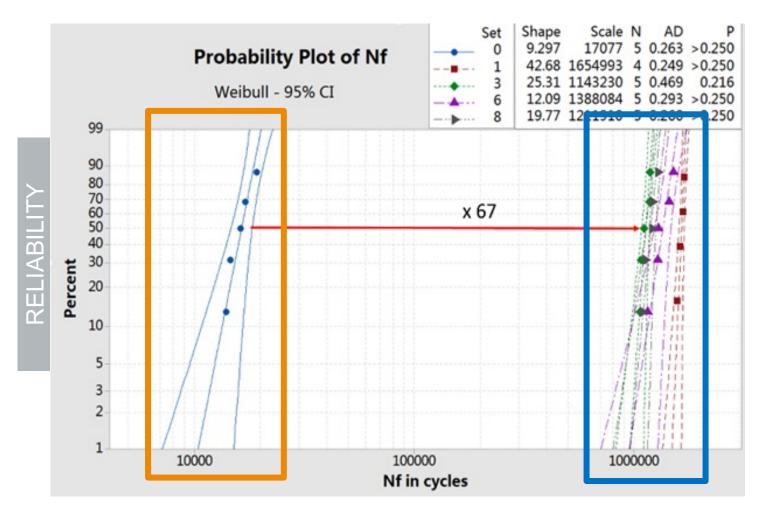

#### POWER CYCLING SOLDER & AL WIRE VS. SINTER & CU WIRE

#### POWER CYCLING SOLDER & AL WIRE VS. SINTER & CU WIRE

#### SOLDER / AL WIREBONDING

- Bond wires:400µm Al wire

- Die attach:

SnAg solder

#### SINTER / CU WIREBONDING

- Bond wires:400µm Cu wire

- > **Die attach:** Ag sinter

Number of cycles increased by a factor > 60

**Highest lifetime and performance**

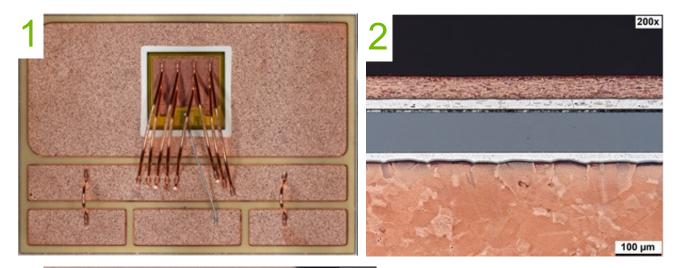

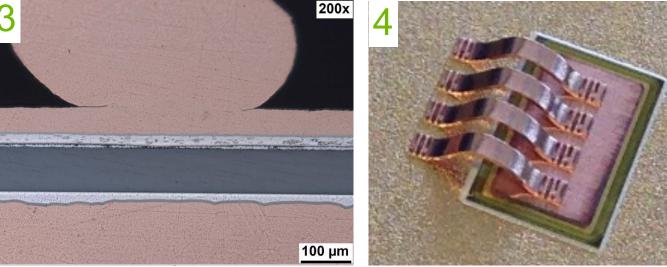

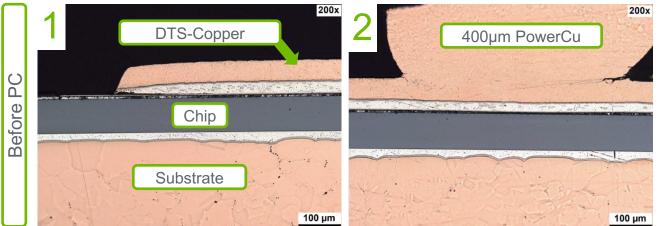

#### **DIE TOP SYSTEM - CROSS-SECTIONS**

#### Die Top System<sup>®</sup> Power Cycling

- Cross-section images

- Very strong interconnection:

- DTS-Sinter-Layer to

- DTS-Copper to

- PowerCu soft wire

- Failure mechanism:

- Degradation layer moves from DTS-Sinter-Layer into Almetallization of the chip (cohesive crack)

Failure mode equal to baseplate-free sets

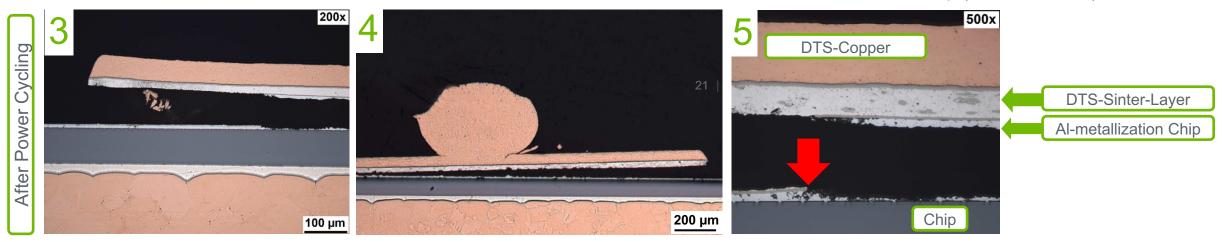

#### DTS<sup>™</sup> IS BASED ON HIGH RELIABILITY AND PERFORMANCE OF SINTERING AND **CU BONDING TECHNOLOGY** COMPARISON OF BULK MATERIAL PROPERTIES ALUMINUM VS COPPER

Advanced Interconnect Technologies in Power Electronics | Heraeus Electronics | PSMA Packaging Industry Session

### SI<sub>3</sub>N<sub>4</sub> AMB COMES WITH ESSENTIAL TECHNICAL ADVANTAGES VS. AL<sub>2</sub>O<sub>3</sub>

<figure><figure>

- 5 times better thermal conductivity for excellent heat dissipation

- By factor of 3 reduced thermal expansion ideally matching semiconductor materials and resulting in low thermo-mechanical stress

- 50 times better reliability proven in thermal shock tests

- 3 times thicker copper layers for increased current capability

**Electronics**

Al2O

400

heat dissipation

reliability

current carrying

capability

Temperature [°C]

300

500

Si3N4

Coefficient of thermal expansion [%]

0.3

0.2

0.1

100

200

## CONTENT

#### HERAEUS GROUP

#### > Heraeus through the ages

- > Heraeus A globally Successful portfolio company

- > A Selection of leading Heraeus products

- Heraeus Business Portfolio

- Heraeus Electronics

#### CHALLENGE PERFORMANCE

- > DTS<sup>®</sup>, sintering and Cu bonding technology for increased lifetime and current/power density

- > Si<sub>3</sub>N<sub>4</sub> AMBs for enhanced heat dissipation and reliability

## HERAEUS AND CHALLENGE OF NEW PACKAGING SOLUTIONS

#### CHALLENGE QUALITY AND YIELDS

- > DTS for reduced production complexity

- > Pre-applied sinter paste for reduced complexity and improved yields

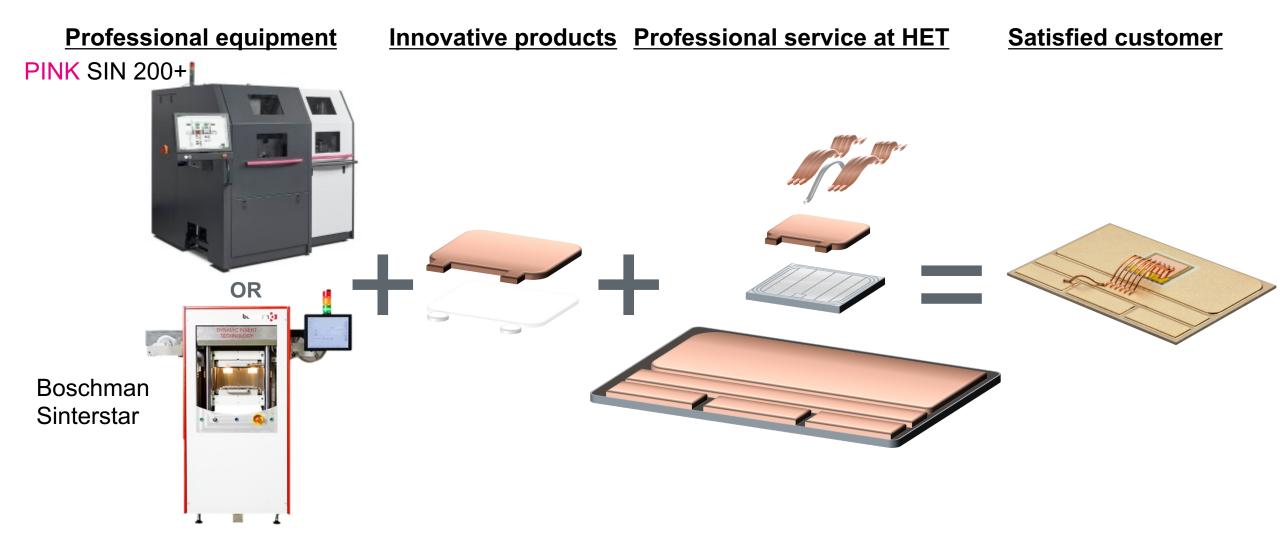

#### The Die Top System (DTS®) is a Material System consisting of:

- > Copper foil with functional surfaces

- > Pre-applied sinter paste

- > Optional adhesive for DTS® fixation prior to sintering

- > Matched copper bonding wires

#### Reduce production complexity, optimize quality and yields:

- > Pre-applied sinter paste & adhesive dot to simplify the assembly

- > One step sintering process of the die and the die top system

- Die Fixation System to prevent relative movement to the die prior to sintering

- Functional surfaces optimized for sintering on the die (under side) and for bonding with Cu wire (upper side)

Copper Foil Pre-Applied Sinter Paste Optional Adhesive

### PRE-SINTERING SERVICE $\rightarrow$ SIMPLIFIED AND HIGH YIELD CHIP ATTACH

### PROTOTYPING SERVICE SINTERING / DTS PROVIDED BY HET

#### **Electronics**

# ENGINEERING SERVICES TO ACCELERATE THE INTRODUCTION OF NEW DEVELOPMENTS IN PRODUCTION

#### **ENGINEERING SERVICES**

#### Simulation

- > Thermal simulation

- > Thermo-mechanical stress simulation

- > Lifetime prediction

#### **Material Analysis**

- > Fatigue analysis

- Root cause analysis

#### **Process Optimization**

- Parameter definition

- > Yield optimization

#### **Prototype Design**

- > Electrical design

- > Mechanical design

#### **Prototype Assembly**

- > Power modules

- > LED modules

- > Documentation, Traceability

#### **Testing and Qualification**

- > Environmental tests

- > Thermal cycling tests

- > Active cycling tests

### CONCLUSION

- Integration of wide bandgap semiconductors like SiC and increasing requirements require optimized interconnection and packaging solutions

- Transformation to high-temperature interconnects from state-of-the-art soldering and wire bonding solutions is imminent

- Significant improvement of reliability and thermal stability can be achieved by

- ..silver sintering as component topside and backside attach

- ...die-top system in combination with copper wire bonding

- ..replacement of conventional alumina bonded substrates to silicon nitride brazed substrates

### THANK YOU FOR YOUR ATTENTION

aarief.syed-khaja@heraeus.com habib.mustain@heraeus.com

Advanced Interconnect Technologies in Power Electronics | Heraeus Electronics | PSMA Packaging Industry Ses