## Micro-Magnetics Based on Single-Litho Core Laminations

Establishing a New PwrSoC Paradigm:

Higher Energy Density & Lower Power Losses for Cost Effective Wafer Level Magnetics

Kamyar Ahmadi, Mo Khodadadi, Matt Wilkowski, Trifon Liakopoulos

## EnaChip Inc. – Intro

- Enachip ("One"-Chip) started operations in 2018 (early stage, VC funded startup)

- Mission: Re-invent Power Management by Commercializing Wafer Level Magnetics

HQ Located between NYC and Philadelphia (30min south of Newark Airport)

#### **THE POWER PROBLEM**

**Power Is** Wasteful And Uses Too Much Space

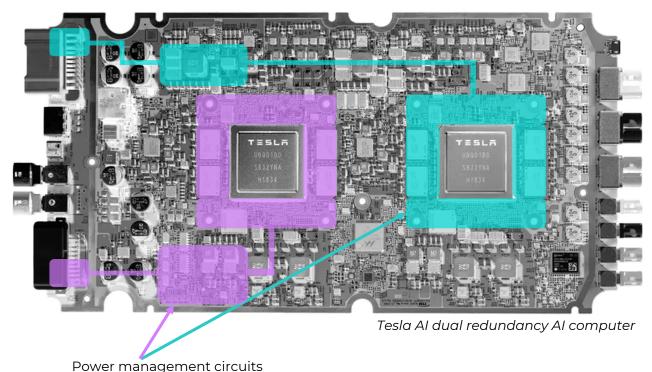

### **Example chipset**

There are **1600 I/O connections** per processor The majority of connections (**60%**) are for **Power**

### THE ROOT CAUSE of POWER INEFFICIENCIES

### Power Is Separate From Silicon

EnaChip Inc. presented at APEC 2022

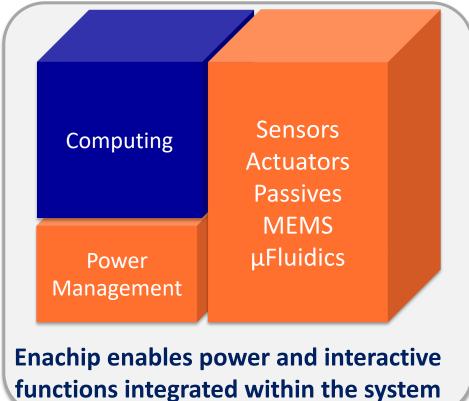

### EnaChip – Breakthrough Innovation in Integration

COMMERCIALLY VIABLE TECHNOLOGY THAT INTEGRATES POWER MAGNETICS WITH SILICON IC

20-50% Energy Savings 30x Smaller Size 3x Lower Cost

#### Power System in Package State of the Art

Power System on Chip EnaChip Enabled Solution

### Wafer Level Magnetics

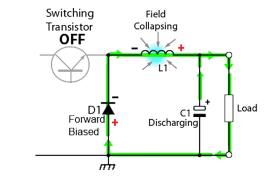

(Si & GaN trends to higher  $F_{sw}$  shift the PwrSoC's bottleneck to magnetics)

The inductor is acting as an energy storage element on a switching converter

Inductor size reduction:

- Core Materials: High B<sub>sat</sub> allows for size reduction

- Output Power: High F<sub>sw</sub> allows for size reduction

- High F<sub>sw</sub> increases system losses due to core material limitations and IC switching losses

- Multi-layered laminated cores required for meaningful integration of magnetics

# Wafer Level Magnetics (Core technology options)

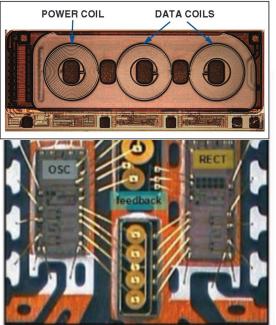

#### **Aircore WLM**

iCoupler, ADI

#### Multilayered thick film sputtered core

#### Electroplating thick film core

Enpirion

#### Electroplating windings

#### Electroplating windings

#### Electroplating windings

### Wafer Level Magnetics (Core technology comparison)

#### **Aircore WLM**

- 1 Easy to fabricate

- 1 Low cost

- 1 Low power loss

- High near magnetic fields

- Low inductance

- Requires high F<sub>sw</sub>

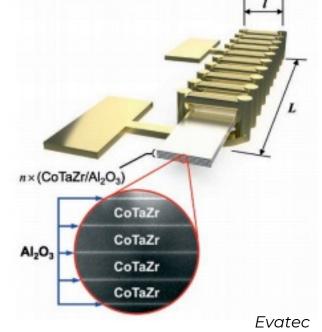

#### Multilayered <u>thick</u> <u>film</u>sputtered core

- High performance

- Process/thickness control

- FEOL compatible

- Slow (.1μm/min)

- High cost process

(~10-20x of the plating )

- High capital costs

(>5X over electroplating)

- Thickness/Stress limitations (<20L, <3 um)</li>

Power ≈ core thickness

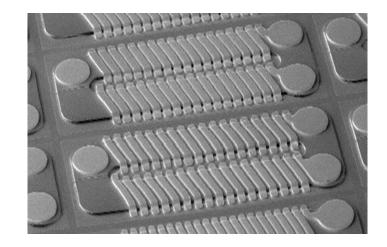

### Electroplating <u>thick film</u>core

- Fast deposition (lum/min)

- Low cost process

- Intrinsically low stress → No. layers (>100)

- Low capital costs (BEOL-OSAT)

- Highly scalable

- Metallic high µ crystalline films have low ρ→ small skin depth → higher loss

- Multi-layer laminations

needed for high currents >1A

Complex multi-layer/multi-mask

cost prohibited process

## **Enachip's Technology Platform**

Enachip addresses the electroplating core shortcomings to enable a high performance WLM cost competitive solution

#### Electroplating core

- Fast deposition process (1μm/min)

- Low cost process

- Intrinsically low stress → No. layers (>100)

- Low capital costs (BEOL-OSAT)

- Highly scalable

- Metallic high µ crystalline films have low ρ→ small skin depth → higher loss

- Multi-layer laminations needed for high currents >1A Complex multi-layer/multi-mask

cost prohibited process

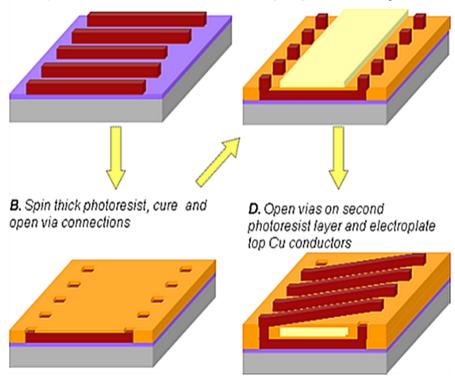

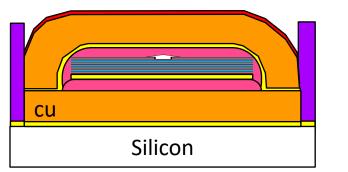

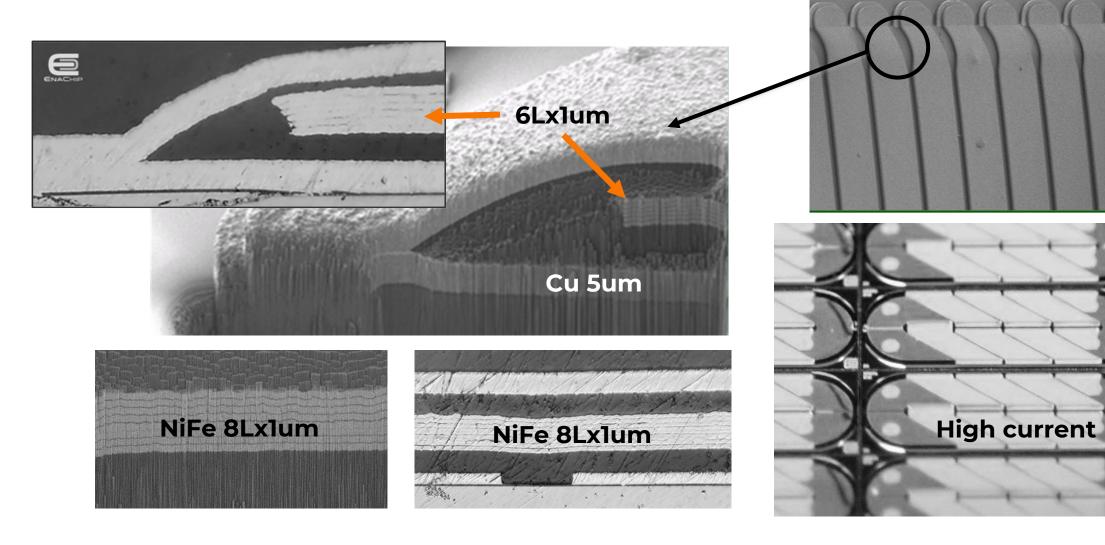

### Key Process Modules (Electroplated micro-coils)

- Thick electroplated Cu (5um 80um)

- Dielectric insulation/planarization

- Electroplated high frequency magnetic alloy laminations

A. On top of a SiO2/Si wafer electroplate thick Cu conductors

C. Electroplate Cu via conductors and (FCA) laminated magnetic core

Ref. Modern Electroplating, 5<sup>th</sup> edition Mordechay Schlesinger (Editor), Milan Paunovic (Editor)

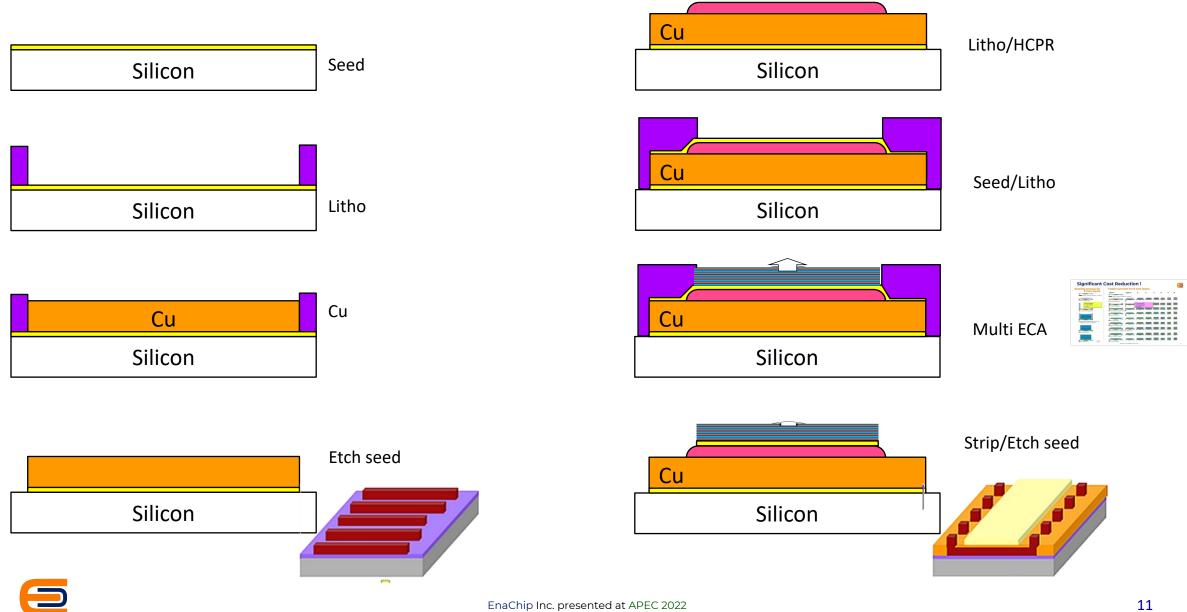

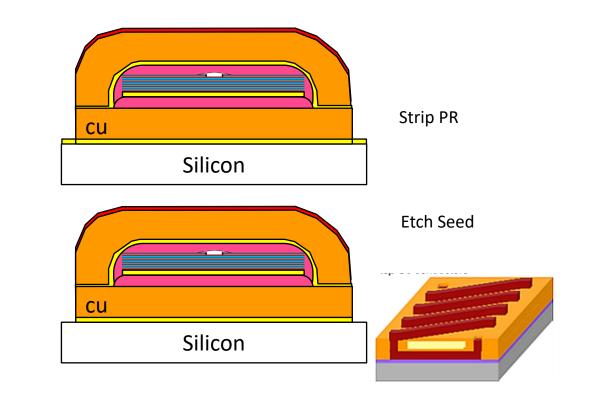

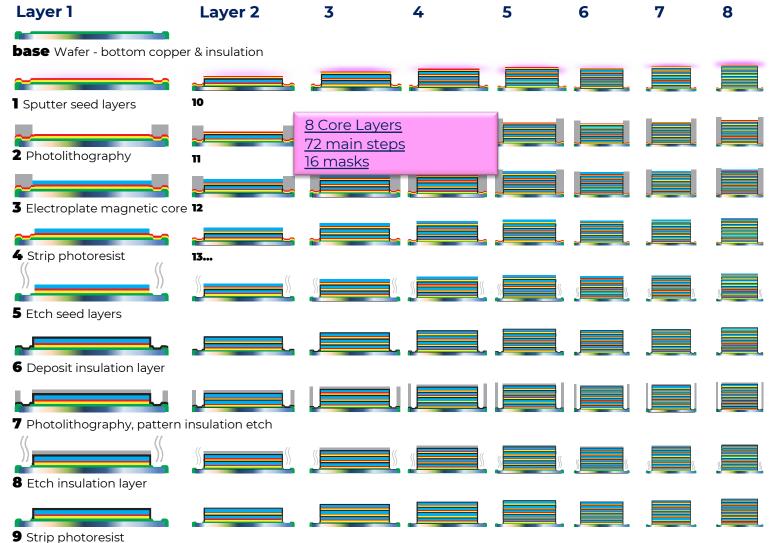

### **Process Flow**

### **Process Flow**

Plate Cu/Ni/Au

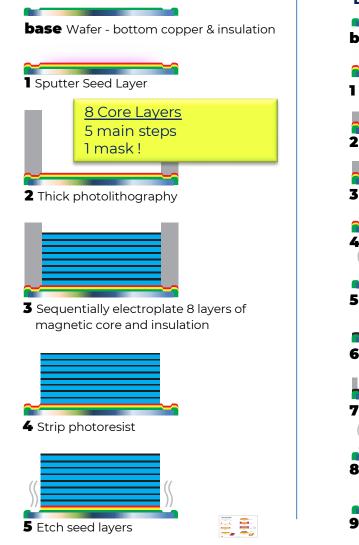

## **Significant Cost Reduction !**

#### EnaChip process for 8 core layers

### **Today's process for 8 core layers**

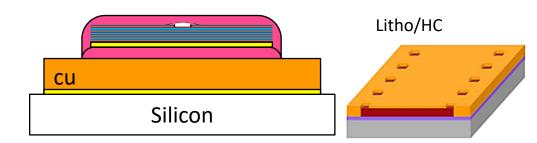

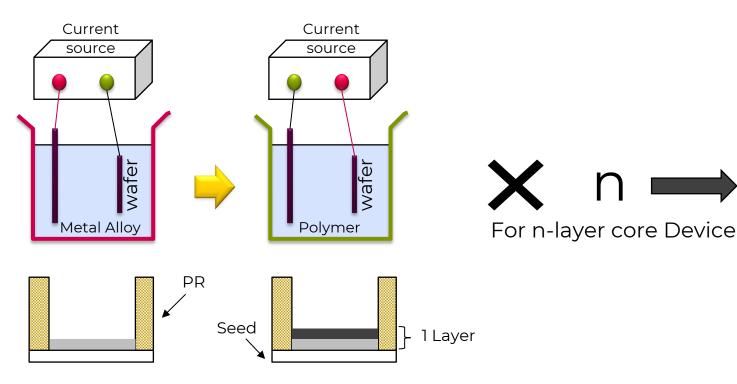

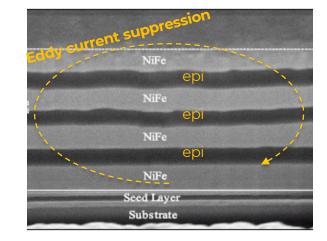

### Multi Layer process incorporates <u>electroplated</u> insulator (epi)

- Electrochemically synthesized insulator

- Conjugated polymer based

- Conductivity < 1S/m</p>

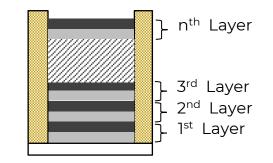

## **Multi Layer process Thin Insulator !**

■ Multiple layer with thin Insulator → Very high layer packing coefficient

→ Low profile cores

EPI performance is comparable to ideal insulator with ability to suppress Eddy Current Loss

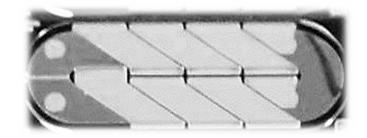

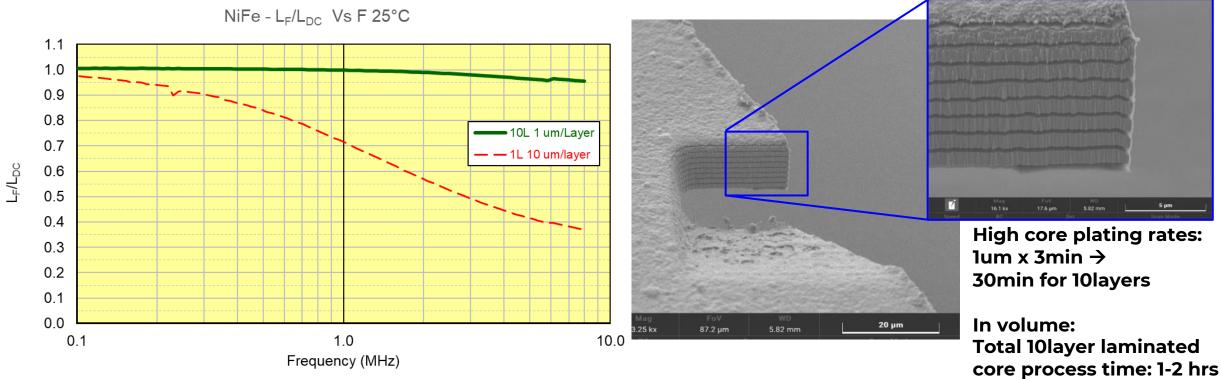

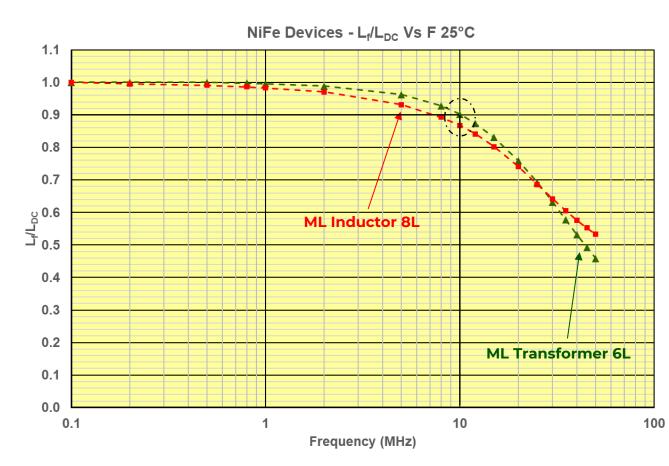

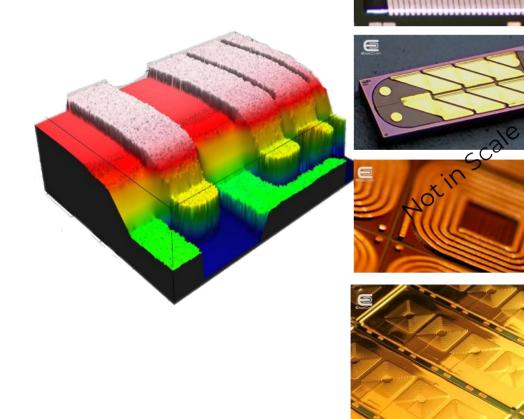

### Device Performance Using Mag Core with Single Mask n-Layer process

EnaChip multilayer process extends the performance of NiFe materials to maintain higher values of inductance at higher frequencies.

L=20-40nH die 2mm x 5mm

L=120-150nH die 1.7mm x 4.0mm

### **Device structure**

## **High Performance proprietary Mag. Alloys**

9

## **High Performance proprietary ECA alloy**

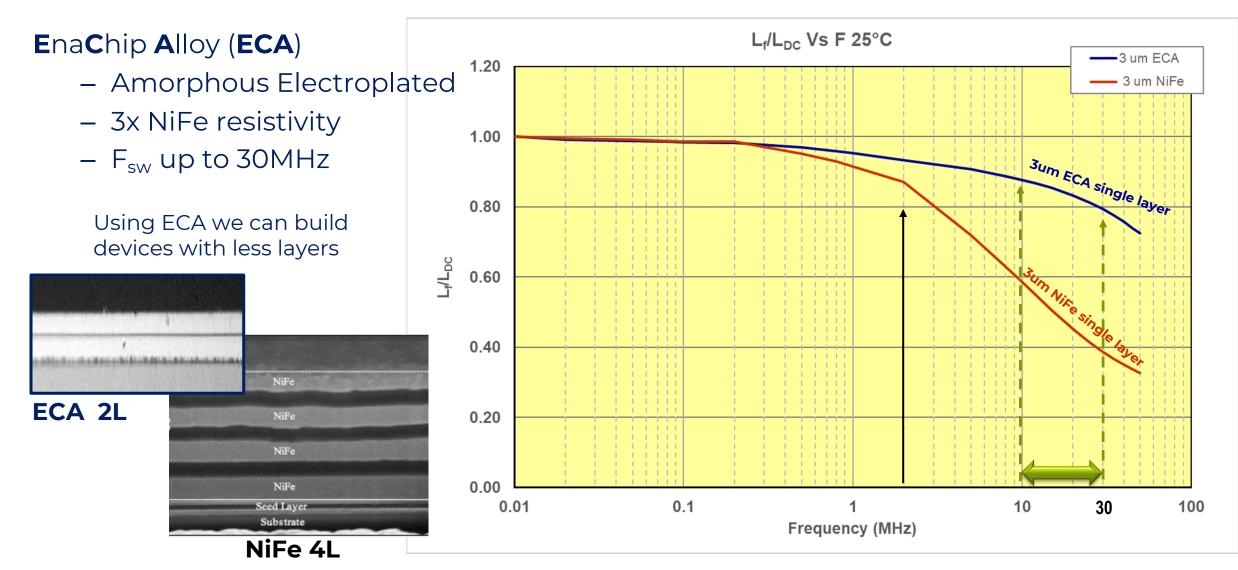

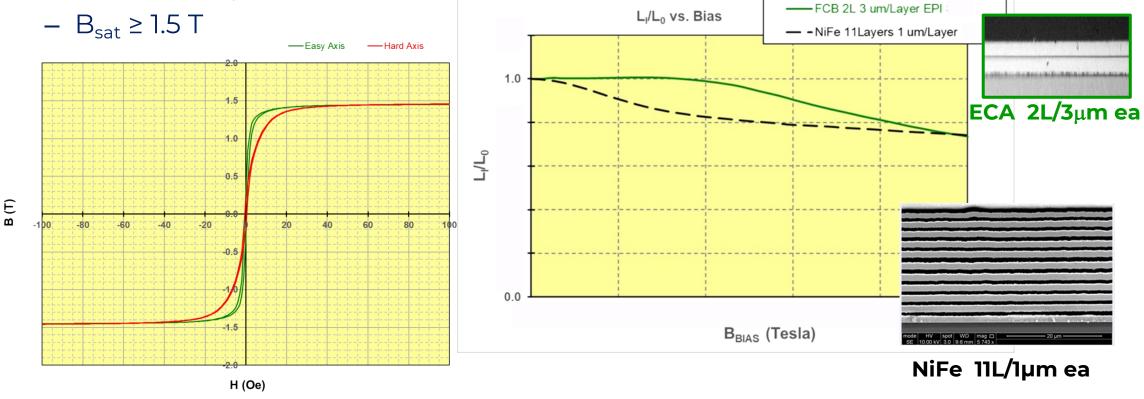

### EnaChip Alloy (ECA)

- Permeability up to 900

ECA Bias operational range >> NiFe

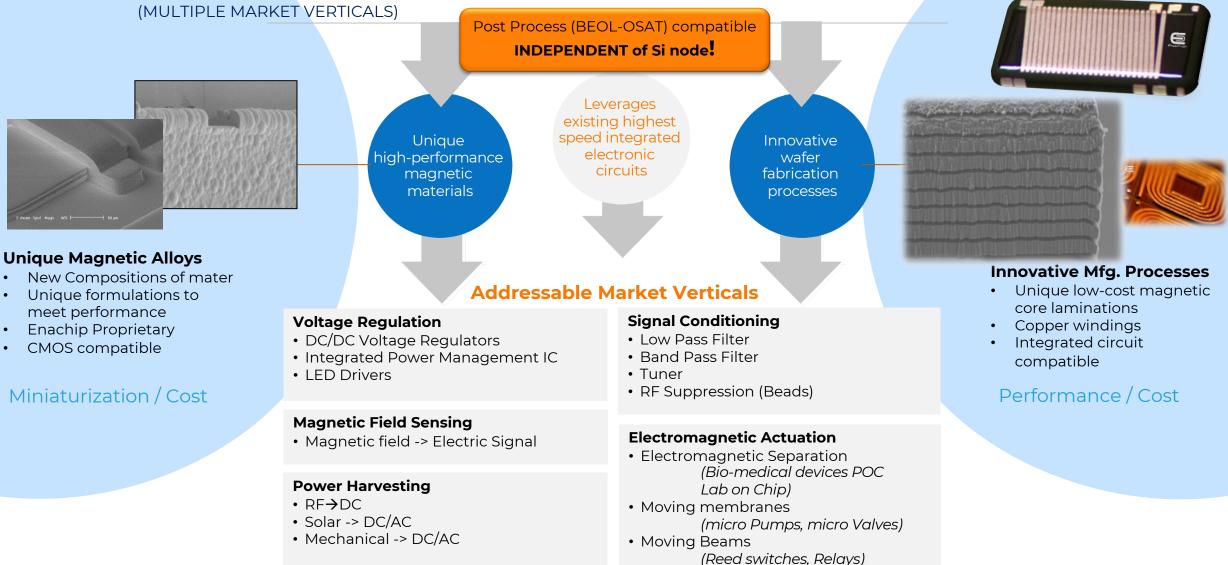

### **EnaChip Creates an Enabling Technology Platform**

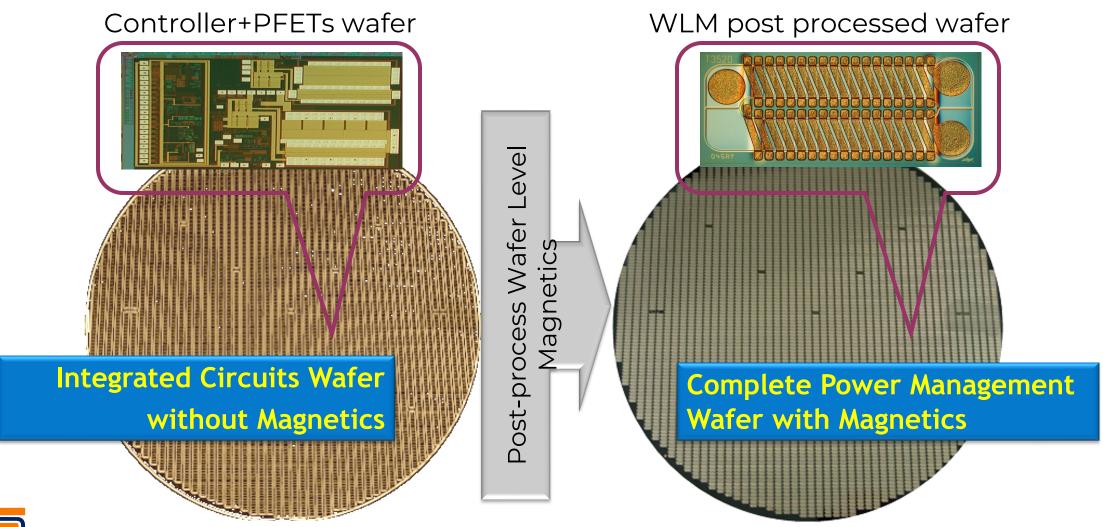

### The advantage of being... Node-Agnostic

(Enachip's "Magnetic Functionality" can be post-processed on **ANY substrate** from **ANY foundry** and **ANY node**)

EnaChip Inc. presented at APEC 2022

21

### **Smart Power Integration is needed in All Systems**

WLM platform enables integration of power and interactive functions - **SoC** *Wafer Level Magnetic*

### System Integration at chip level

### Devices are "talking" to environment and to the users

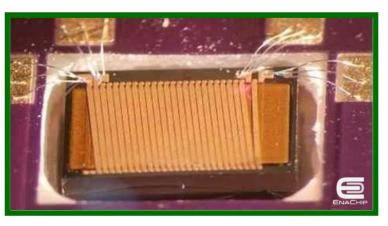

## **Device Examples**

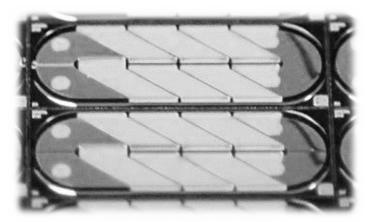

- Thick Cu toroid micro-inductors

Multi-core toroids

- Spiral coils

- Electromagnets/Actuators

- Transformers

- Sensors

## Walk away message:

First time demonstrated continuous electroplating of magnetic film and insulator sequentially

### That enables:

Single mask thin film magnetic core laminations for high performance wafer level magnetics

Fast and Low cost BEOL – CMOS compatible simple manufacturing process with existing infrastructure

Performance enhancement by unique proprietary high performance electroplated magnetic alloys

### Thank you!