# PwrSoC: Industry Adoption in High-Volume Applications

Francesco Carobolante, IoTissimo® LLC

ISO5.7

### Agenda

- Computing Requirements Driving Power Supply on Chip

- Drivers and Enablers

- Evolution of Products in the Market

- What Is Next?

- Conclusions

## The Evolution of PwrSoC Requirements

- Initial Motivation:

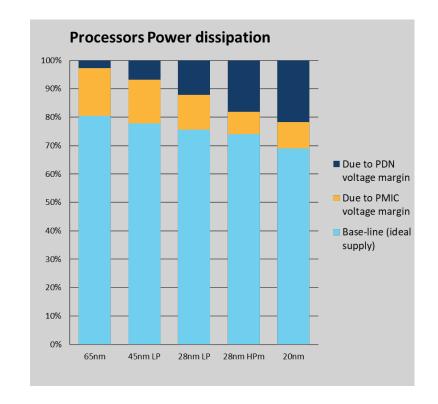

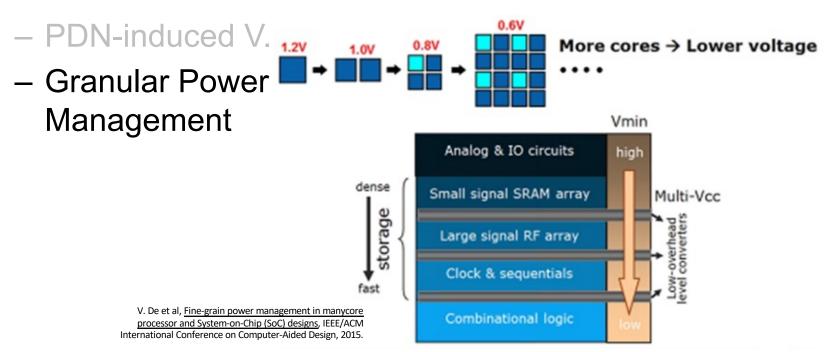

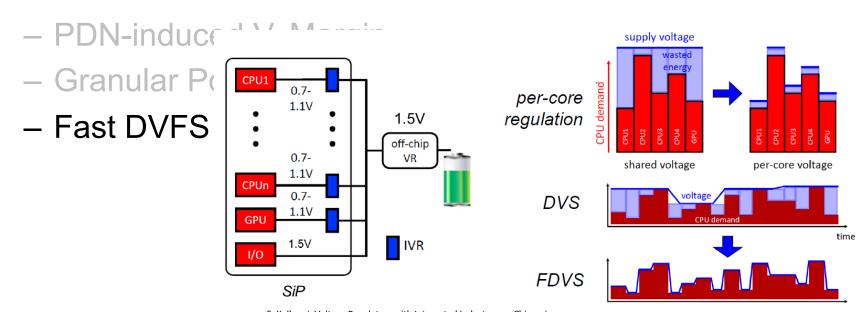

- PDN-induced Voltage Margin

F. Carobolante, <u>Power Supply on Chip: from R&D to commercial products</u>, PwrSoC 2014

### The Evolution of PwrSoC Requirements

Initial Motivation:

### The Evolution of PwrSoC Requirements

### Initial Motivation:

S. Kulkarni, <u>Voltage Regulators with Integrated Inductors on Chip vs in Package</u>, Applied Power Electronics Conference and Exposition, 2020.

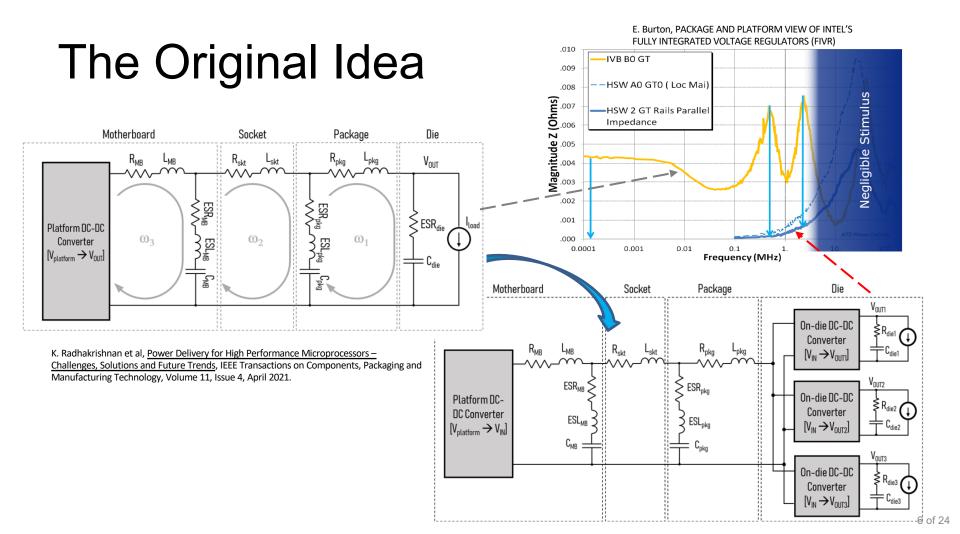

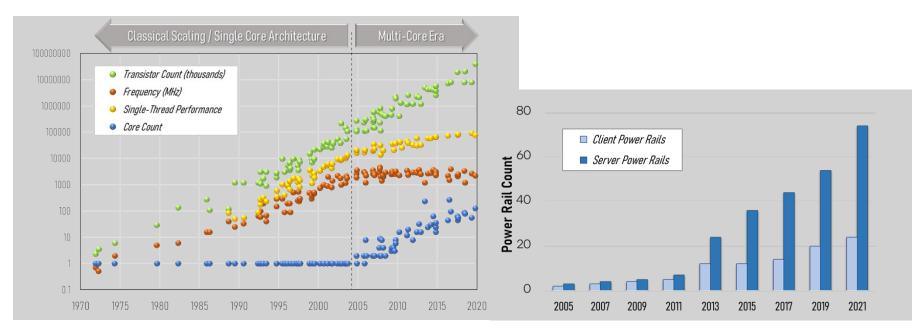

### Meantime, on the Processor Side...

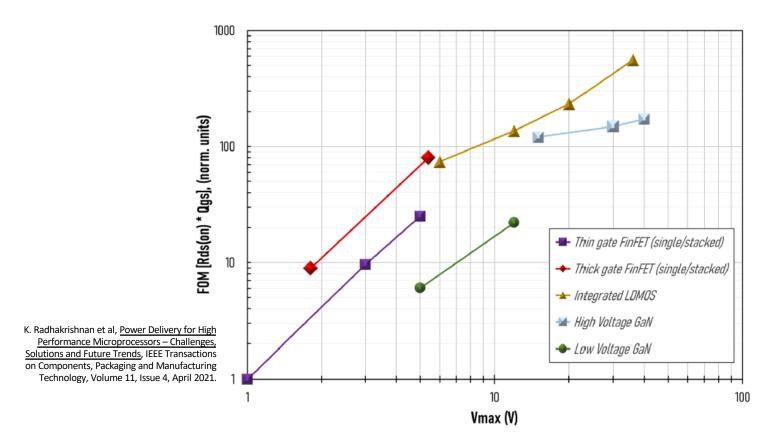

K. Radhakrishnan et al, Power Delivery for High Performance Microprocessors — Challenges, Solutions and Future Trends, IEEE Transactions on Components, Packaging and Manufacturing Technology, Volume 11, Issue 4, April 2021.

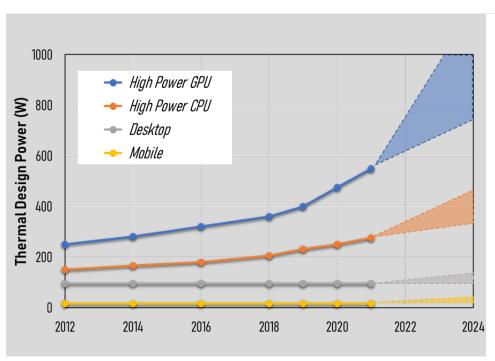

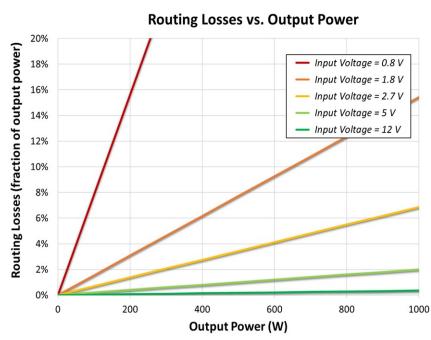

### The New "Power Wall"

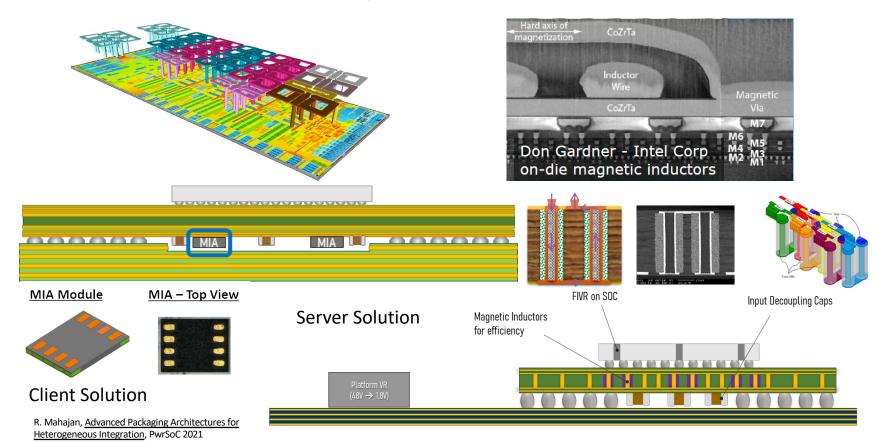

R. Mahajan, Advanced Packaging Architectures for Heterogeneous Integration, PwrSoC 2021

Assumes path resistance of 0.5  $m\Omega$

K. Radhakrishnan et al, <u>Power Delivery for High Performance Microprocessors – Challenges, Solutions and Future Trends</u>, IEEE Transactions on Components, Packaging and Manufacturing Technology, Volume 11, Issue 4, April 2021.

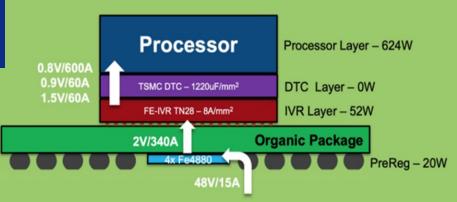

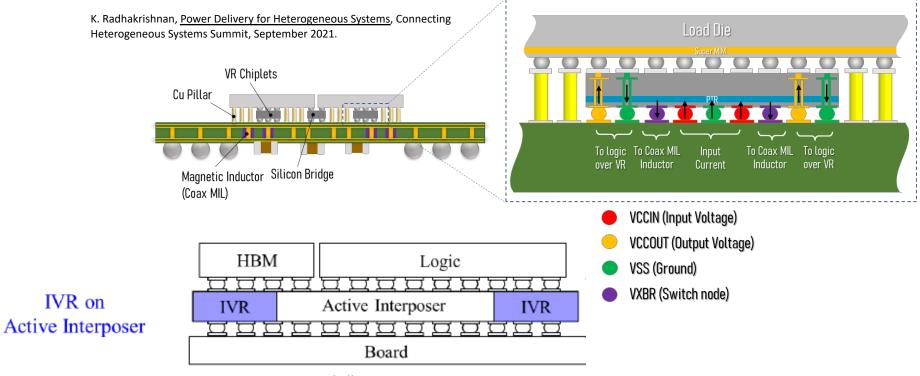

### Two-stage Conversion Is Mandatory

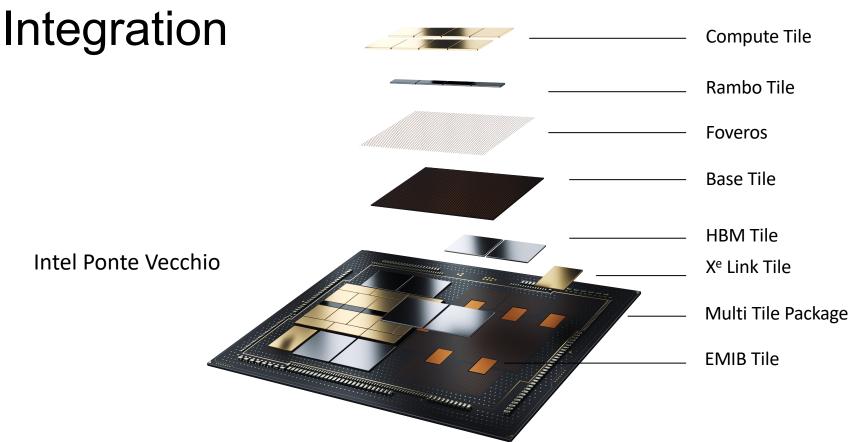

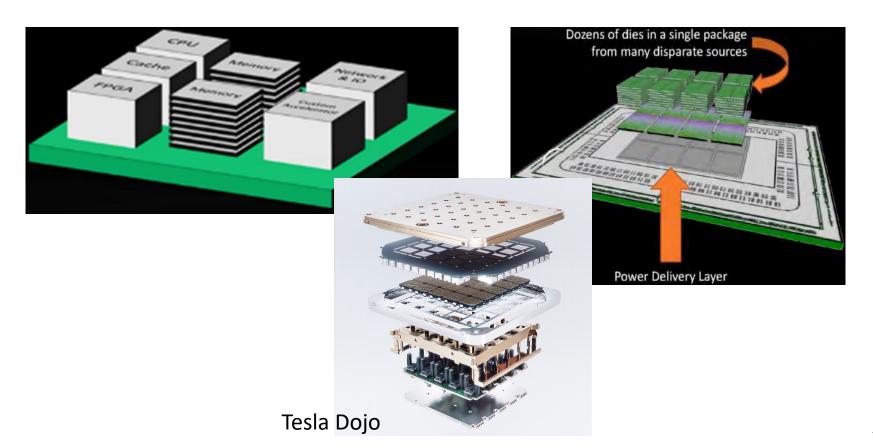

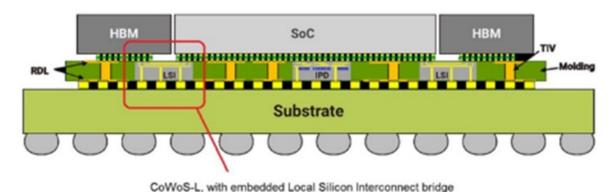

Now: Chiplets and Heterogeneous

### Shortest Path for Current Flow Is Vertical

## How do we get there?

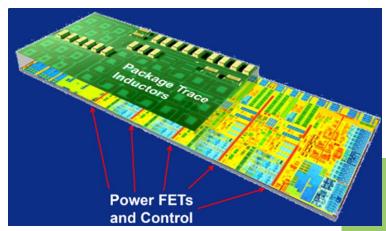

Package and Platform View of Intel's Fully

Integrated Voltage Regulators (FIVR)

N. Sturcken, IEEE Power Electronics Society October 22, 2020, Integrated Power – A Virtual Panel Session

### Many Options Are Proposed

"BEOL, chip-last assembly"

Highlights of the TSMC Technology Symposium Part 2

2020 11 18 IMAPS' webinar Enabling a Path to System Level Solutions

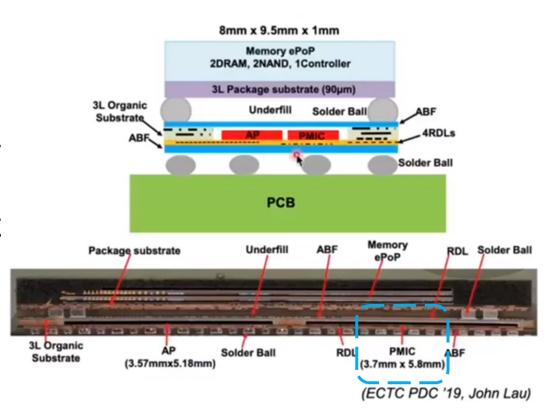

**ASE's Double-Sided Mounting SiP**

## Many Options Are Proposed

S. Kim et al., <u>Power Integrity Comparison of Off-chip, On-interposer,</u>

On-chip Voltage Regulators in 2.5D/3D lcs

## PWRSOC IS NOW INTO EVERYDAY PRODUCTS

### Product Generations: Intel

## Product Generations: Samsung

- This 2018

Product

shows initial integration of Power

Management

- Where is Samsung in 2022?

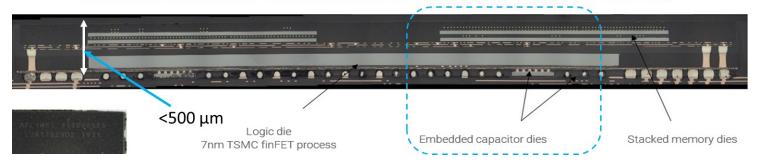

## Product Generations: Apple

Apple A13 designed by Apple (2019) (manufactured by TSMC, 7 nm finFET process and packaged by TSMC's InFO technology)

### Global Foundries Joins the Path

- GF joins TSMC in providing integrated inductors in silicon

- Others are working on it

150µm Si + 50µm SUMMIT Laminated Magnetic Core Integrated: 55BCDLite+SUMMIT+RDL/Bump BUMP BUMP Underlying 55BCDI

Transformer with WLCSP balling

L. Peng et al., <u>Silicon-based Ultimate Miniature</u>

<u>Magnetic Inductors and Transformers</u>

(SUMMIT) for High-frequency Switching Regulator,

PwrSoC 2021

### What Is "More Than Moore"?

- Heterogeneous Integration enables:

- 1. Higher Performance and Efficiency

- Integration of Passive Components

- Integration of III-V Semiconductors

- 2. Co-optimization of Signal & Power Integrity

- FO-packaging

- TSV's

- WoW and CoW

- Silicon Interposers and Silicon Bridges

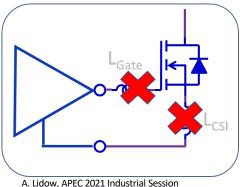

## GaN Is Making Great Progress

Integration of Power and Drivers

A. Lidow, APEC 2021 Industrial Se presentation number 3017

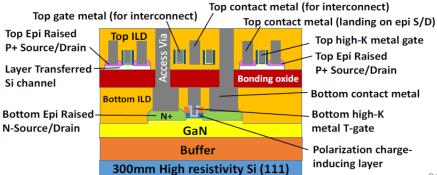

Heterogeneous Integration of Low-Voltage

Si+GaN Processes

H.W. Then et al., <u>3D heterogeneous integration of high</u>

<u>performance high-K metal gate GaN NMOS and Si</u>

<u>PMOS</u>

<u>transistors on 300mm high-resistivity Si substrate for</u>

energy-efficient and compact power delivery, RF (5G and beyond) and SoC applications, IEDM19-402

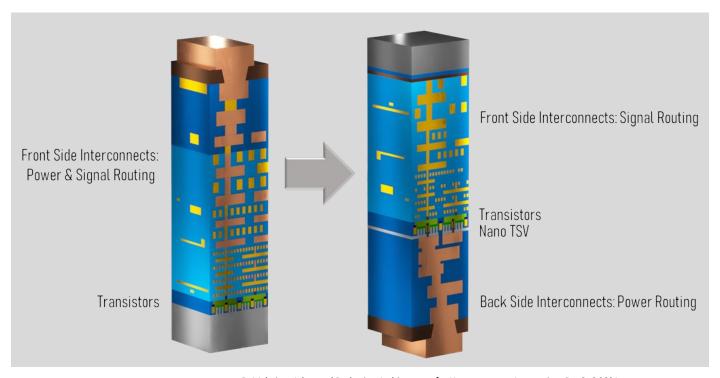

### Process Is Driven by Power Routing

Signal on one side – Power from the other side

### Conclusions

- Incorporating Power Management in High Performance SoC is mandatory! Heterogeneous Integration is the solution.

- Each application has different requirements and constraints: there is no single solution!

- High Performance Computing requires Two-stage architecture for any supply ≥5 V. GaN is a good option for the first stage.

- Back-end processing has evolved dramatically: FO packages, TSV, WoW and CoW bonding are now in volume production.

- Computing Industry has hit the "Power Wall": Performance and Efficiency improvements require bringing Power Management into the System Architecture – from the start of the project!

## Many Thanks to the IEEE HIR Members!

#### Integrated Power Electronics (IPE) Technical Working Group (TWG)

**Doug Hopkins** North Carolina State University DCHopkins@ncsu.edu

Patrick McCluskey University of Maryland mcclupa@umd.edu

PM Raj Florida International University mpulugur@fiu.edu

Cian Ó Mathúna Tyndall National Institute cian.omathuna@tyndall.ie

HETEROGENEOUS

YY Tan ON Semiconductor tan.vikyee@onsemi.com

Ray Fillion Fillion Consulting fillion.consulting@gmail.com

Tzu Hsuan Cheng North Carolina State University tcheng8@ncsu.edu

Robert Davis ON Semi Robert.Davis@onsemi.com

**Bob Conner** X-Celeprint

Francesco Carobolante IoTissimo bconner@x-celeprint.com francesco@iotissimo.com

Jason Rouse Corning rouseih@corning.com

Slide 1

### Thank You for Listening!

Apollo 13 - Universal Pictures

My contact: francesco@iotissimo.com

"Power is Everything"\*

John Aaron- Apollo 13 Flight Controller