Industry Session 05: PwrSoC for Next-Gen Power

# Integrated Capacitors and Energy Storage Devices for PwrSoC: Trends and challenges

Mohamed Mehdi Jatlaoui, Product Line Manager Murata Integrated Passive Solutions mohamed.jatlaoui@murata.com

Tuesday, March 22, 2022

### Outline

- 1-Introduction

- 2- Silicon Capacitors technology

- 3-3D Silicon capacitors for power applications

- 3.1-Automotive

- 3.2- Optical transceivers

- 3.3- Mobile & HPC

#### Transmission Temperature sensor Rotation speed torque control Under the Hood In cylinder pressure temperature sensor Exhaust Composiziture sonso kills sensor iser Box emperature sensor Wheels and brakes lotation speed Regiment control latitud control Temperature latomatic gear base control Rotation speed (ABS)

#### 4- Conclusion

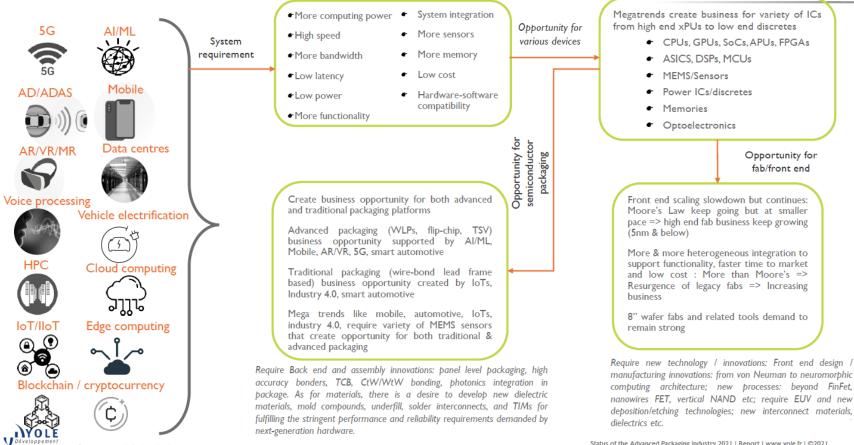

#### 1- New Trends & Drivers

Source: Yole Développement

Status of the Advanced Packaging Industry 2021 | Report | www.yole.fr | @2021

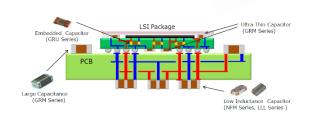

### 2- Silicon Capacitors extending MLCC portfolio

High Density

Low ESL Low ESR

Low profile

Mechanical strength

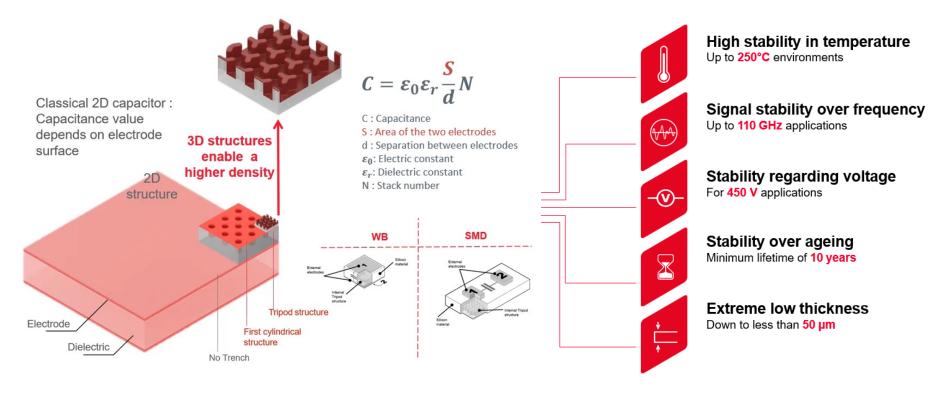

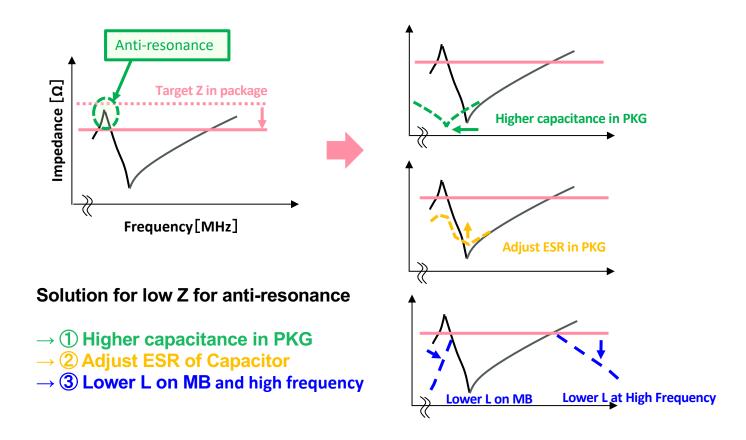

### 2- Silicon Capacitor - Technology Road Map

Murata is committed to a vision of developing innovative integrated Silicon capacitors to match the requirements and trends of SOC

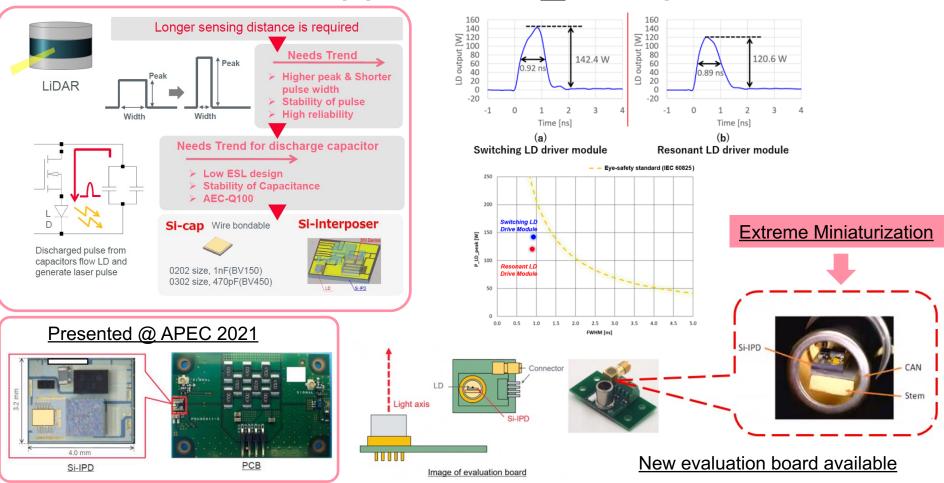

#### 3.1- LiDAR Applications\_Si-cap benefits

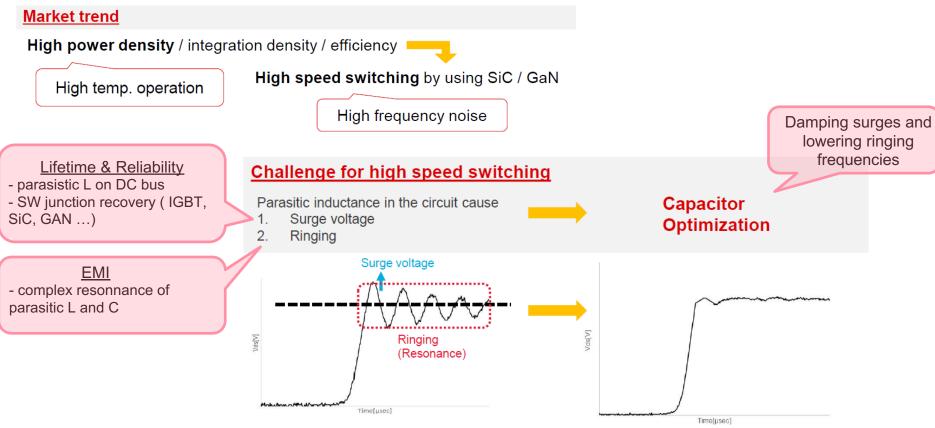

# 3.1- WBG power switching challenges

Integration of low ESL components and innovative packaging

#### Built-in snubber solution for power module

# 3.1- Synergy with Murata Film capacitor

#### 1.High temp. operation (200°C) Put Si-RC device close to SiC/GaN which

operates under high temp.

#### 2. Same mounting method as power device

Ex) Top → Wire bonding Bottom → Soldering and Sintering

#### 3. Function of CR device as 1 chip

Realize downsizing of power module by saving space. (If you used other capacitors, both capacitors and resistor must be used.)

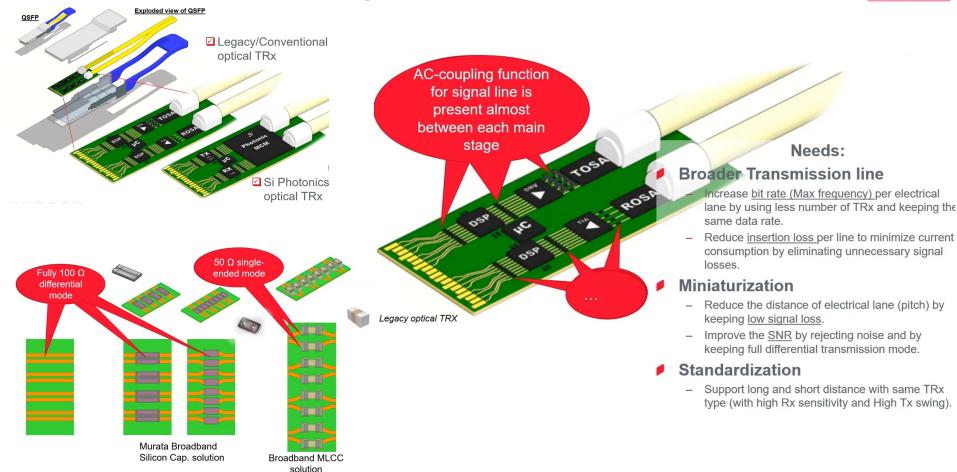

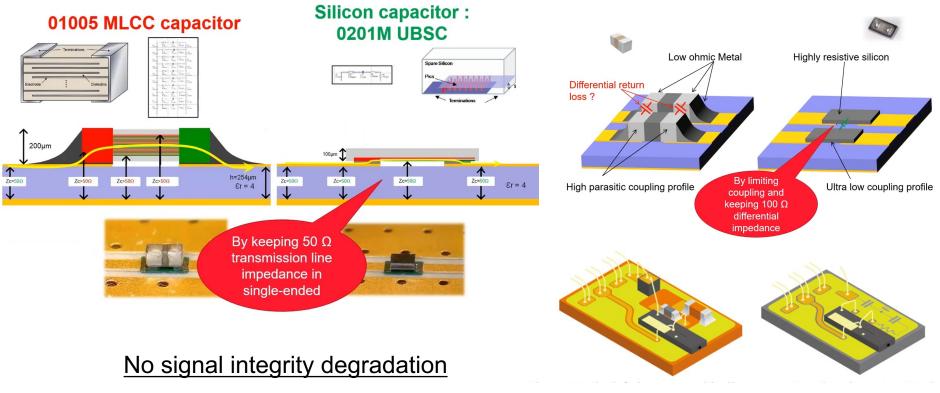

#### **3.2- Optical Transceivers**

Data centres

#### **3.2- Optical Transceivers**

Further integration with Si-IPD

Data centres

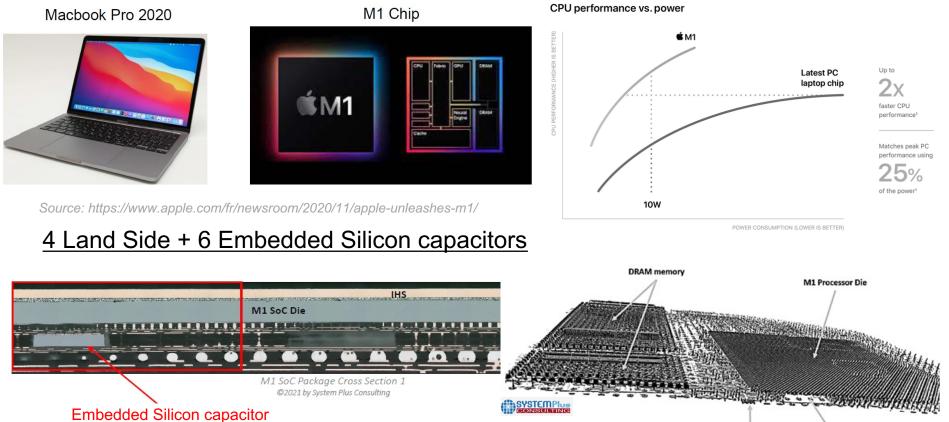

### **3.3- PDN Applications**

Source: SystemPlus consulting

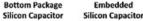

#### 3.3- Lower PDN impedance

# 3.3- Increased Interest in Si-Caps is Driven by ..

| 16 nm | 10 nm | 7 nm | 5 nm                               | 3 nm |

|-------|-------|------|------------------------------------|------|

|       |       |      |                                    |      |

|       |       |      | Challenging Power Delivery Network |      |

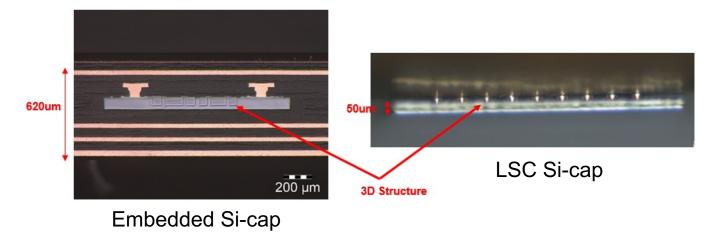

#### 3.3- Murata's innovative solutions

Ultra Low ESL Silicon capacitor with:

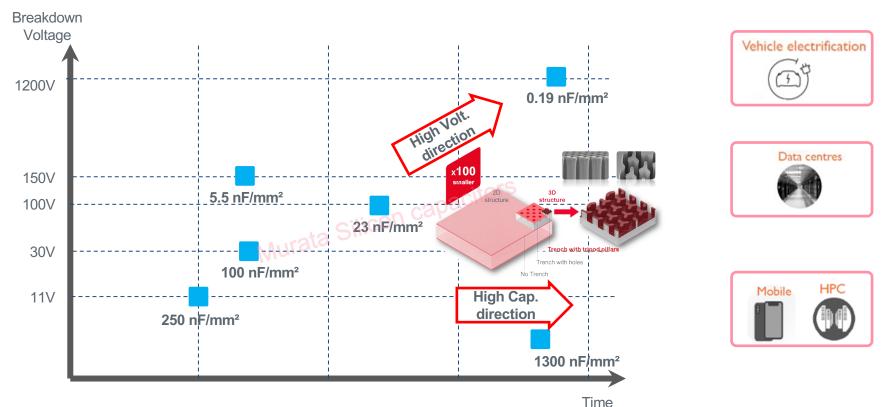

- World record of 1300 nF/mm<sup>2</sup> in Silicon, 1 µF in ultra compact 0404 form factor

- Ultra-low ESL (< 5 pH) and ESR (< 10 m $\Omega$ )

- <50 µm thickness

- Mechanical robustness of silicon during assembly

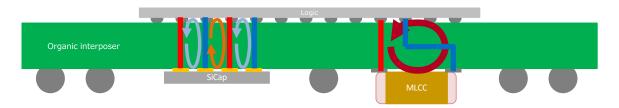

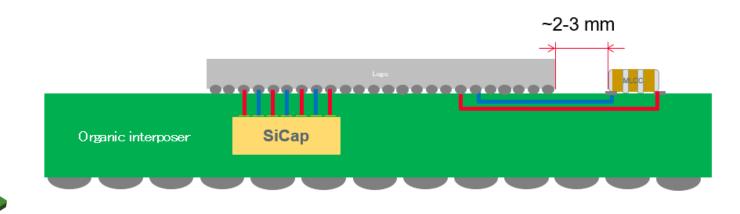

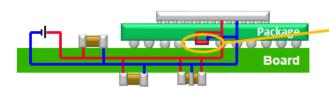

#### 3.3- Landside benefits

Si-Caps help reducing ESL

- Si-Caps intrinsic ESL is lower than MLCC

- Assembly ESL is reduced

- Multi-terminals generate smaller current loop → lower ESL (shorter distance between pads)

- Low-profile enables integration closer to IC

#### 3.3- Embedded benefits

Source: N. Normand [IMAPS 2021]

| Decoupling cap | Parasitic from<br>assembly            | Cap intrinsic ESL                                     | Conclusion  |

|----------------|---------------------------------------|-------------------------------------------------------|-------------|

| MLCC die-side  | High ESL<br>high distance - Underfill | High ESL                                              | Standard    |

| SiCap embedded | Low ESL<br>close to IC                | Low ESL<br>Multi-terminals<br>Adjacent opposite loops | Improvement |

#### + Ability to reduce substrate X/Y size

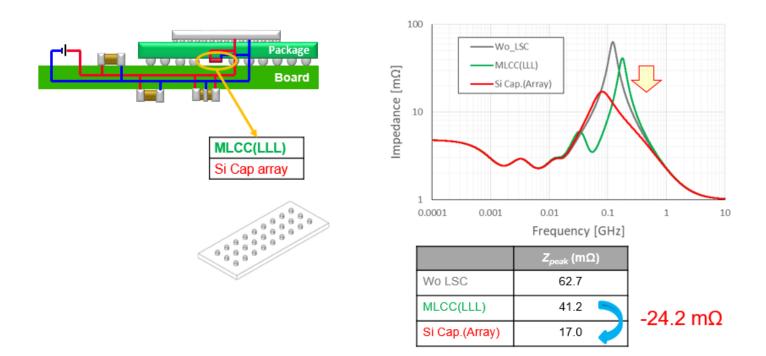

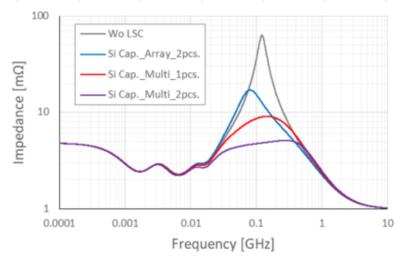

#### 3.3- Si-caps improve system performance

- Abrupt changes in processor activity induce large current transients in the power delivery network

- There is a need to reduce losses → provide better and more granular regulation to the processor cores

#### 3.3- Si-caps improve system performance

Cap Array

Z<sub>peak</sub>: anti-resonance between Chip and Board

|                 | <i>Z<sub>peak</sub></i><br>(mΩ) | Improvement rate<br>(%) |

|-----------------|---------------------------------|-------------------------|

| Wo LSC          | 62.3                            |                         |

| Si Cap. ×2 pcs. | 17.0                            | -72.7%                  |

| Si Cap. ×1pcs.  | 9.1                             | -85.4%                  |

| Si Cap. ×2pcs.  | 5.1                             | -91.8%                  |

0404 Multi-term

\* Wo LSC = Without Land Side Capacitor \* In the case, we connect Si Cap.(Array) to same power line

• Z<sub>peak</sub> is reduced by mounting LSC.

#### 4. Conclusion

- Miniaturization enables new markets and applications

- Si-cap use from niche market/application to wider usage

- Solutions that both increase the performance and reduce the power consumption

- Automotive:

- High voltage, low ESL loop, Thermal stability

- Silicon capacitive interposer presents innovative solution from electrical and assembly point of view

- Challenges: automotive reliability standard (AEC-Q100) and Eye safety (IEC 60825)

- DataCenter:

- Increased bit rate and reduced insertion loss

- Improved SNR

- Mobile & HPC:

- Requirements in terms of high density, low profile and low ESL

- Silicon capacitors flexibility: process, materials, design, interconnects and assembly

#### Thanks a lot for your time and attention!

### Any questions and/or comments?