The eGaN<sup>®</sup> Technology Journey Continues

APEC - PSMA Industry Sessions MPS and EPC Drive Efficiency and Power Density in 48V Datacenters

# EPC eGaN<sup>™</sup> enables MPS high power density fixed ratio Intermediate Bus Converters

Alex Richardson – Product Marketing, MPS

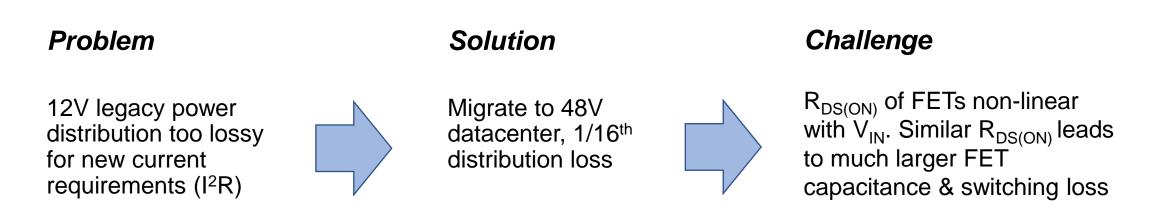

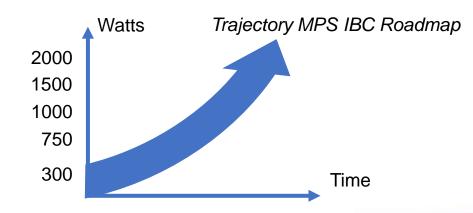

## **The Demand for More Power**

As demand for cloud computing, AI applications, and high-power processors/accelerators grows datacenters are evolving to accommodate new high-power requirements.

Power providers *must* adopt new technologies to improve efficiency and provide more power in the same form-factor.

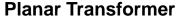

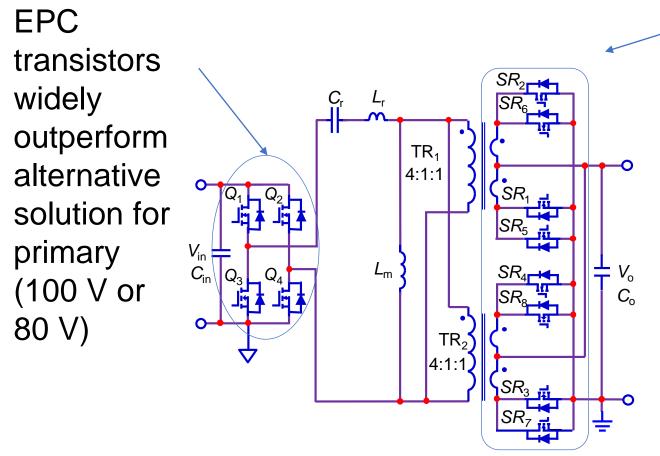

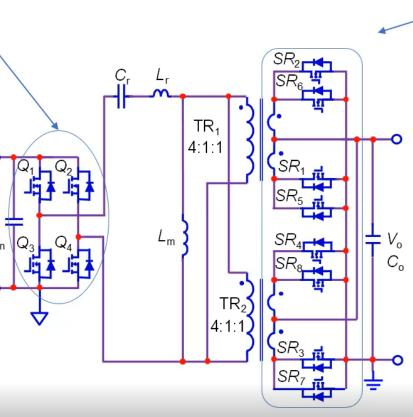

# Primary-side GaN FET

#### **Primary & Secondary-side FETs**

Improved FOM for R<sub>DS(on)</sub>\*Q<sub>G</sub> Smaller FET sizes for better

form-factor

Significant decrease of start-up stress by MP2981 soft-start control. Can power-on under severe conditions

## **MPS Design Principles**

- Excellent Heat Dissipation for high-efficiency & density

- Low-height, easy to fit into existing server form-factor

#### **Synchronous Rectifier**

- Accusense<sup>™</sup> current sensing for accurate sensing (+/-2%) without significant loss from sense resistor or passive network

- Designed as counterpart to controller for optimized control & telemetry

#### **Dedicated LLC Controller**

- Adjusts Frequency for Best Efficiency

- MTP for fine-tune control

- I<sup>2</sup>C/PMBus for fault and performance monitoring

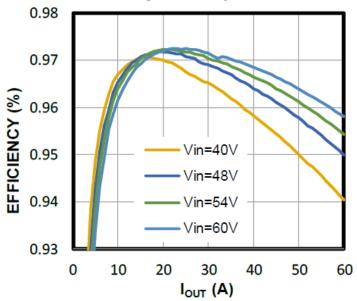

## **MPS 10:1 IBC – MPC1100A**

| Specifications  | Min | Тур     | Max | Units |

|-----------------|-----|---------|-----|-------|

| Vin             | 40  | 54      | 60  | Volts |

| Vout            |     | 5.4     |     | Volts |

| Pout            |     | 300     |     | Watt  |

| Size(X & Y)     |     | 18 x 27 |     | mm    |

| Total Thickness |     | 6.1     |     | mm    |

#### Benefits:

- 1. Common Footprint

- 2. Soft-switching for all FETs

- 3. OVP/UVP/OCP/OTP

- 4. PMBus/I<sup>2</sup>C Compatible

- 5. Programmable soft-start

Efficiency vs. Output Current

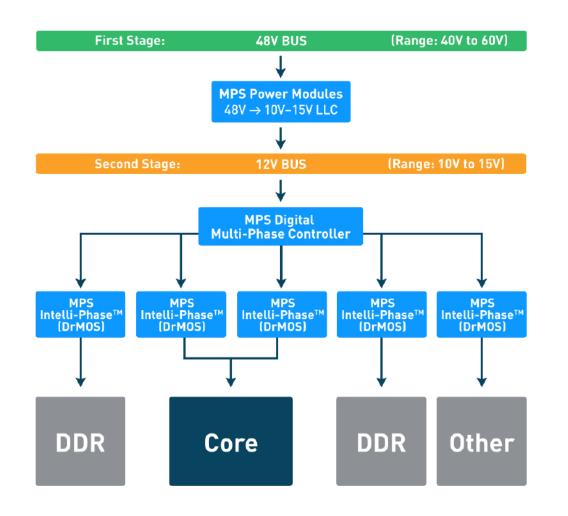

#### The Next Trend: $48V \rightarrow 12V$ Conversion, 4:1 LLC

Why 48V  $\rightarrow$  12V? Key Reasons:

- 1. System Development. Easiest method for 48V migration can reuse an existing 12V system

- 2. Solution Size. 4:1 conversion can be placed in smaller form-factor, improving system layout

Datacenter power products follow trend for higher power density & efficiency. Regardless of winding ratio or topology new techniques and technologies are vital to maintain relevance.

# The electrical challenge

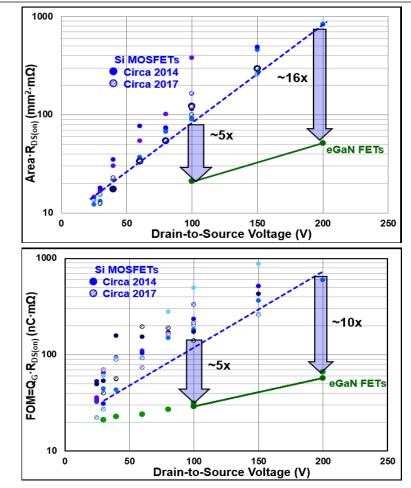

## **The Electrical Advantage**

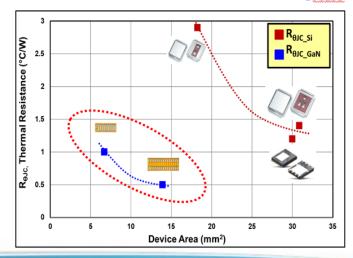

- The theoretical on-resistance versus blocking voltage of a GaN transistor is more than three orders of magnitude lower than that of silicon

- Using the R<sub>DS(ON)</sub>·Q<sub>G</sub> figure of merit, GaN devices show an improvement between almost three times to more than ten times that of silicon, with larger advantages at higher voltage

Lidow, Alex; de Rooij, Michael; Strydom, Johan; Reusch, David; Glaser, John. GaN Transistors for Efficient Power Conversion (pp. 43-44). Wiley. Kindle Edition. s

## LLC DCx @1MHz

#### High Density applications operate at fsw ~ 1 MHz

EPC transistors offers competitive performance for 12 V output with ½ of the size vs Si MOSFET

| Specificatio<br>n | Min. | Nom.              | Max. | Units |

|-------------------|------|-------------------|------|-------|

| Vin               | 40   | 48, 54            | 60   | Volts |

| Vout              |      | 12                |      | Volts |

| Pout              |      | 300 W –<br>2.5 KW |      | Watt  |

• Shown with 2 paralleled FETs for secondary and for 4:1

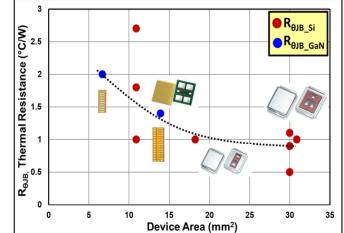

## eGaN FETs for LLC DCx

#### **Primary Side eGaN FET**

| Typical<br>Specificati<br>on                            | EPC2204            | EPC2218               |  |

|---------------------------------------------------------|--------------------|-----------------------|--|

| V <sub>ds,max</sub>                                     | 100 V              | 100 V                 |  |

| R <sub>ds,on</sub>                                      | 4.5 mΩ             | 2.5 mΩ                |  |

| <b>Q</b> <sub>oss</sub>                                 | 25 nC              | 46 nC                 |  |

| $Q_{gd}$                                                | 0.9 nC             | 1.6 nC                |  |

| $Q_{g}$                                                 | 6.4 nC             | 11.8 nC               |  |

| $egin{array}{c} R_{	heta,jc}\ R_{	heta,jb} \end{array}$ | 1 °C/W<br>2.5 °C/W | 0.54 °C/W<br>1.8 °C/W |  |

| _                                                       | 2.5 mm             | 3.5 mm                |  |

| 5 mm                                                    |                    |                       |  |

#### Secondary Side eGaN FET

| Typical<br>Specification                                      | EPC2024              |  |  |

|---------------------------------------------------------------|----------------------|--|--|

| V <sub>ds,max</sub>                                           | 40 V                 |  |  |

| $R_{ds,on}$ at 4.5 $V_{GS}$                                   | 1.2 mΩ               |  |  |

| Q <sub>oss</sub>                                              | 45 nC                |  |  |

| $Q_{gd}$                                                      | 2.4 nC               |  |  |

| $Q_g$                                                         | 18 nC                |  |  |

| $egin{aligned} & R_{	heta,jc} \ & R_{	heta,jb} \end{aligned}$ | 0.4 °C/W<br>1.1 °C/W |  |  |

|                                                               |                      |  |  |

ŝ

2.0

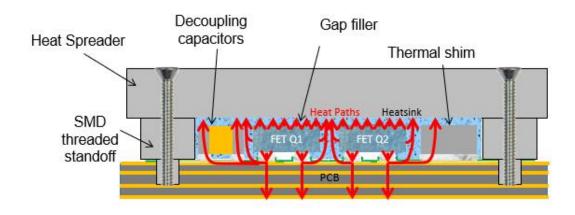

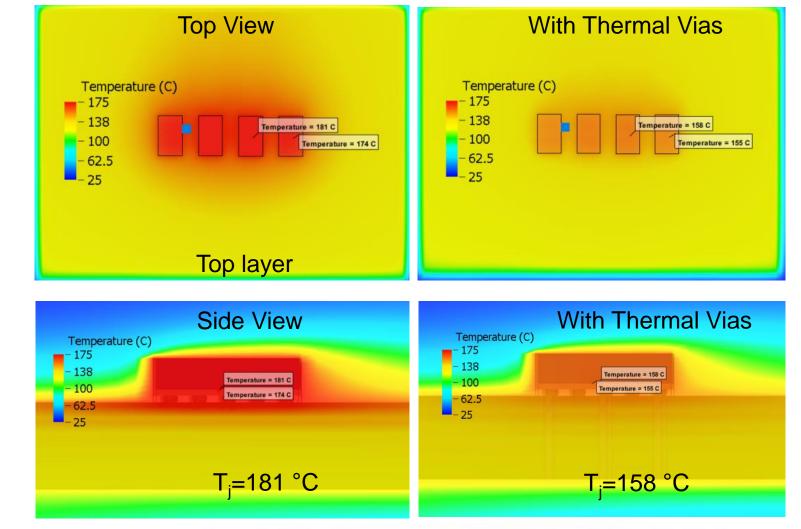

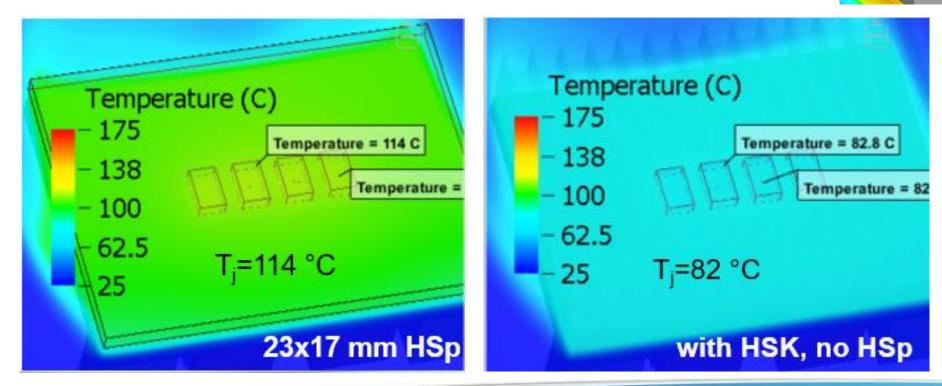

# **The Thermal Challenge**

How to achieve optimal thermal performance:

- Thermal Vias

- Gap pads

- Heat-spreader (dual sided cooling)

#### Heat transfer to PCB R<sub>OJBoard</sub>

#### Heat transfer to top Si substrate R<sub>OlCase</sub>

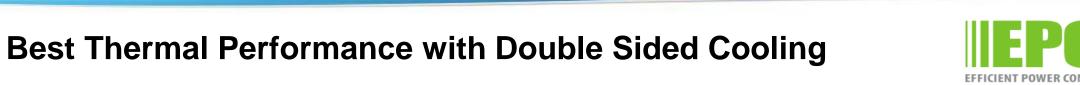

# Vias Construction (VIPPO)

- Vias are

- non-conductive filled (better CTE vs board)

- plated over

- hole diameter (typical) = 7.8 mil

- annular ring = 13.8 mil diameter min.

- wall thickness = 0.78 mil per IPC standard class 2

- Used for under bump and close to component pads

- Used for up to 2 oz copper thickness

Practical Example layout showing vias for EPC2204

#### Power Conversion Technology Leader epc-co.com

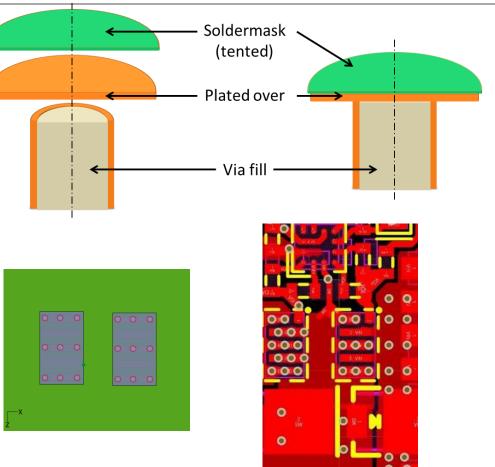

## **Effect of Vias On Thermal Performance**

- Vias improve heat conduction into the board

- High thermal conduction path into the FR4 insulating layers

- Use heat spreading in copper layers

- Board design without vias has ~18% higher FET temperature rise

Simulations with EPC2204, LLC application 750W, 6 layers 2oz PCB

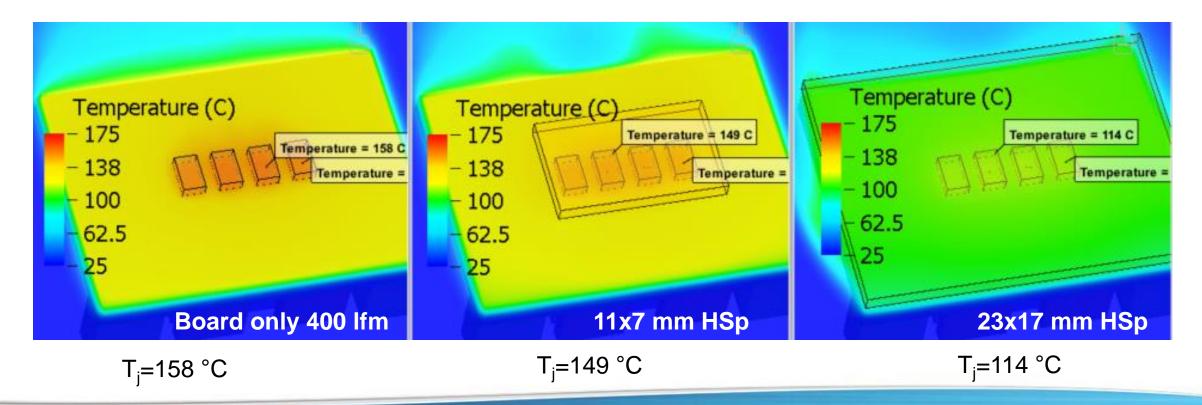

## **Effect of Heat-Spreader Size**

- Larger area heat-spreader is more effective ~52×A<sub>FETs</sub>

- Small area heat-spreader (~13×A<sub>FETs</sub>) insufficient for optimal heat spreading

### **High Performance TIM is Recommended**

- Case A

- TIM material: 0.3 mm T-Global A1760 with  $\kappa = 17.6W/m.K$

- Case B

- TIM material: 0.2 mm,  $\kappa = 3 W/m$ . K

| Configuration                             | Case A             |                  | Case B                                     |                | Increase |

|-------------------------------------------|--------------------|------------------|--------------------------------------------|----------------|----------|

| Configuration                             | $T_{J}(^{\circ}C)$ | , Δ <b>Τ(°C)</b> | $T_{J}\left( ^{\circ }\mathcal{C} ight)$ , | <b>Δ</b> Τ(°C) | (°C)     |

| Cu heat-spreader (23x17mm)                | 114                | 89               | 121                                        | 96             | + 7      |

| Heatsink (3.5 mm total)                   | 82                 | 57               | 90                                         | 65             | + 8      |

| Heat-spreader +Heatsink<br>(4.5 mm total) | 77                 | 52               | 86                                         | 61             | + 9      |

## **Effect of Heatsink**

Thermal heat dissipation from the top can be further increased by using a heat sink instead of the heat spreader

#### Power Conversion Technology Leader

## **Thermal Challenge**

- 1. Distance between heatsink and FET is critical for performance: 1mm standoffs is typically used

- 2. Area of heatsink is critical to improve heat spreading effect

The challenge is to find low profile components that go around the FET to allow the heat sink mounting

# The Manufacturing challenge

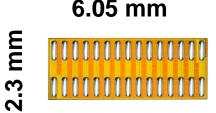

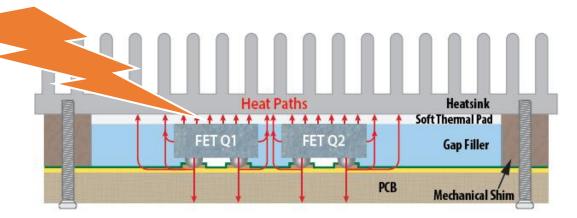

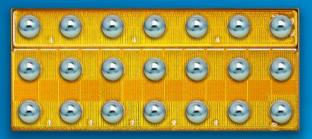

# Wafer Level Chip Scale Package (WLCSP)

• EPC devices are available in WLCSP

This allows for the smallest PCB area utilization and highest power density

#### a reliable electrical, thermal, and mechanical connection

• The quality of the solder bump interfacing

• The top of the device is the Silicon substrate, it is not part of the active device. However, it is connected to the source potential, so care must be taken when attaching to a heat-sink

## Wafer Level Chip Scale Package

the eGaN device to the PCB is crucial for EPC2023: 6.05 mm x 2.3 mm

MPS and EPC are pushing the limits of power density and power efficiency for datacenters 48V power

- MPC1100A is the first in a series ... more to come!

- EPC eGaN enables MPS roadmap where Si is reaching its limits

How To GaN Video Series

epc-co.com

**3<sup>rd</sup> Edition Textbook**

#### eGaN<sup>®</sup> FETs and ICs

Evaluation Kits