# Robustness and reliability aspects of SiC power devices

# Peter Friedrichs, Infineon Technologies AG

# Agenda

1 2 3

SiC reliability: gate oxide, cosmic ray aspects and body diode performance

SiC Product release process and robustness validation approach

Key takeaways

### Gate oxide (GOX) requires special attention in SiC MOSFETs

SiC has higher

blocking capability

(0.3 MV/cm Si vs. 3.0 MV/cm SiC)

4H-SIC

Si

1015

Doping Concentration (cm<sup>-3</sup>)

**Higher fields**

in blocking state

1016

1017

1014

(V/cm)

Critical Electric Field for Breakdown

106

SiC has a larger bandgap (1.1 eV Si vs. 3.2 eV SiC)

FIT rates under nominal operating conditions

GOX stress induced by V<sub>DS</sub> in blocking mode as well

Copy right © Infineon Technologies AG 2021. All rights reserved.

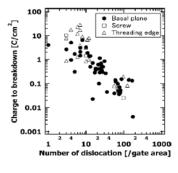

SiC has higher defect density in substrate and in GOX

Higher risk of early GOX breakdown

Measures to sort out affected devices required to meet FIT rates

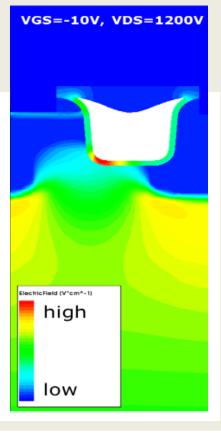

### Oxide in SiC MOSFET devices

## Oxide in SiC MOSFET devices

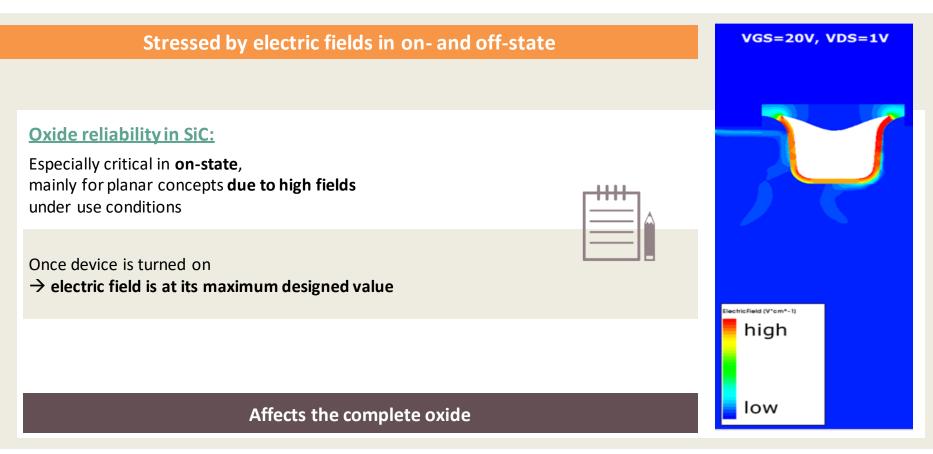

#### Stressed by electric fields in on- and off-state

Important and more challenging for Trench concepts, but it has **less impact** under nominal use conditions **compared to the on-state**

Max. field achieved at the full rated  $V_{DS}$  only (1200 V for lead types)

#### $\rightarrow$ Real application:

mission profile based cumulated **stress lower compared to on-state** (e.g. In case of a DC link voltage of 800 V)

Just a small area of the oxide is stressed

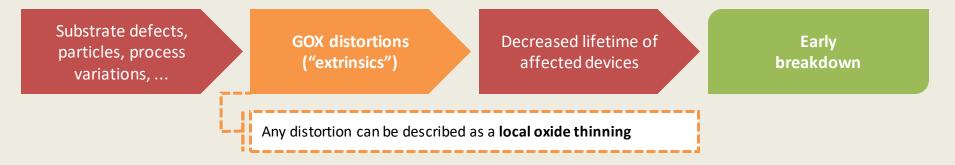

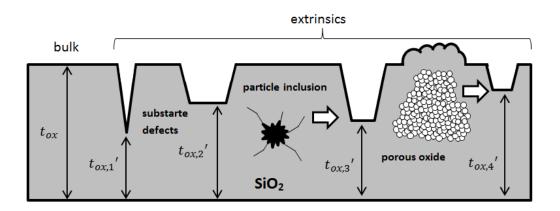

# Effect of high gate oxide defect density on SiC MOSFETs' stability : Extrinsic challenge

The thinner the GOX, the higher is the electric field at a certain gate bias and the lower is the time to breakdown

# Effect of high gate oxide defect density on SiC MOSFETs' stability: Weibull Plot characterization

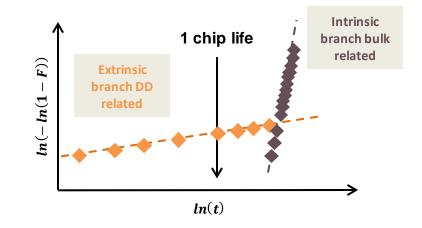

Failure probability of Time-Dependent-Dielectric-Breakdown (TDDB) <u>Distribution is described in a **Weibull Plot**</u>

After an end of life test of a larger number of devices, the **failure rate over time is plotted**

# GOX failure probability typically determined by the extrinsic branch

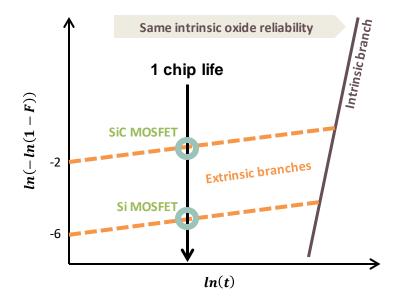

# Effect of high gate oxide defect density on SiC MOSFETs' stability: Analyzing failure statistics

How does Weibull Plot look like for SiC and Si MOSFETs?

(same area and gate oxide thickness)

At the end of processing (EOP): SiC MOSFETs → much larger extrinsic defect density

Failure probability: up to 4 orders of magnitude higher

Many decades of development away to **drop extrinsic GOX defect density below 1% at EOP** in modern SiC MOSFETs

< 0.001% (10 ppm) or < 0.0001% (1 ppm) is needed!

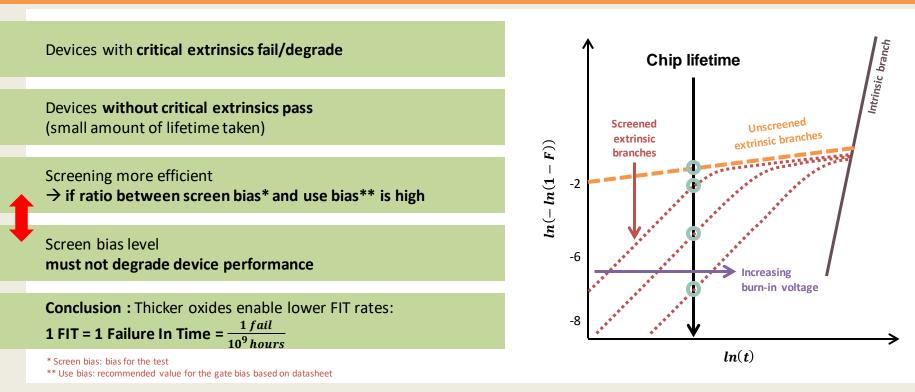

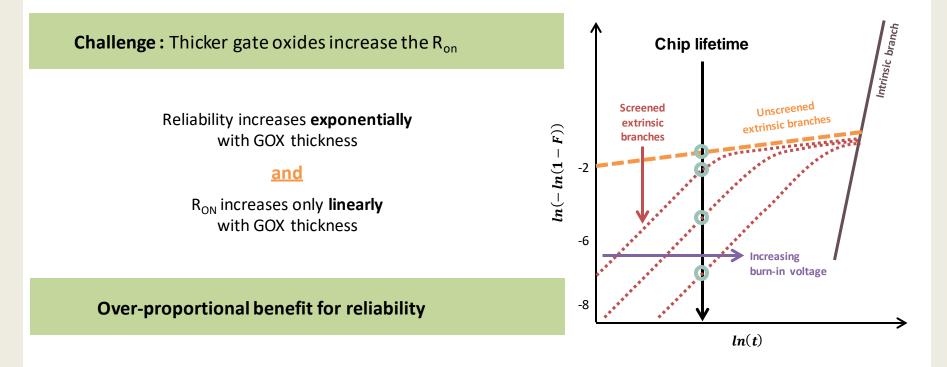

#### How can we get rid of devices with critical extrinsics?

#### Devices are "aged" by an electric screen pattern at the gate

#### How can we get rid of devices with critical extrinsics?

#### Devices are "aged" by an electric screen pattern at the gate

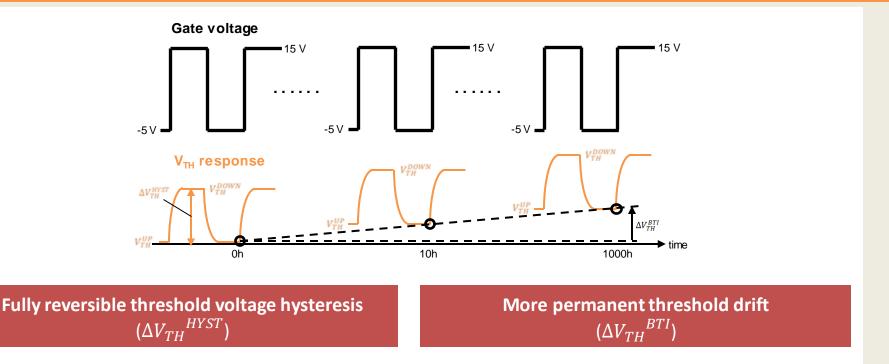

### Drift of the threshold voltage in SiC MOSFETs: Static contribution

2 quasi-static Bias Temperature Instability (BTI) components exist

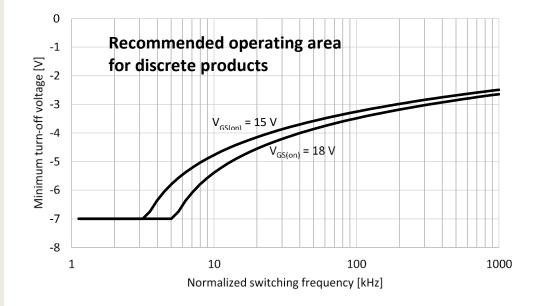

### Drift of the threshold voltage in SiC MOSFETs: Dynamic contribution\*

By switching triggered, a 3<sup>rd</sup> Bias Temperature Instability (BTI) components exist

\*H. Jiang, X. Zhong, G. Qiu, L. Tang, X. Qi and L. Ran, "Dynamic Gate Stress Induced Threshold Voltage Drift of Silicon Carbide MOSFET" IEEE Electron Device Letters, vol. 41, no. 9, pp. 1284-1287, Sept. 2020

Triggered by switching device, a **third** effect needs to be taken into account when  $V_{TH}$  effects are quantified

Amount of  $V_{TH}$  drift mostly **influenced by switching frequency** and **chosen bias for turning off the MOSFET**, partially also by turn-on bias at the gate

Infineon provides an Application Note (AN2018-19) that describes how to make sure to stay within the safe operating area. Magnitude of the effect needs to assessed for a certain technology and is in the focus of optimization targets.

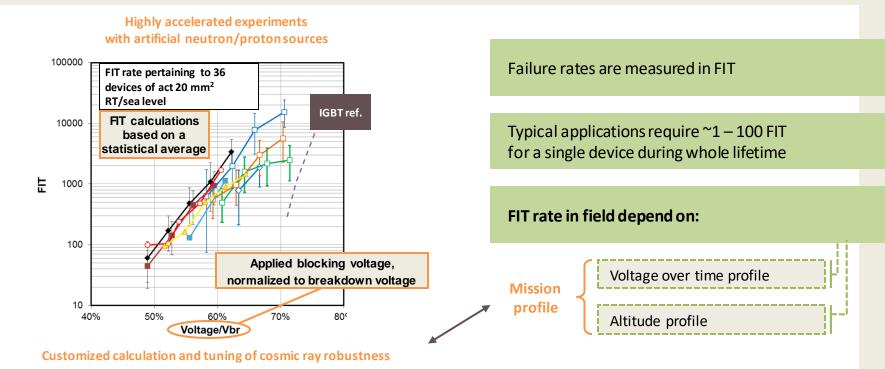

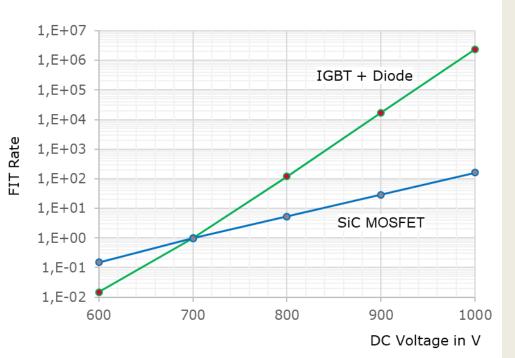

# SiC reliability: cosmic ray aspects

#### Cosmic ray failure rates: Situation for SiC

#### Cosmic ray: radiation caused by extraterrestrial sources that causes fatal device fails

### Cosmic ray and SiC: Impact on real designs and difference from Si

SiC MOSFET: **smaller active area** than Si IGBT/diode (same current)

SiC MOSFET: **no need of free wheeling diode** (which contributes to CR FIT)

Si FIT rate: larger descrease with rising  $T_j$  (compared to a SiC MOSFET)

Graph represents typical CR FIT values for a 200 A Si- and SiC-based half-bridge at 25°C and sea level

# SiC reliability: body diode performance

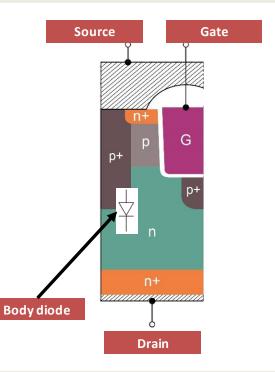

### MOSFET body diodes: Structure and requirements

#### Vertical power MOSFETs (planar and trench types)

These contain a diode that allows conduction in the 3<sup>rd</sup> quadrant and can be used as freewheeling diode – **body diode**

Since  $V_F$  of pn-based diodes in SiC is high  $\rightarrow$  It is recommended to use synchronous rectification

#### Turn on the channel after a short dead time

In this mode, channel carries most of the current and low losses (comparable to the  $1^{st}$  quadrant) are secured

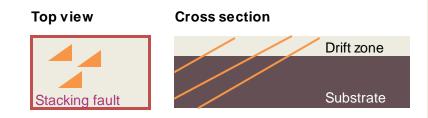

### The potential degradation in bipolar SiC elements: Recombination induced increase of $R_{DS(on)}$ and $V_{SD}$

Bipolar degradation might affect all SiC MOSFET technologies

Effect is defect-driven and related to defects of **substrate material**

Statistical effect: devices without these defects will not have bipolar degradation effect

Effect **only triggered by bipolar operation** (body diode conducting) **and saturates** after limited time

Driven by electron hole recombination, stacking faults grow in the drift zone and act as a barrier for current

#### What is the impact of bipolar degradation in application?

Drift of  $R_{DS(on)}$  and diode  $V_{SD}$  over operation time due to reduction of effective active area of the device

No other major properties will change (e.g.  $V_{br}$ ,  $V_{GS(th)}$ , ...)

#### Bipolar degradation: Countermeasures

Infineon's strategy to tackle the effect

Applying screening approach (as for gate oxide extrinsics) as long as defect density is above a critical threshold

Dropping down defect density to avoid stacking fault growth

Avoiding recombination at stacking faults

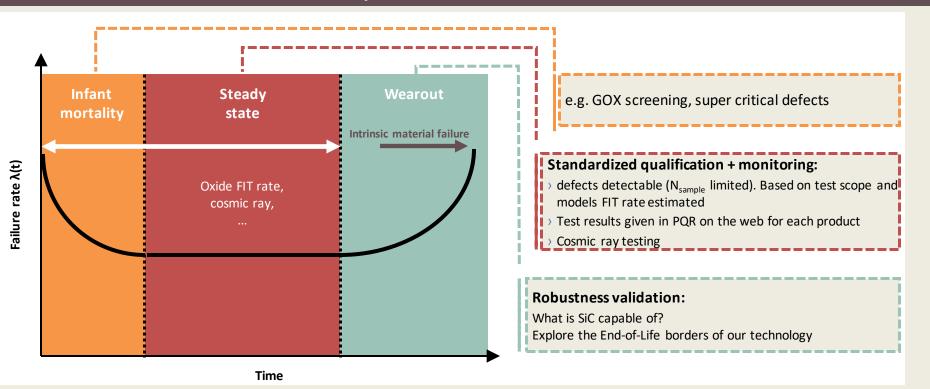

# Product release process and robustness validation approach

#### Robustness and bathtub curve: Short introduction

#### **Exploration "End-of-life"**

#### Robustness validation for Infineon's power modules

| Test     | Test conditions                                                                            | Serial<br>release:<br>stress time |  |

|----------|--------------------------------------------------------------------------------------------|-----------------------------------|--|

| HTRB     | V <sub>DS</sub> = 1080 V<br>T = 150°C                                                      | 1000h                             |  |

| HTGS     | V <sub>DS</sub> =0V<br>V <sub>GS</sub> =+20V/-20V<br>T=150°C                               | 1000h                             |  |

| H3TRB    | V <sub>DS</sub> = 80 V<br>T = 85℃<br>rH = 85%                                              | 1000h                             |  |

| HV-H3TRB | V <sub>DS</sub> = 960 V<br>T = 85℃<br>rH = 85%                                             | 1000h                             |  |

| AC HTC   | $T_{cycle} = -20^{\circ}C/85^{\circ}C$<br>rH = 93%<br>$V_{DS} = typ.$ (AC)<br>f = typ. kHz | 21d<br>(only SiC)                 |  |

#### Robustness validation for Infineon's discrete devices

| Stress test                               | Test conditions                                                                                                                                         | Duration |                                      |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------|

| HTRB                                      | V <sub>DS</sub> = 1200 V; T <sub>vj</sub> = 175°C; V <sub>GS</sub> = 0 V                                                                                | 2000 h   | )                                    |

| HTRB w/ negative voltage (blocking state) | V <sub>DS</sub> = 1200 V; T <sub>vj</sub> = 175°C; V <sub>GS</sub> = -10 V                                                                              | 2000 h   | Extended                             |

| HTRB w/ negative voltage (blocking state) | V <sub>DS</sub> = 1100 V; T <sub>vj</sub> = 175°C; V <sub>GS</sub> = -15 V                                                                              | 1000 h   | <ul> <li>HTRB<br/>section</li> </ul> |

| HTRB w/ pre-stressed parts                | $V_{DS}$ = 960 V; $T_{vj}$ = 175°C; $V_{GS}$ = 0 V w/ initial 0x and 10x short-circuit stressed parts                                                   | 1500 h   |                                      |

| HTGS                                      | $V_{GS}$ = +20/-20 V constant; $T_{vj}$ = 175°C                                                                                                         | 2000 h   | Extended                             |

| HTGS w/ pre-stressed parts                | $V_{GS}$ = +20/-20 V constant; $T_{vj}$ = 175°C w/ initial 0x and 10x short-circuit stressed parts                                                      | 1000 h   | HTGS<br>section                      |

| HV-H3TRB                                  | V <sub>DS</sub> = 1200 V; T <sub>a</sub> = 85°C; rH = 85%                                                                                               | 2000 h   |                                      |

| Dynamic H3TRB                             | T <sub>a</sub> = 85ºC; rH = 85%; V <sub>DClink</sub> = 960 V; V <sub>GS</sub> = +15 V/0 V; IL peak<br>= 16 A; f <sub>SW</sub> = 25 kHz; dv/dt = 70 V/ns | 1000 h   | Humidity<br>section                  |

| Dynamic Reverse Bias ( DRB)               | T <sub>a</sub> = 25°C; V <sub>DC link</sub> = 960 V; V <sub>GS</sub> = +15 V/-5 V;<br>dv/dt ~ 200 V/ns; f <sub>SW</sub> = 100 kHz                       | 1000 h   |                                      |

#### Key takeaways

- There are three main aspects that make SiC MOSFET systems different from silicon:

- Larger bandgap

- Higher blocking capability

- Higher defect density, which is why stricter measures are required to assure long-term reliability

- There are dedicated measures in place to overcome the challenges posed by SiC such as gate oxide and cosmic ray aspect as well as body diode performance

#### I'm happy to answer your questions now!