## PwrSoC at an Inflection Point: from R&D to Market Relevance

Francesco Carobolante IoTissimo® LLC

## Agenda

- Where are we in the PwrSoC journey?

- Drivers and Enablers

- The key parameters

- Efficiency

- Size

- Cost

- Conclusions

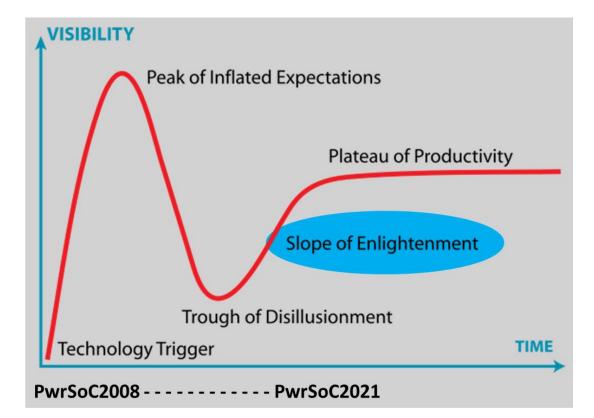

## Where are we in the technology cycle?

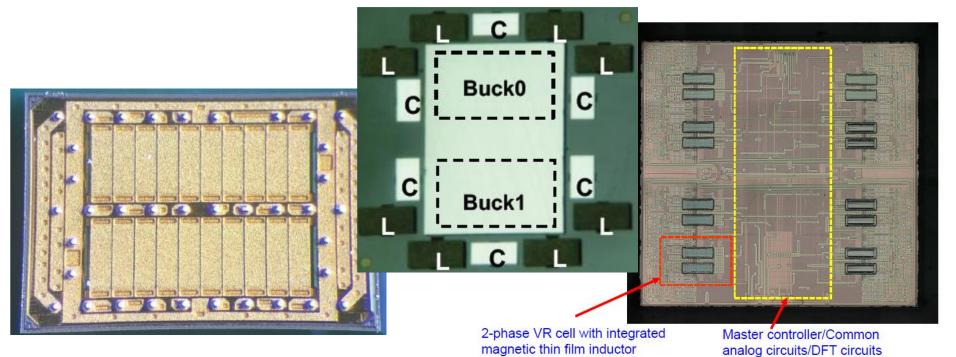

#### IBM Research

4

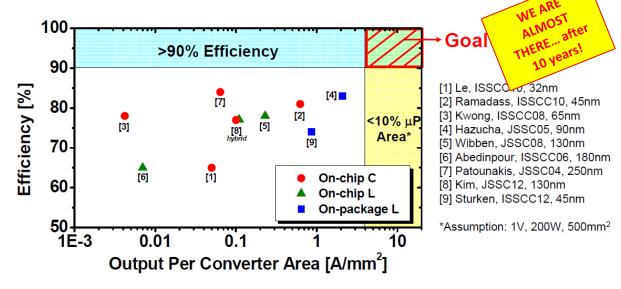

#### Previous Work on On-Chip Voltage Conversion

#### Deep Trench Capacitors for Switched Capacitor Voltage Converters

<u>Jae-sun Seo,</u> Albert Young, Robert Montoye, Leland Chang

IBM T. J. Watson Research Center

For full history of PwrSoC see APEC 2020 presentation: F. Carobolante "Power Supply on Chip as a key enabler for high performance applications"

- Typically 3 approaches : (1) linear (2) switched-capacitor (3) buck

Linear regulator not suitable for high-voltage power delivery

- Difficult to achieve high efficiency & current density simultaneously

# Ferric, Dialog and Huawei show fully integrated PwrSoC's

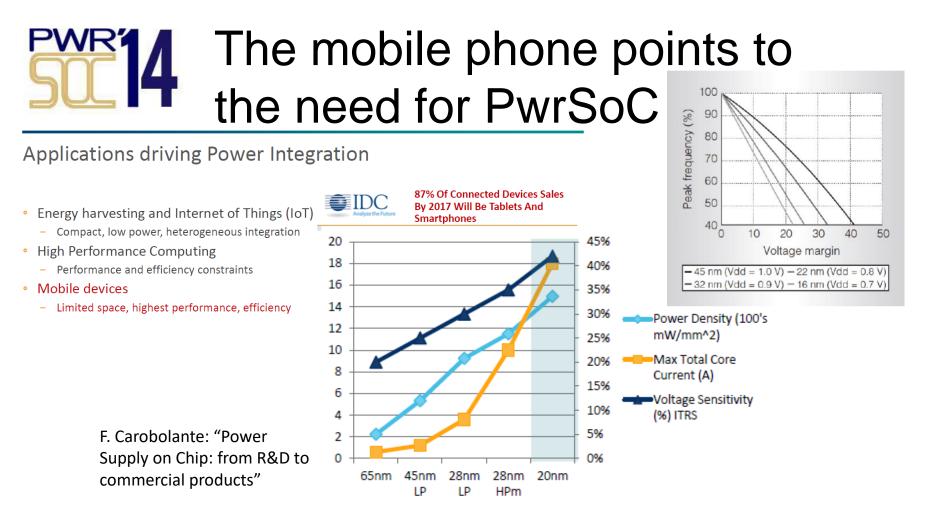

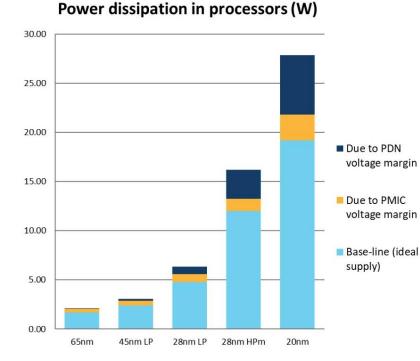

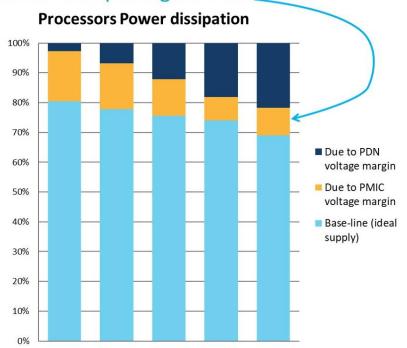

#### Inefficiency grows due to lower load impedance and fast transients

Gains achievable from Power Management "outside" the package are limited

65nm

45nm LP

28nm LP

28nm HPm

20nm

## Power Dissipation grows more than quadratically with supply voltage (~V<sup>3</sup>)

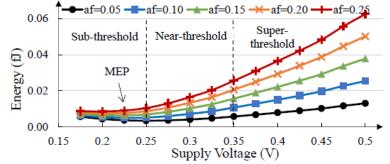

Figure 4. Energy consumption of a 20-stage inverter chain versus supply voltage at different activities factors (af) for FinFET 7nm normal  $V_{th}$  device.

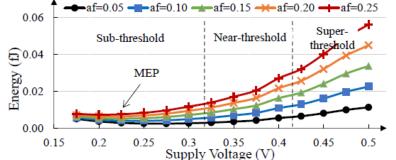

Figure 6. Energy consumption of a 20-stage inverter chain versus supply voltage at different activities factors (af) for FinFET 7nm high  $V_{th}$  device.

For <10nm processes, SoC power increases by 3% for every 10mV increase in supply voltage!

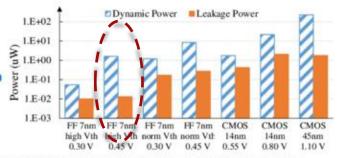

Dynamic and leakage power consumptions of the c432 benchmark for different standard cell libraries.

Qing Xie et al. "Performance Comparisons between 7nm FinFET and Conventional Bulk CMOS Standard Cell Libraries," IEEE Transaction on Magnetics, 2015

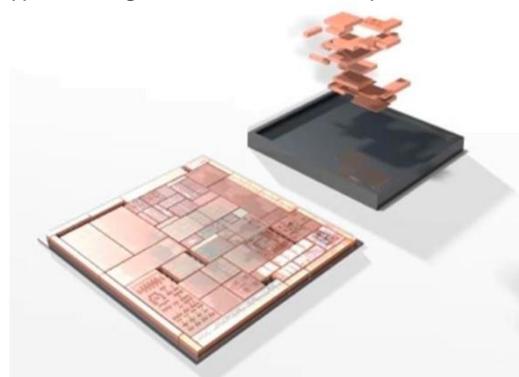

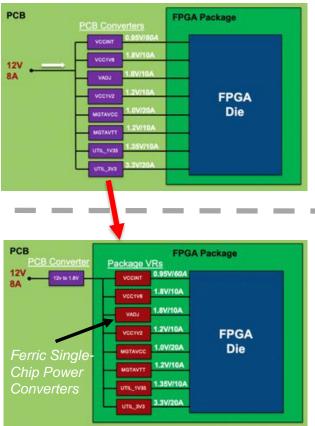

The evolution of high-performance systems to a "chiplet" approach and heterogeneous integration is facilitating the integration of the "PMIC chiplet," since a two-stage approach to regulation becomes mandatory

## Enablers: Convergence of technologies

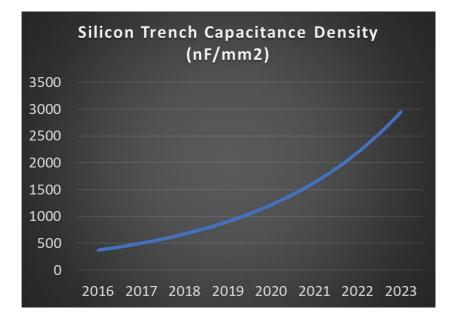

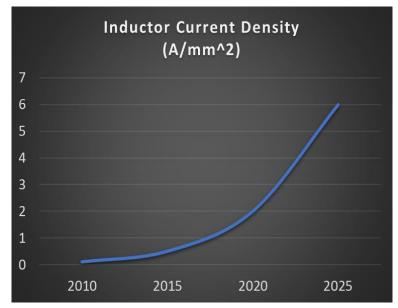

**Deep Trench capacitors & Integrated Inductors**

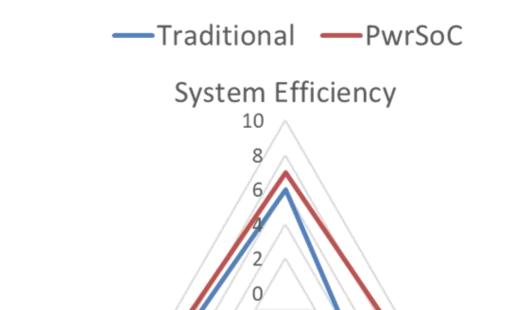

### Value proposition: PwrSoC vs Traditional PMIC

Size

System Cost

## Efficiency

Benefits of PwrSoC:

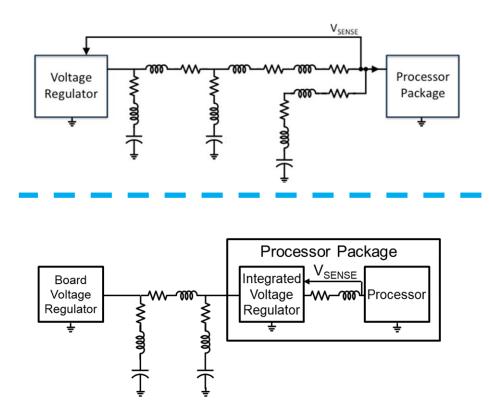

- High bandwidth (> 50MHz) feedback can be placed directly on the processor load

- <u>Broadband</u> supply impedance reduced to <1mΩ</li>

- Drastic reduction of processor supply voltage margins → improved efficiency

- Regulation of resonant impedance peaks from upstream PDN →

- No 3<sup>rd</sup> droop and reduced 2<sup>nd</sup> droop

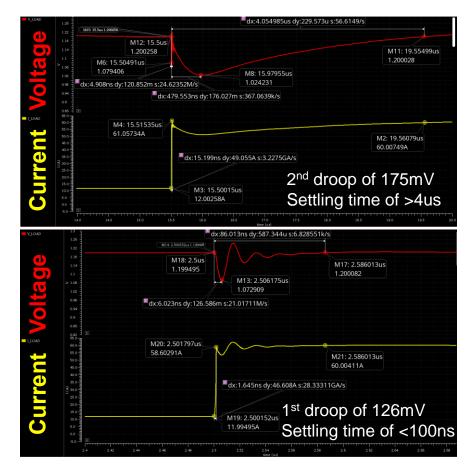

## Power Integrity Comparison

60A Processor Load Step with Mother Board VR

## 60A Processor Load Step with in-Package VR

Courtesy of Ferric Inc.

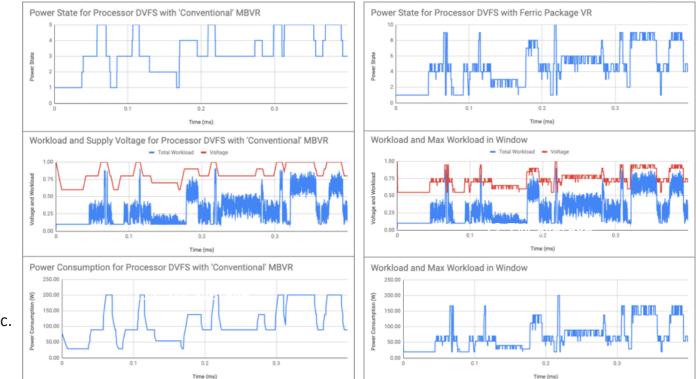

## Fine Grain DVFS

#### Identical Workload and Performance with 35% less power consumption!

#### Courtesy of Ferric Inc.

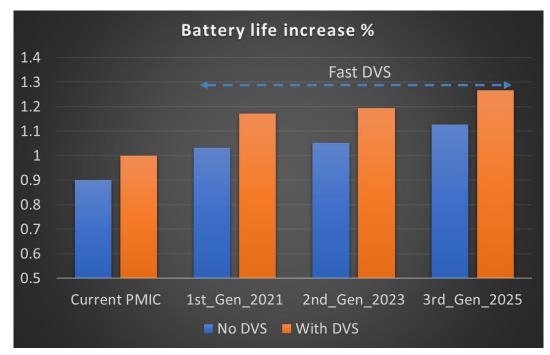

# BATTERY LIFE increase by 3-26% depending on implementation

Note: Above numbers are based on the Google Pixel

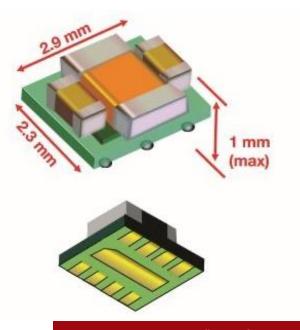

- Shrink power converters to be co-packaged with processors

- Reduce losses associated with high currents through board → socket → package → processor

- Enable delivery of many independently scalable supplies

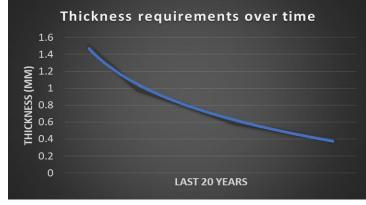

### Size Matters

## Mobile products: typical PMIC area dedicated to SoC's is greater than 200 mm<sup>2</sup>

PC Boards are often skinny and long, making it difficult to optimize routing

Goertek G476 Microphone Diversit FFM Goertek G476 Microphone PMIC ~ 36mm<sup>2</sup> Miscell, PMIC PCB ~ PCB ~ LB Diversity 220mm² 100mm<sup>2</sup> I amsung Shanng 5500 RF Transceive **GNSS** Receiver HB/MB Diversity Samsung Samsund \$2MIS01 Electro-Mechanics Samsung S2D0S05 Samsung Shannon 2244C2 WiFi Module Display Power ST I SM6DSC NFC Secure Management **iNEMO** Inertial IDT IDTP9320S Module

Samsung Galaxy 10e

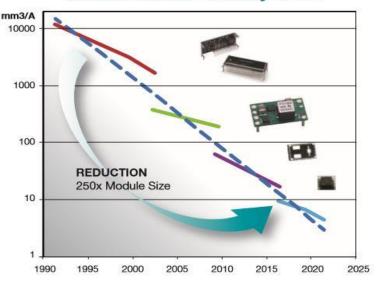

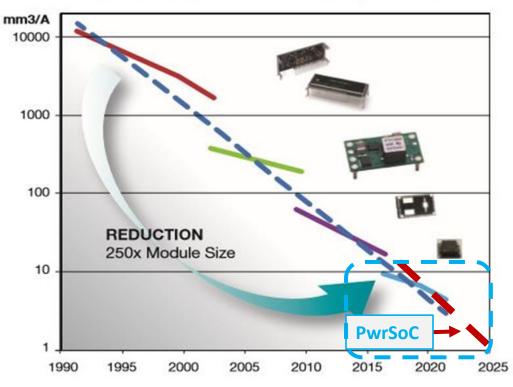

## Current Roadmap for PMIC - State of the Art: MicroSIP (25% Volume Reduction per Year)

From Texas Instruments: "Powerful solutions come in small packages - Innovative SiP power modules simplify and accelerate system development"

**Module Volume Density Trend**

Power modules have paralleled the tremendous downscaling that has taken place in circuitry. In the past 25 years, Tl has brought an average module size reduction of 25 percent annually – and aims to continue this trend.

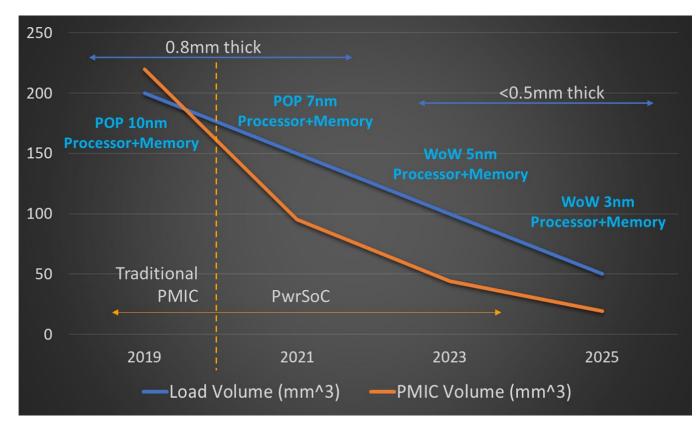

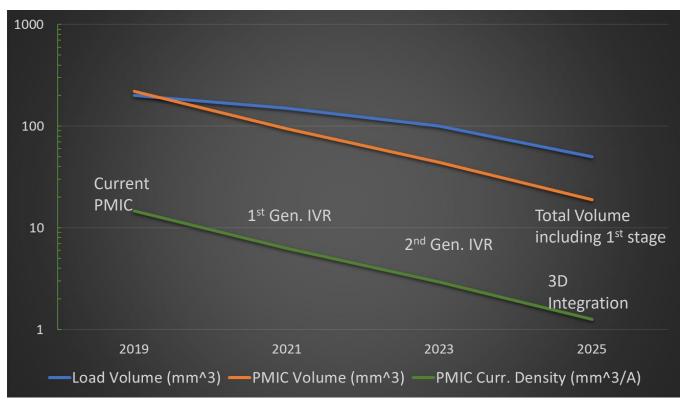

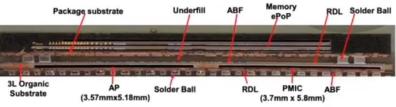

## Volume occupied by Processor and PMIC

## **Density evolution**

#### **Module Volume Density Trend**

## PwrSoC extends the Density trend another decade!

Power modules have paralleled the tremendous downscaling that has taken place in circuitry. In the past 25 years, TI has brought an average module size reduction of 25 percent annually – and aims to continue this trend.

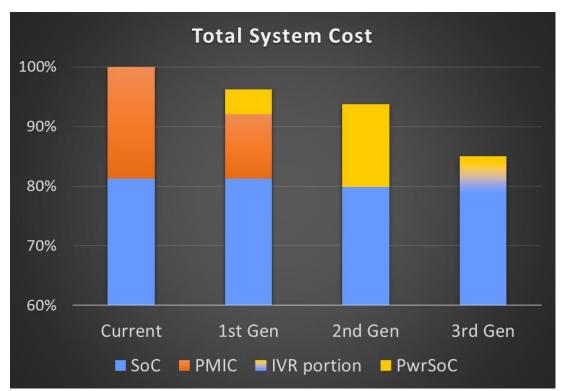

# COST: PMIC Integration reduces system cost by ~15%

## What are the drivers?

- Server platforms (performance!)

- HPC

- Accelerators

- Wearables (there is no room!)

- Smartwatches

- AR/XR glasses

- Mobile (size and efficiency!)

- Smartphone

- Tablets

(ECTC PDC '19, John Lau)

## CONCLUSIONS

Passives need to shrink to enable integration, both for performance and to keep up with packaging requirements

- → Only Silicon passives can deliver *size-performance-reliability*

- We expect to see multiple product lines shipping by the end of 2021

- Evolution of integrated passives, together with advanced packaging technology, will keep the density trend going for many years.

- New Architectures leverage the integration, leading to highfrequency with performance superior to discrete approaches

- A byproduct of such integration is improved reliability (especially in small form factors)

## **QUESTIONS?**

#### Thank you for Listening

francesco@iotissimo.com