# TI Live! AT APEC DESHENG GUO

### HIGH-EFFICIENCY 4-kW SINGLE-PHASE CCM TOTEM-POLE PFC DESIGN

Page 3088

### Agenda

- **Background:** Why choose Totem-pole PFC and common concerns

- 4kW Totempole PFC design and test results

- Efficiency and deadtime influence

- AC drop response

- o Surge test

- o EMI-CE & Thermal test

- Conclusion

## Why choose totem-pole PFC?

## Background

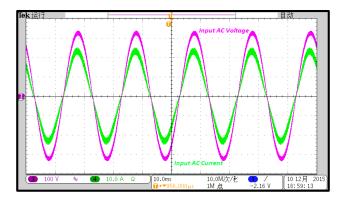

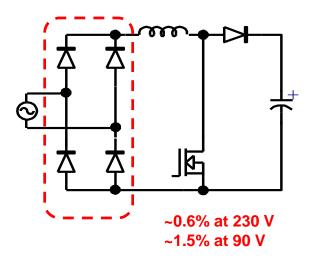

- PFC is widely used in AC/DC applications as a front stage to improve power factor and iTHD.

- Bridge diode loss is a key part in total losses.

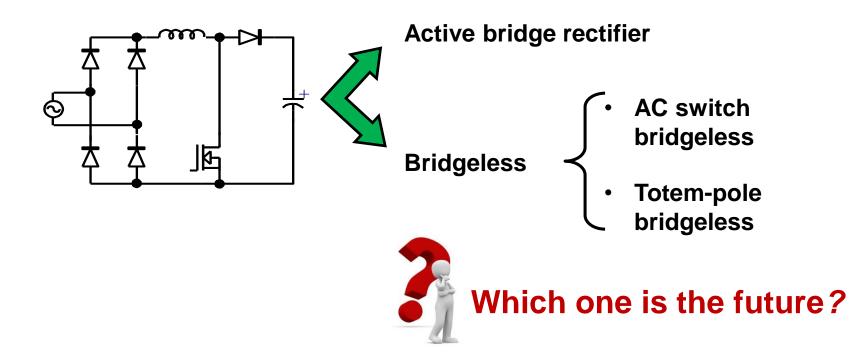

## **Technologies to improve PFC efficiency**

## **PFC technology comparison**

|               | AC switch PFC                                                                   | Totem-pole PFC                                                | Active bridge PFC                                           |

|---------------|---------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------|

| Block diagram |                                                                                 |                                                               |                                                             |

| Details       | 2 silicon diodes<br>2 MOSFETs<br>2 silicon diodes or SiC diodes<br>1 choke coil | 2 <b>GaN FETs</b> or SiC MOSFETs<br>2 MOSFETs<br>1 choke coil | 5 MOSFETs<br>1 silicon diodes or SiC diodes<br>1 choke coil |

| Cost          | Middle                                                                          | Lowest in future                                              | High                                                        |

| Efficiency    | On-time: 2 MOSFETs<br>Off-time: 1 SiC diode + 1<br>silicon diode                | On-time: 1 MOSFET + 1 FET<br>Off-time: 1 MOSFET + 1 FET       | On-time: 3 MOSFETs<br>Off-time: 2 MOSFETs + 1<br>diode      |

|               | ~ <b>98.7</b> %                                                                 | ~99.0%                                                        | ~98.5%                                                      |

### **Common concerns about totem-pole PFC**

- What is the efficiency performance of GaN FETs?

- How is the power stage and control in the **AC drop** test?

- What is the real risk in the **lighting surge** test?

- What is the **EMI/CE and thermal** performance of totem-pole PFC with GaN?

Let's find out these answers in the following slides.

### 4kW totem-pole PFC design and test result

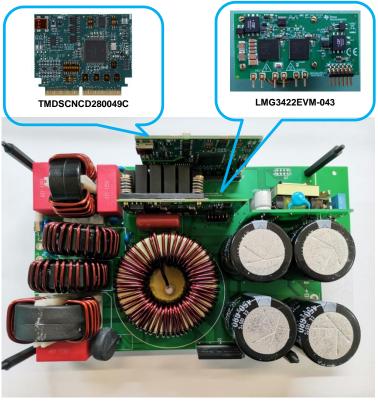

## 4-kW design of a CCM totem-pole PFC

#### **Design parameters**

| Key parameters       | Key specification          |  |

|----------------------|----------------------------|--|

| Input range          | 200 $V_{AC}$ -277 $V_{AC}$ |  |

| Nominal input        | 230 V <sub>AC</sub>        |  |

| DC output voltage    | 400 V <sub>DC</sub>        |  |

| Maximum power        | 4,000 W                    |  |

| GaN HEMET<br>(Q1/Q2) | LMG342xR030                |  |

| Controller           | F280049                    |  |

| Switching frequency  | 50 kHz                     |  |

https://www.ti.com/tool/TIDA-010203

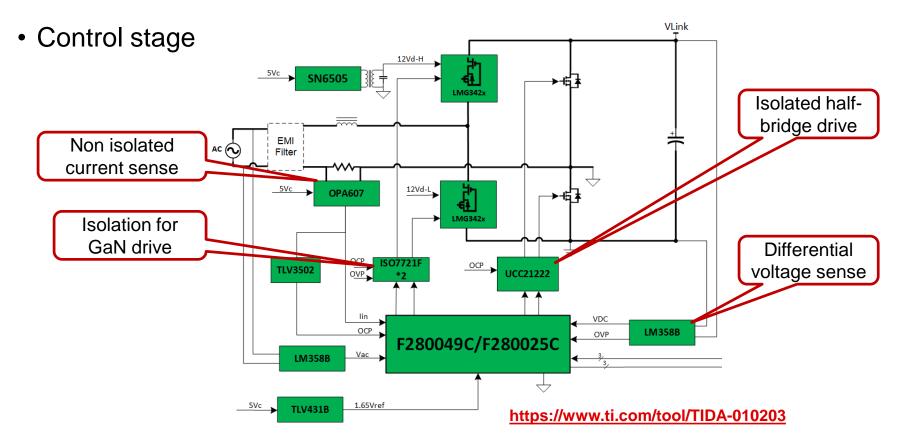

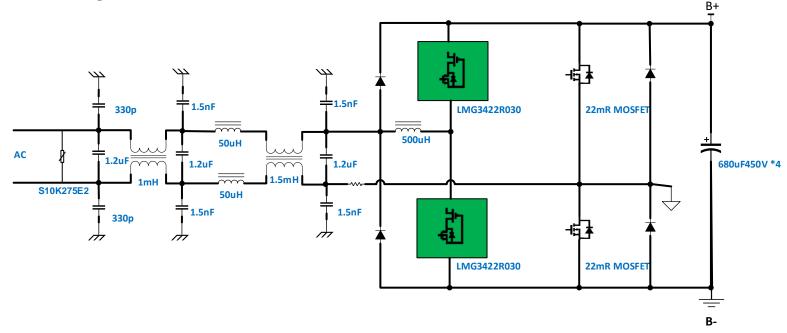

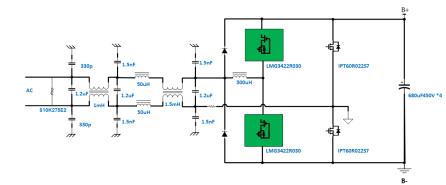

### 4-kW design of a CCM totem-pole PFC

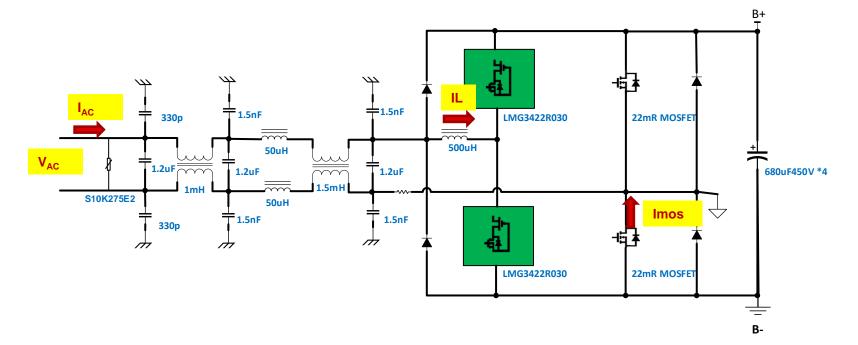

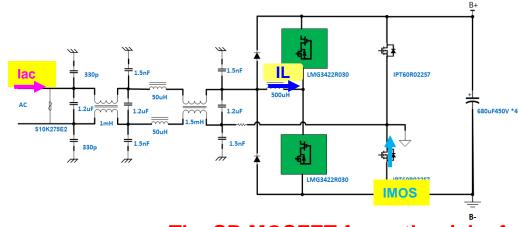

## 4-kW design of a CCM totem-pole PFC

• Power stage

https://www.ti.com/tool/TIDA-010203

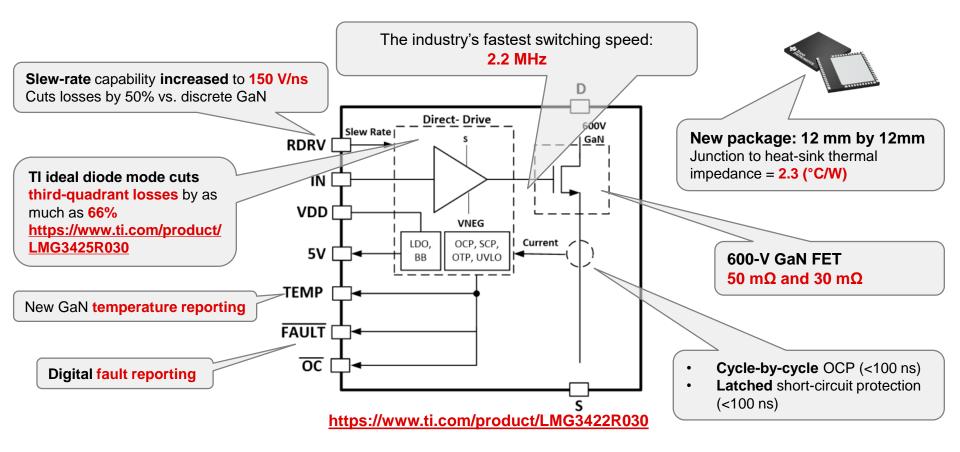

### **TI GaN: integrated driver and protection features**

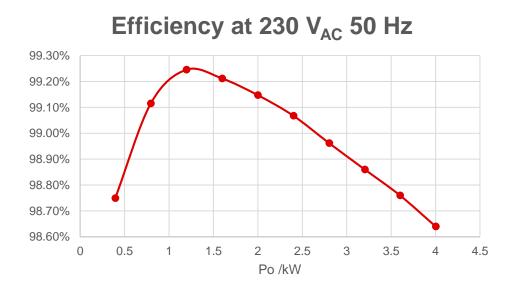

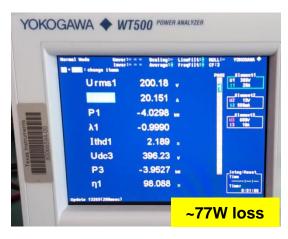

#### Efficiency test results at 230 V

\*Efficiency was measured by WT500 /YOKOGAWA

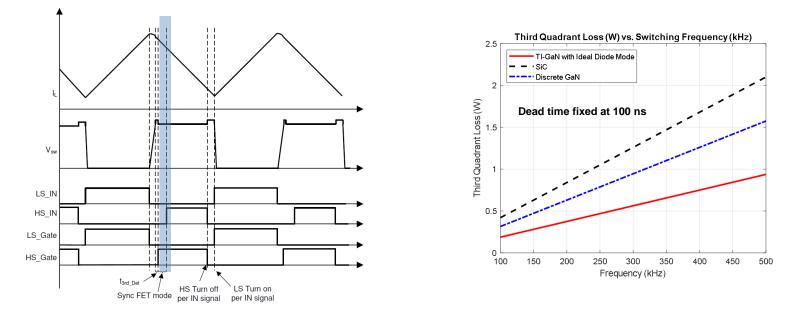

### **Dead-time consideration**

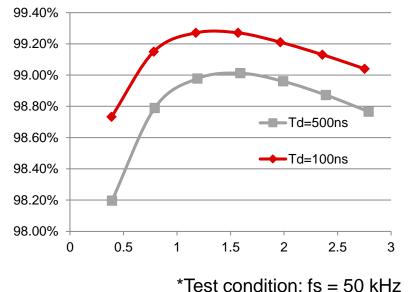

#### Dead-time influence on efficiency

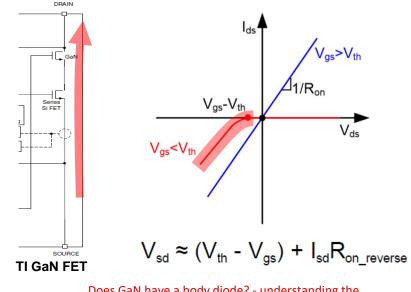

# Simplified behavior of GaN in the first and third quadrants

Does GaN have a body diode? - understanding the third quadrant operation of GaN

## **Dead-time consideration**

### Hard switching off

✓ Time related to switching current

t<sub>deadtime\_optimal</sub> =

✓ Need adaptive control

### Hard switching on

- ✓ Time related to driving strength

- ✓ Fix on the smallest

The <u>Bidirectional High Density GaN CCM Totem Pole PFC Using C2000<sup>™</sup> MCU</u> reference design in the <u>DigitalPower software development kit for C2000<sup>™</sup> MCUs</u> includes an "adaptive control" feature

### **Dead-time consideration**

### Ideal diode mode – LMG3425R030

The LMG3425R030's ideal diode function could save the effort of adaptive control and improve system efficiency. This is helpful in high-frequency solutions.

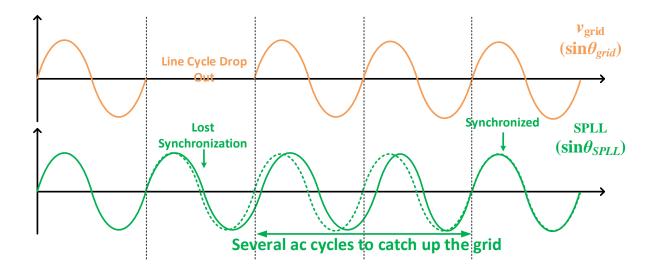

# AC drop

### Key challenges for AC drop:

- SPLL is disturbed and requires several ac cycles to catch up with the grid.

- When ac gets back, SPLL is not synchronized with the grid phase.

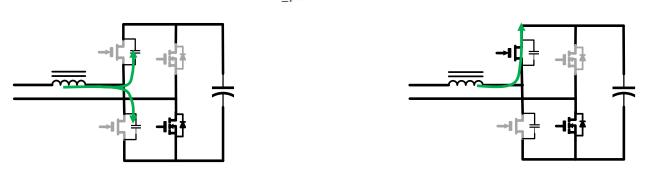

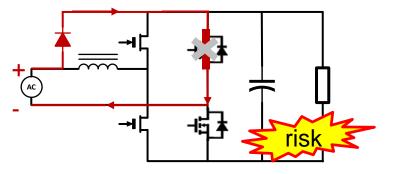

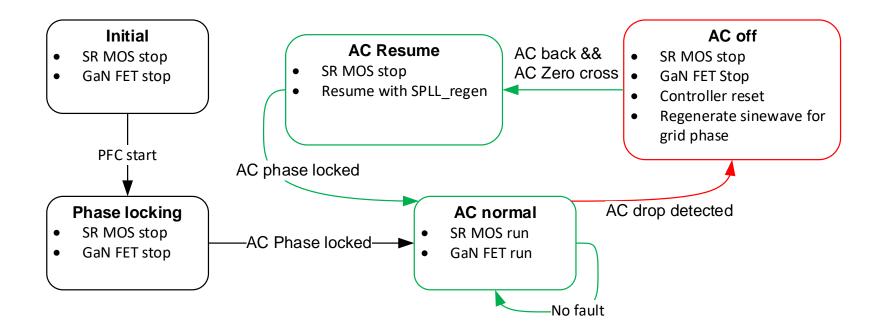

# AC drop

TI's method to solve AC drop:

- Shutdown the SR MOSFET immediate when SPLL loss control or AC voltage out of range.

- Generate an internal sine signal to keep up with grid phase.

- Well-organized state machine ensures the correct trigger of the GaN FET and grid phase.

A mistrigger of the SR MOSFET leads to an input short and current spike

References:

- DigitalPower software development kit for C2000 MCUs

- Design guide of TIDM-2008, Bidirectional Interleaved CCM Totem Pole Bridgeless PFC Reference Design Using C2000 MCUs

### State machine for AC drop monitoring

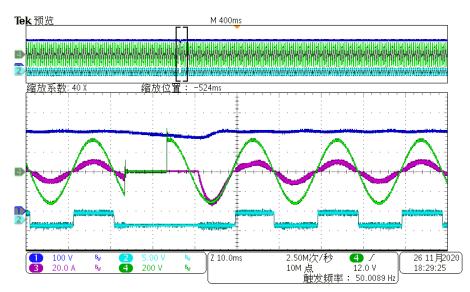

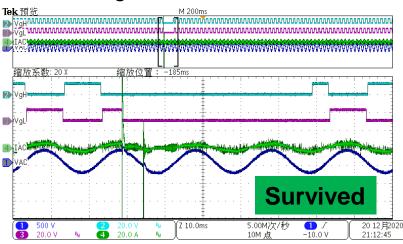

#### Waveform test result

#### AC drop (10ms @ 45 deg)

# Surge test

### Equipment setup:

- 5-kVA isolated transformer

- (Lioncel)

SCU-614A

+ LSG-506CB

+ DN-533P

+ CN533P

### Standard:

- 1.2 μs/50 μs

- $-2-\Omega$  impedance

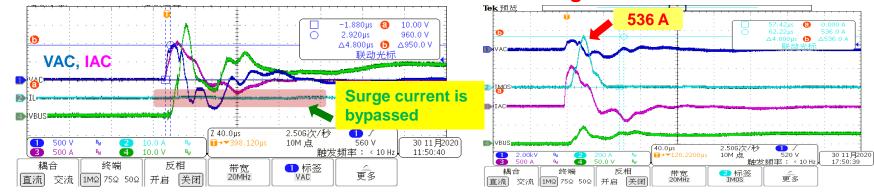

## Surge test

#### EUT parameters and probes

Test without grid AC:

- +3 kV, L to N,

GaN FET is safe.

The SR MOSFET faces the risk of breaking.

## Surge test

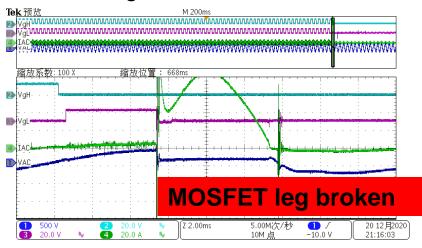

### Test with PFC operating:

- The SR MOSFETs survived at +/-3 kV 90°.

- But SR MOSFETs broke at -4 kV 90°.

#### Surge test at -3 kV 90°

Surge test at -4 kV 90°

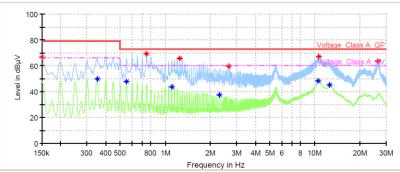

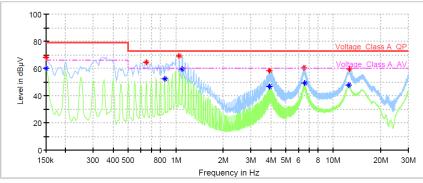

## **EMI CE performance**

CE test setup

#### 230 $V_{AC}$ , load open

#### 230 V<sub>AC</sub>, load 40 $\Omega$

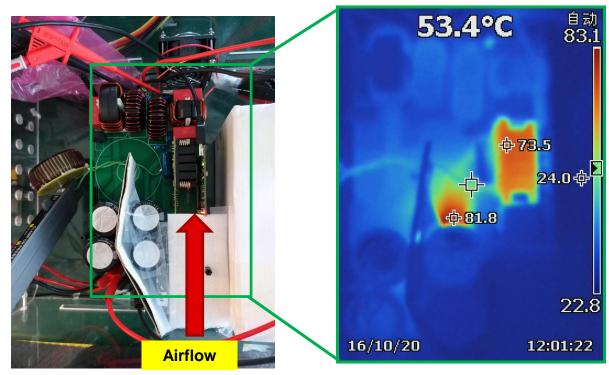

## **Thermal performance**

### **Test conditions**

- 200  $V_{AC},$  4-kW load

- FAN: 27CFM, 24 V 2.64 W; MB60252VX-00C-A99 /SUNON

- Test after 10 minutes

# **Summary**

- 4-kW CCM totem-pole PFC with the LMG342xR030 could achieve 99.2% efficiency.

- AC drop and surge test are validated.

- Lighting surge is not a threat to GaN FETs, but more a risk to the SR MOSFET.

- EMI CEs can be solved in a totem-pole PFC with GaN FET.

- Thermal rise is shown, with common-air force-cooling conditions.

### **THANKS**