# Chiplet integration on active silicon interposer

Applied Power Electronics Conference – Invited talk | 2021, June 9-12<sup>th</sup>

Perceval Coudrain, S. Chéramy, E. Ollier, J. Charbonnier, E. Bourjot, D. Dutoit, P. Vivet, F. Clermidy CEA – LETI, CEA – LIST, Grenoble, France

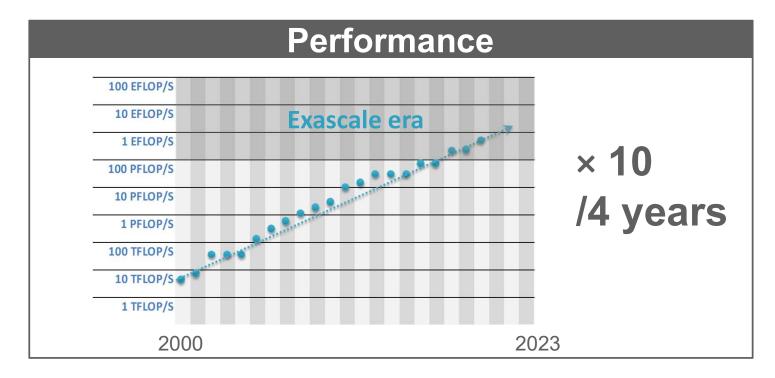

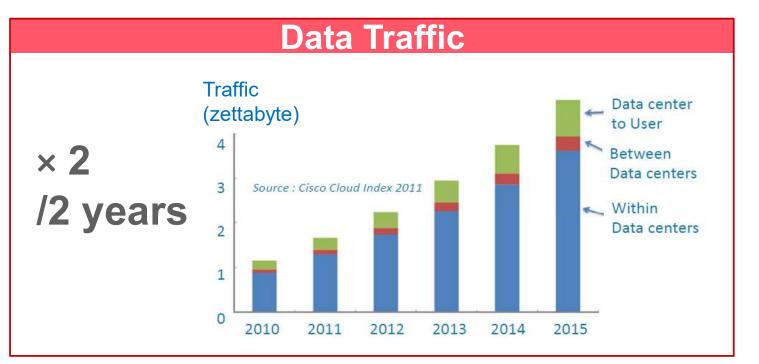

# **Exascale computing trends** Needs for heterogeneous 3D integration

# **INTACT** Demonstration

Many-core integration on active silicon interposer

# **Fowards ultra-fine pitch interconnects** Hybrid bonding approaches

#### leti Challenges in computing & big data applications Ceatech

Chiplet Integration on Active Silicon Interposer - June 2021 APEC conference

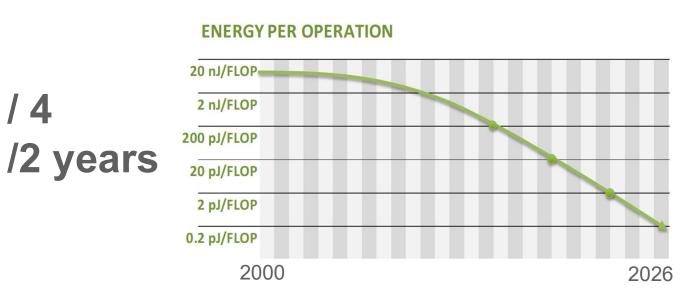

#### **Energy per Operation**

#### leti High performance computing (HPC) & Big data Ceatech

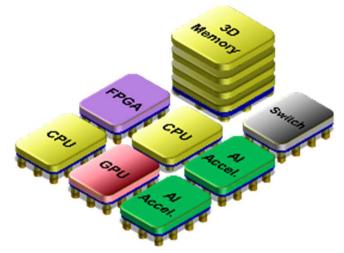

### More cores, more accelerators, more memory

- Highly optimized generic & specialized functions

- Go-to-market solution for sustainable system differentiation

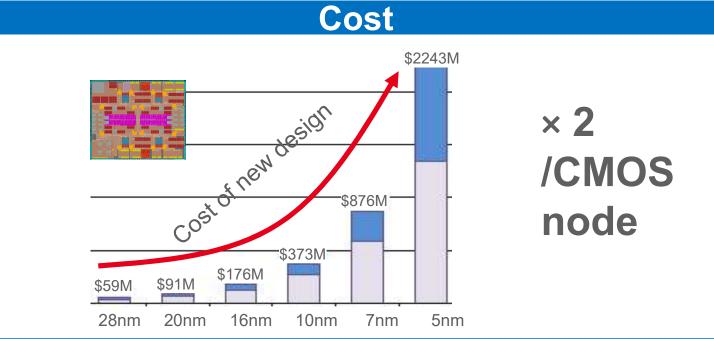

# Single-die SoC approach not viable anymore

- **Digital**  $\rightarrow$  advanced CMOS cost & yield

- Analog  $\rightarrow$  does not shrink anymore

- System designers must offer

- Modular and cost effective solutions

- **Energy efficiency** in system infrastructure

- More on-chip memory bandwidth per core

Chiplet Integration on Active Silicon Interposer - June 2021 APEC conference

| 5

-NVIDIA Volta -**FP64**

••• Fujitsu A64FX

-Sunway SW26010

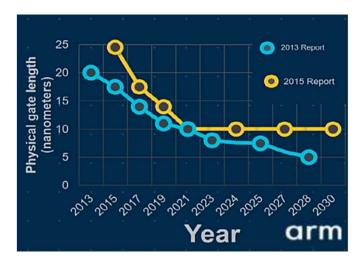

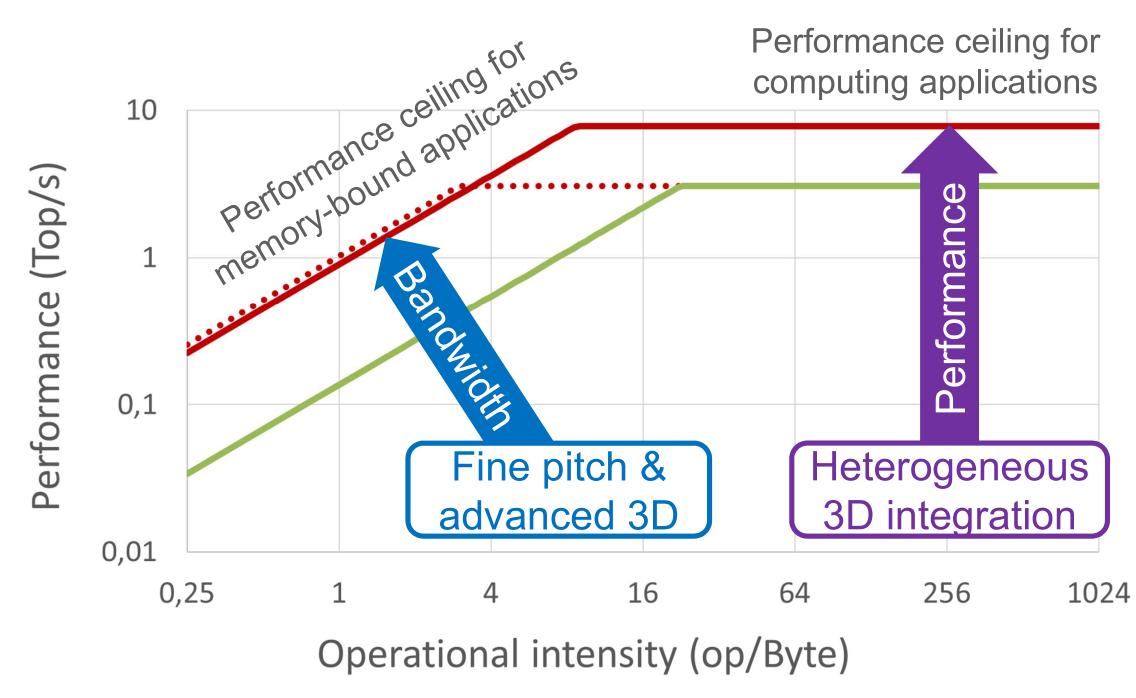

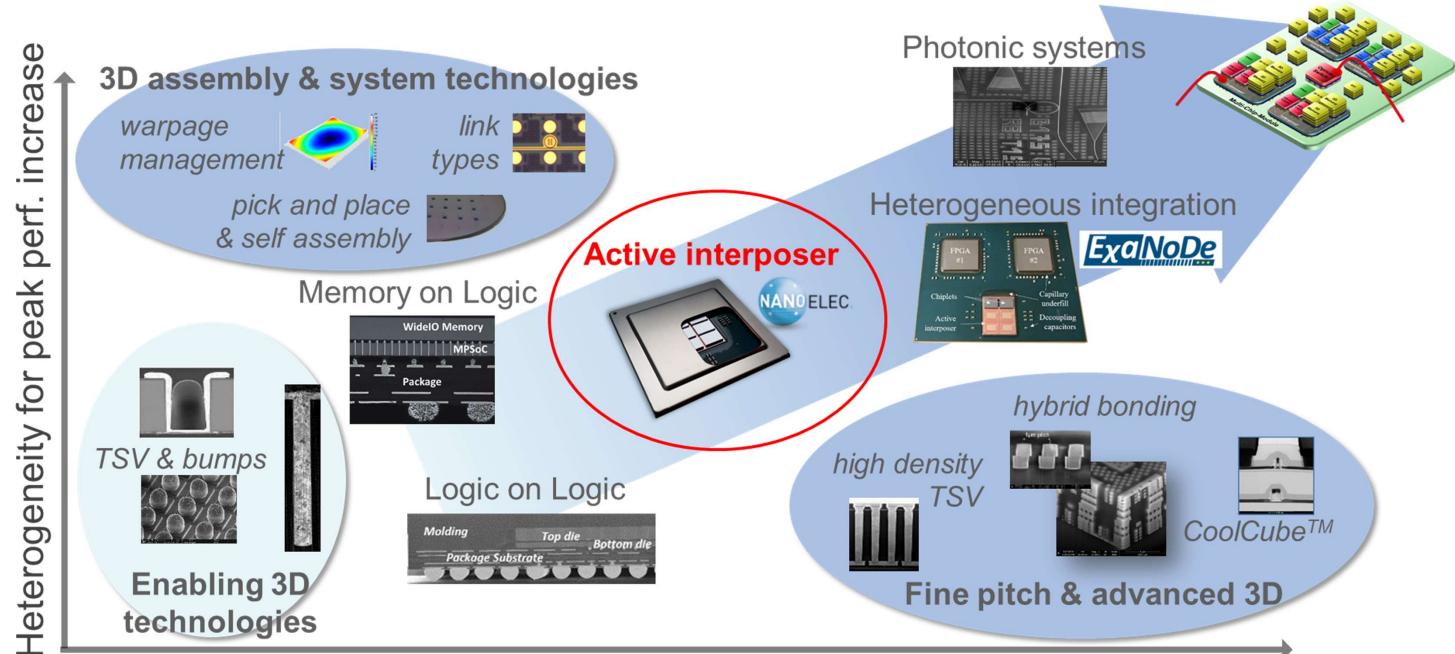

#### leti **3D integration roadmap for HPC** Ceatech

3D pitch reduction for bandwidth increase

| 6

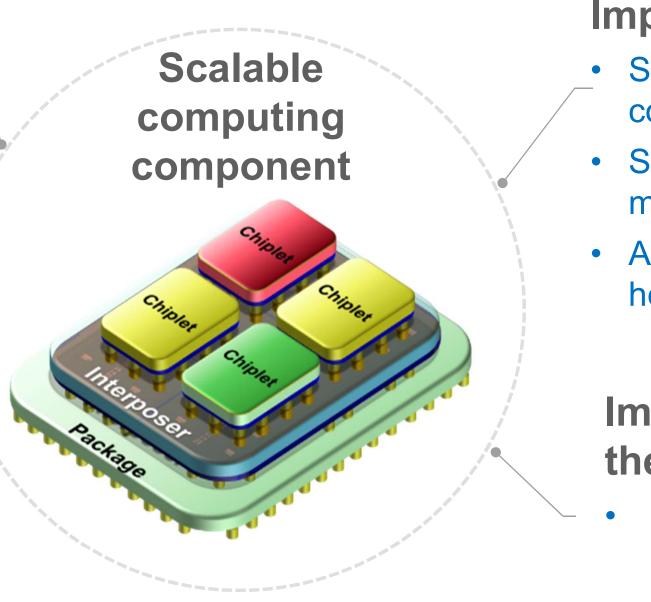

# Why considering chiplets on active interposer?

### Improved cost / performance tradeoff

- Small to medium size chips

- Advanced technology node only when needed

- **Function-partitioning**

### **Specialization**

leti

Ceatech

- Heterogeneous integration

- Flexible communication between chiplets

- Asynchronous network on chip (NoC) for latency reduction

### Improved integration

- Scale-out concept for manycore architectures

- Scalable cache-coherent memory hierarchy

- Adaptation between

- heterogeneous technologies

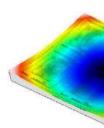

### Improved energy & thermal management

- Energy efficient voltage regulator close to computing chiplet

- **Embedded Sensors**

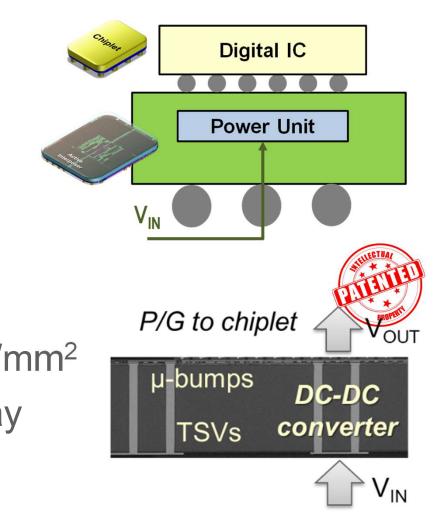

#### leti Focus on switched cap voltage regulators (SCVR) Ceatech

### **Distributed power supply units**

- Local dynamic voltage & frequency scaling (DVFS)

- Fast transitions & reduced IR-drop effects

- High input voltage (up to 2.5V) reduces # power grid IOs

### **Full integration in interposer**

- No external passives, on-chip MOS+MOM+MIM caps  $\rightarrow$  8.9 nF/mm<sup>2</sup>

- 50% of chiplet area, power grid delivery as µ-bump flip-chip array

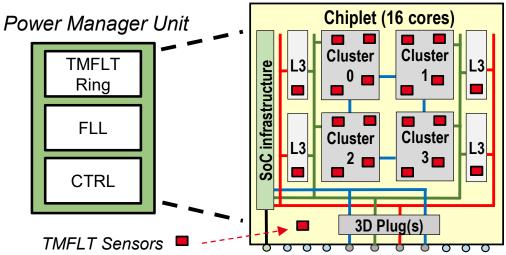

# **Power Management with f**<sub>max</sub>/V<sub>min</sub> tracking

- Circuit estimates V<sub>min</sub> and f<sub>max</sub> & adapts V or F to track optimal energy point

- Time Fault Sensor (*Canary FF like*) estimates f<sub>max</sub>/V<sub>min</sub> of circuit during calibration phase

- Time Fault Ring (configurable replica path) tracks optimal f<sub>max</sub> or V<sub>min</sub> along circuit life-time

#### leti **Power management benefits of f**<sub>max</sub>/V<sub>min</sub> tracking Ceatech

### **PMU** integration within INTACT chiplets

- 1024 Time Fault Sensors per chiplet, 93% capturing useful information  $\rightarrow$  6X w.r.t. other solutions

- 4 Time Fault Rings with 8mV tracking sensibility

- Controller adapts f<sub>clock</sub> to track PVT variations & delay

- Tradeoff f<sub>max</sub> versus V<sub>max</sub>

- $V_{min}/F_{max}$  estimated on wide voltage range [0.4 V 1.3 V]

- Estimation error  $\sim 2\%$  over full voltage range

- Power gain from 19% to 36% w.r.t. signoff CAD results

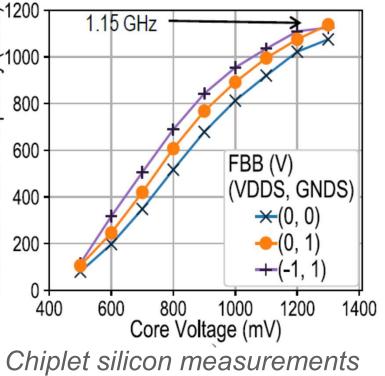

- Achieved with and without FDSOI Body Biasing

- Body biasing range [0;0], [0;+1V], [-1V;+1V]

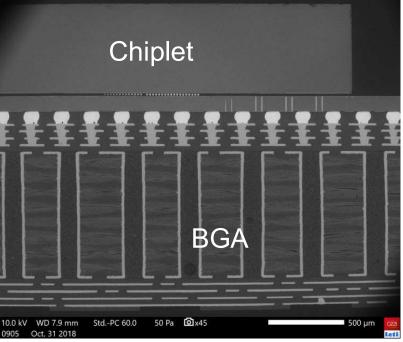

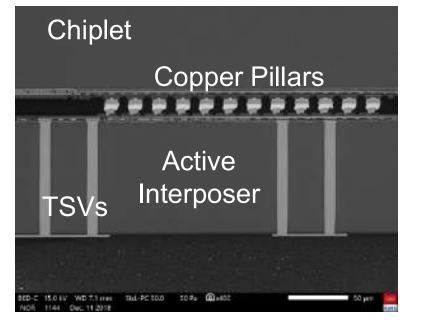

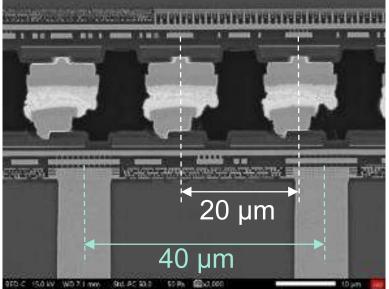

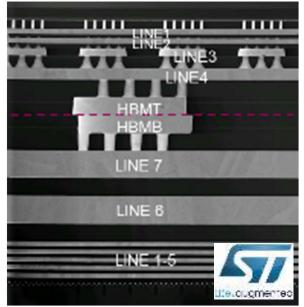

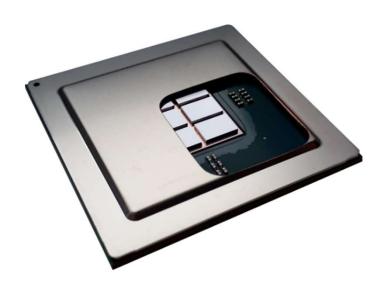

#### leti **Active silicon interposer technology** Ceatech

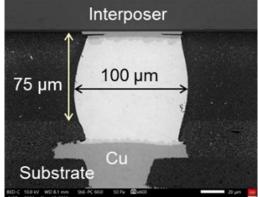

# Through silicon vias (TSV) middle

- Diameter 10µm

- Depth 100µm (AR 10:1)

- Pitch 40µm

# µ-bumps

- Pitch 20µm

- Packaging

Chiplet Integration on Active Silicon Interposer - June 2021 APEC conference

# Warp management

# **Alignment accuracy**

| 10

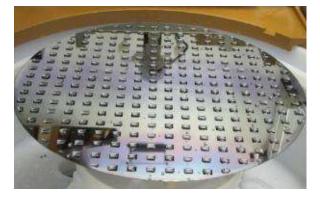

### 150 000 interconnects on interposer (25k/chiplet)

# Diameter 10µm

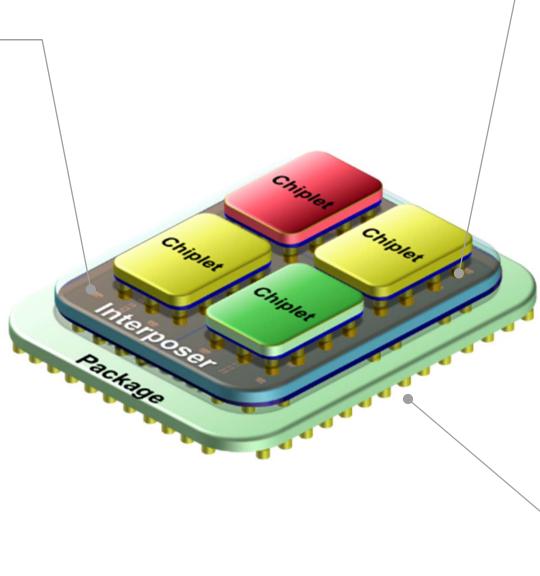

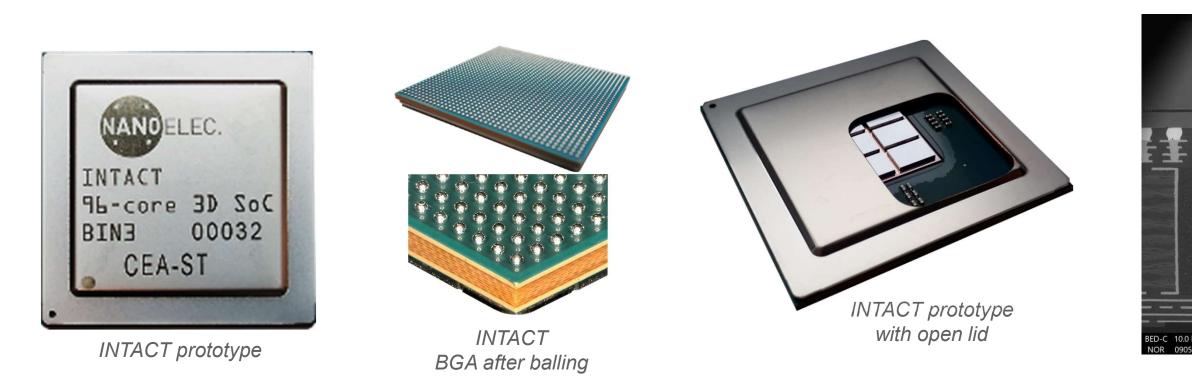

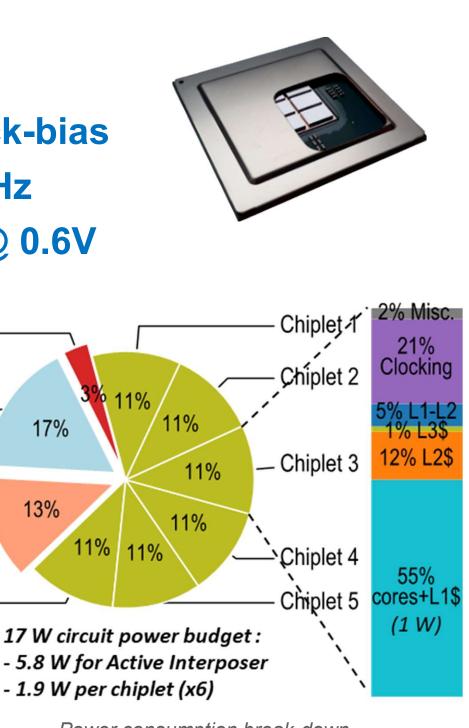

# **INTACT** active interposer demonstration

First demonstration of a large-scale energy efficient computing system on active interposer with chiplets 96-core architecture

[P. Coudrain & al, ECTC'2019], best paper award

Chiplet Integration on Active Silicon Interposer - June 2021 APEC conference | 11

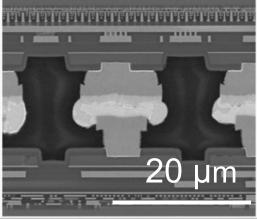

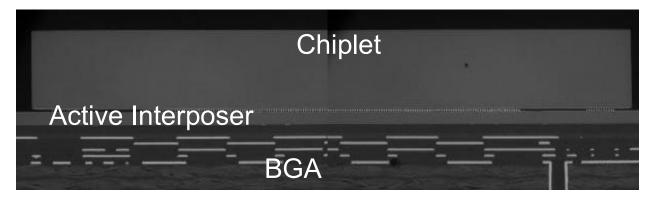

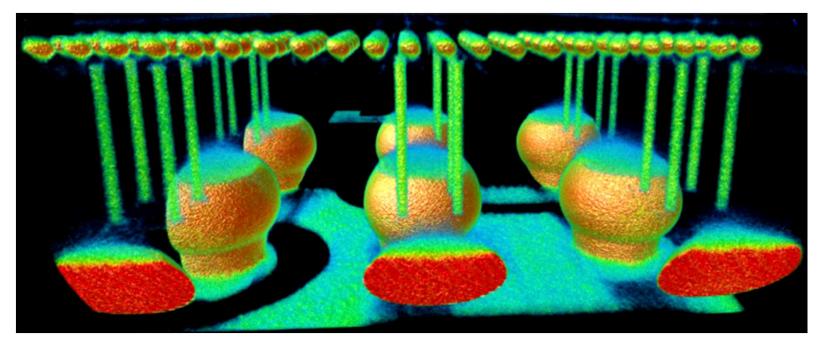

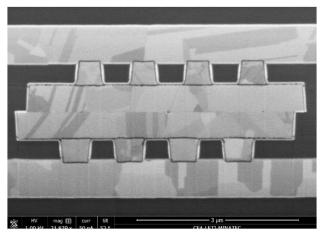

SEM cross sections of the package and focus on the 3D stack

#### leti **3D** assembly physical characterization ceatech

3D X-Ray tomography revealing the internal interconnects structure: µbumps / TSV / Bumps

#### leti **INTACT circuit performances** Ceatech

### **Chiplet main performances**

- Frequency: 130 MHz @ 0.5V 1.15GHz @ 1.1V with back-bias

- Peak performance: 220 GOPS for all 96 cores @ 1.15 GHz

- Energy efficiency: 9.6 GOPS/W (Coremark) @ 246MHz @ 0.6V

# **3D-plug interface & low latency ANOC**

- Throughput up to **3 Tbit/s/mm<sup>2</sup>**

- Latency down to **0.6 ns/mm**

### **Power consumption break-down**

- Cores+L1: ~50% power per chiplet

- Interposer logic & interconnects : **3%**

- Voltage Regulators : **17%** of overall power budget

Interposer

Interposer

Interposer

(incl. pads)

Chiplet 6

MEM-IO

phy

logic

SCVR

17%

13%

Power consumption break-down

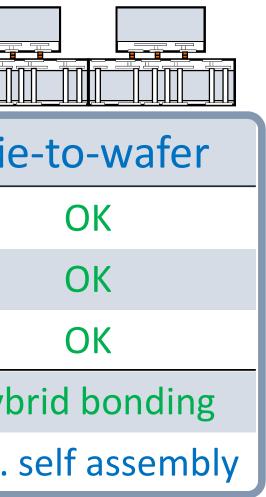

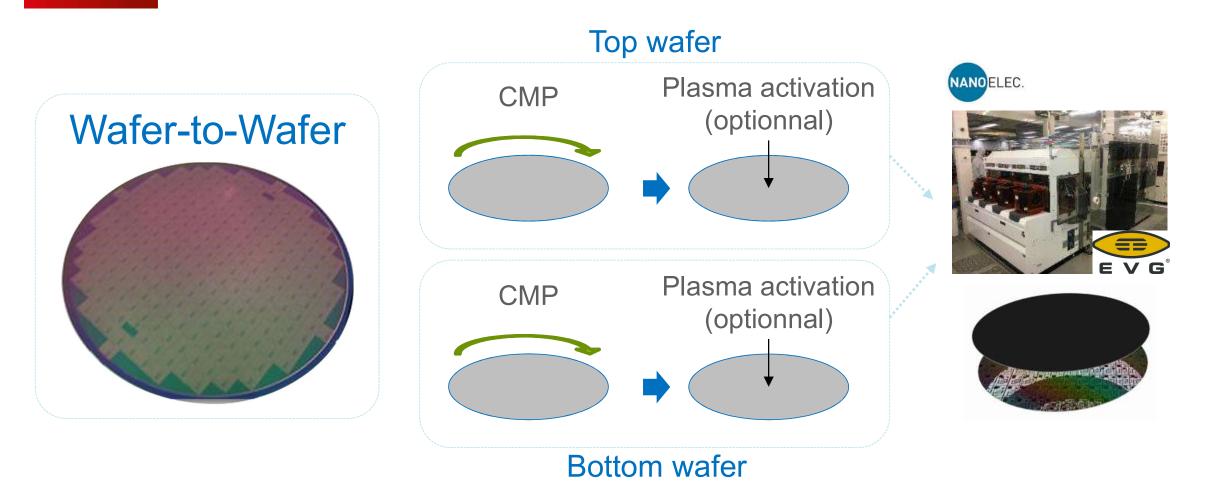

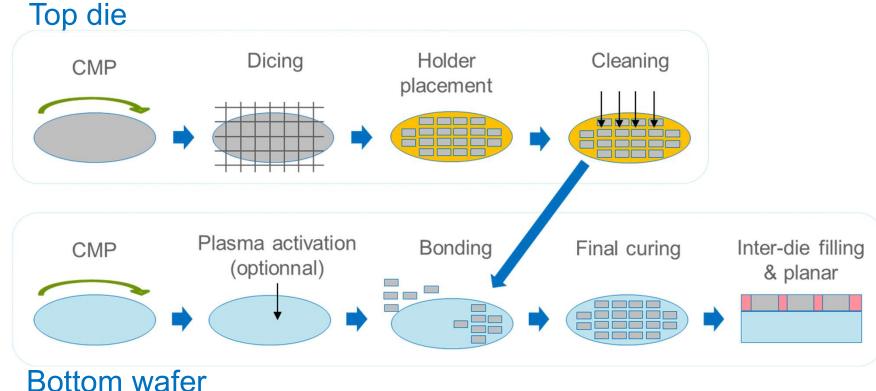

#### leti Challenges for inter-die fine pitch interconnects <u>ceatech</u> Wafer-to-wafer Die-to-die Die-to-wafer **Design flexibility** OK KO OK **Known Good Die** OK KO OK Multi-die stacking KO OK OK Fine pitch enabler Hybrid bonding Hybrid bonding Warpage control Natively collective Coll. self assembly Throughput enabler No

- Pick & Place faces strong alignment / throughput tradeoff

- Die-to-wafer hybrid bonding achieves finer pitch

- Self-assembly as a throughput enabler for die-to-wafer hybrid bonding

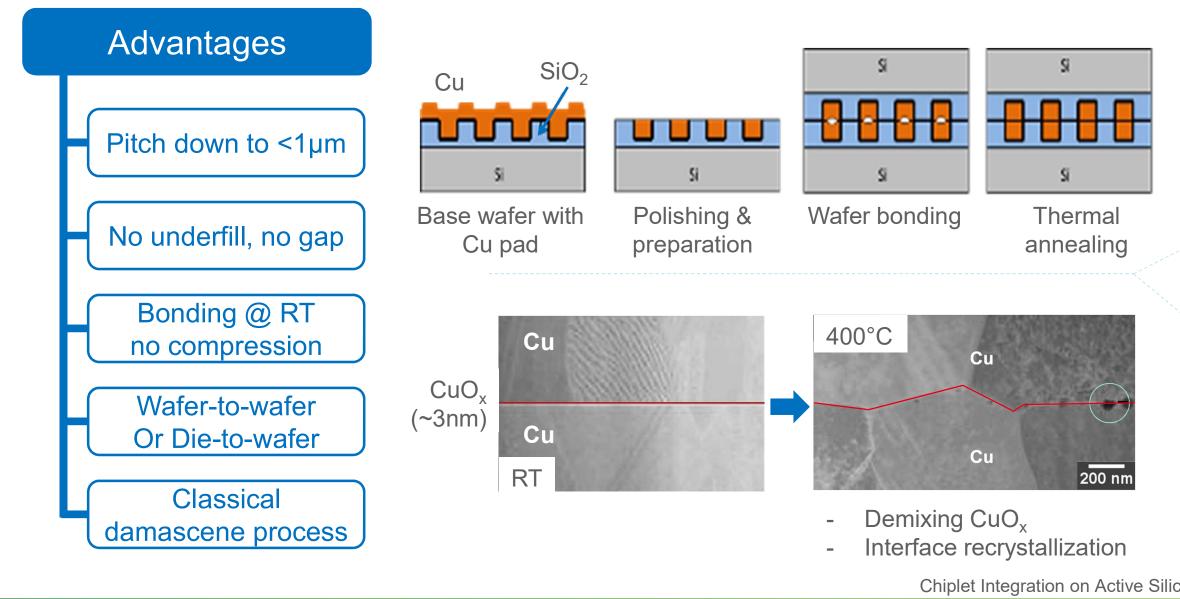

# **Direct hybrid bonding principle**

- Direct bonding is based on the spontaneous adhesion of smooth surfaces

- Cu/SiO<sub>2</sub> Hybrid bonding achieves simultaneous stacking & interconnection

# ooth surfaces

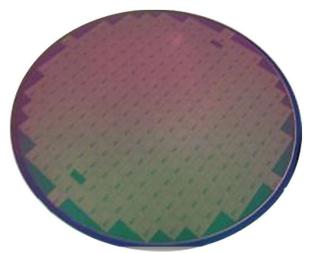

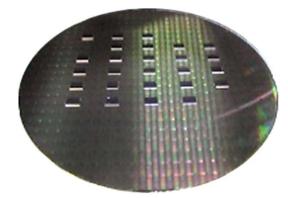

### Wafer-to-Wafer

#### Chip-to-Wafer

#### leti From wafer-to-wafer hybrid bonding... Ceatech

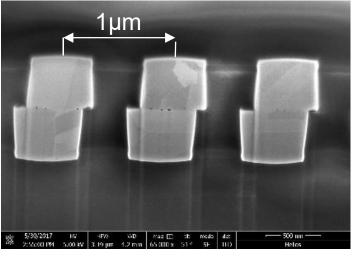

- Wafer-to-wafer hybrid bonding achieves ultra fine <1µm 3D interconnects pitch with high throughput

- Design limited (identical footprint between top/bottom)

Hybrid bonding on CMOS wafers

Hybrid bonded 1µm pitch interconnetcs

leti

Ceatech

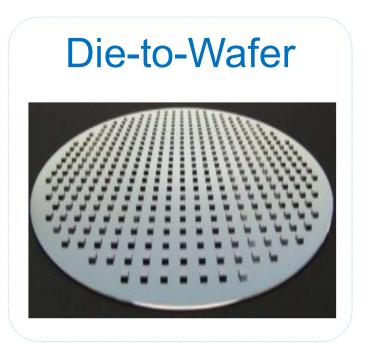

- Die-to-wafer allows **known good die** (KGD) strategy, heterogeneity & multi-die stacking

- Throughput improved with self-assembly collective approach

SEM cross section of die-to-wafer hybrid bonded interconnects

Die-to-wafer hybrid bonding SET tool

Self-assembly demonstration for *high throughput / high accuracy*

#### leti Take away messages Ceatech

# Heterogeneity & bandwidth enablers for exascale HPC

- Chiplets on active interposer as new paradigm for HPC

- 3D assembly options towards heterogeneous processors

- Higher bandwidth comes with fine pitch 3D interconnects

- Embedded power management allows energy efficiency

- Successful chiplets integration on active silicon interposer demonstrated with high performance

- Further improvements underway with process developments

- Direct hybrid bonding for ultra-dense die-to-die interconnects

- Die-to-wafer bonding for heterogeneous 3D integration (III/V on CMOS...)

This work was supported by the French National Program "Programme d'Investissements d'Avenir, IRT Nanoelec" under Grant ANR-10-AIRT-05.

Nom événement | Nom Prénom | Date | 19