Rugged, high-performance 650 – 1200V SiC MOSFETs with flawless gate oxide integrity

Additional info here.

Martin Domeij, Fredrik Allerstam and Thomas NEYER of ON Semiconductor

### Agenda

- ON's growing SiC product portfolio

- SiC MosFET Gate drives harmonization in sight?

- Speedlimit for discrete SiC MosFETs the body diode

- How to sustain a flawless gateoxide on defective material

- Paralleling of MosFET (worst case spread)

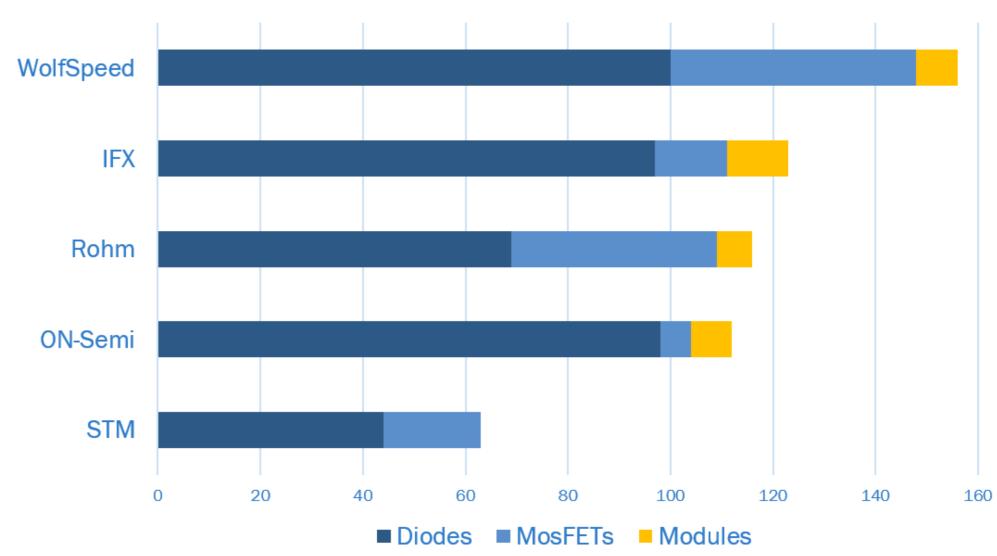

## SiC products on the open market Q4/2019

ON released 1<sup>st</sup> 6" SiC product in 2015 and has grown its portfolio

Key focus on automotive qualification and supply chain superiority

Comparable FOM on Diodes and MosFETs between top 5 suppliers

#### SiC Product offering top5 IDMs

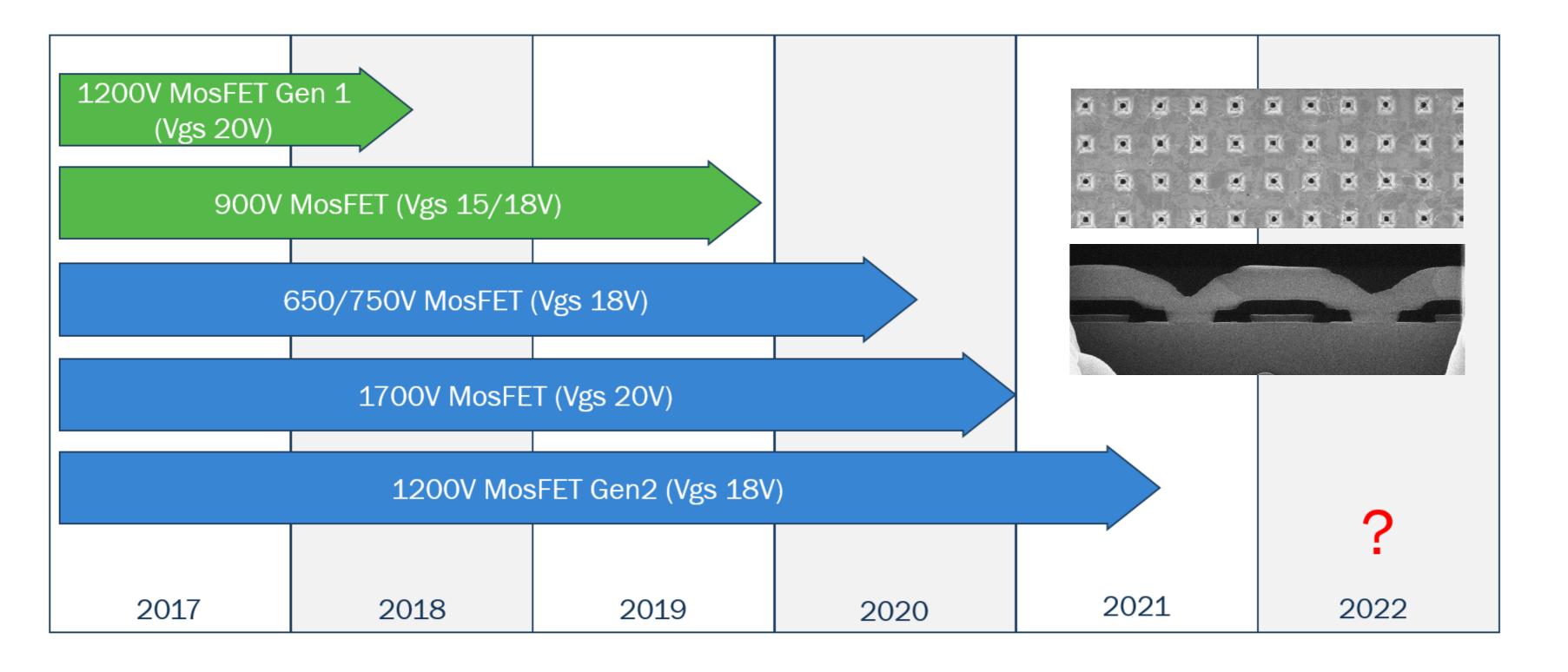

# AEC-Q101 SiC MosFET platform roll-out

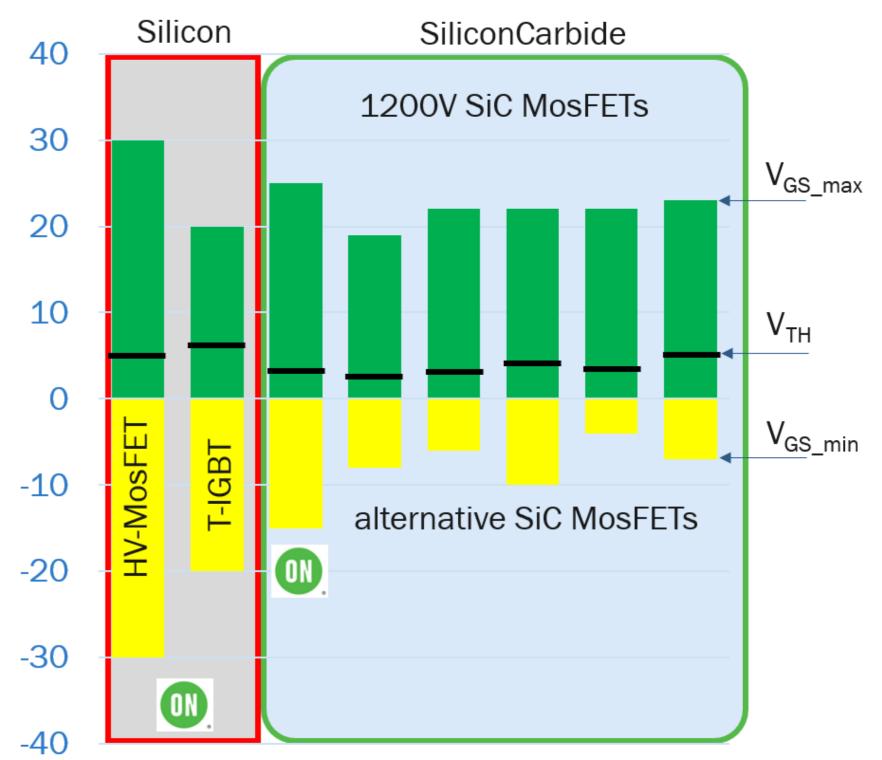

# Gate drive voltage range – What's the right choice?

#### Silicon:

HV transistors allow symmetrical Gate-Source maximum ratings and recommended drive conditions

$V_{TH}$  is standardized at >4V

#### SiC:

VTH of majority of suppliers is ~3V

most MosFETs are more sensitive at negative voltage

recommended drive conditions range from 15-20V / -- (5-0)V

### Gate drive voltage range – What's the right choice?

The best SiC MosFET is optimized for device lifetime not for compatibility to legacy Silicon gate drives

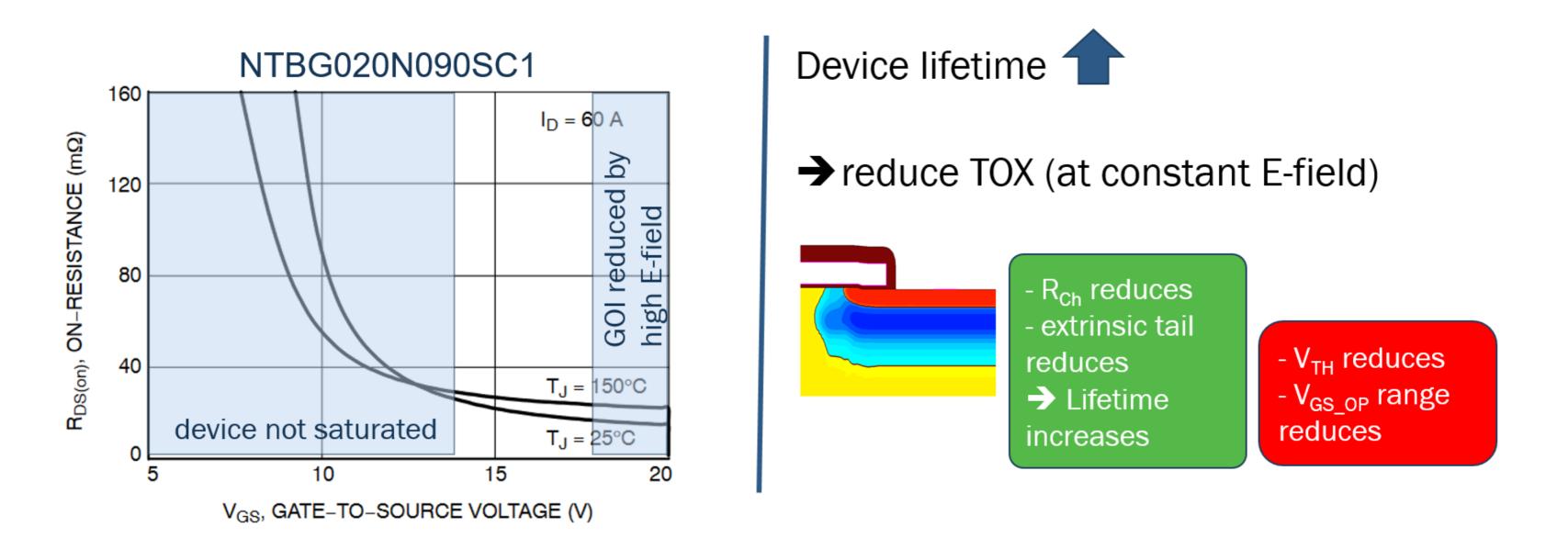

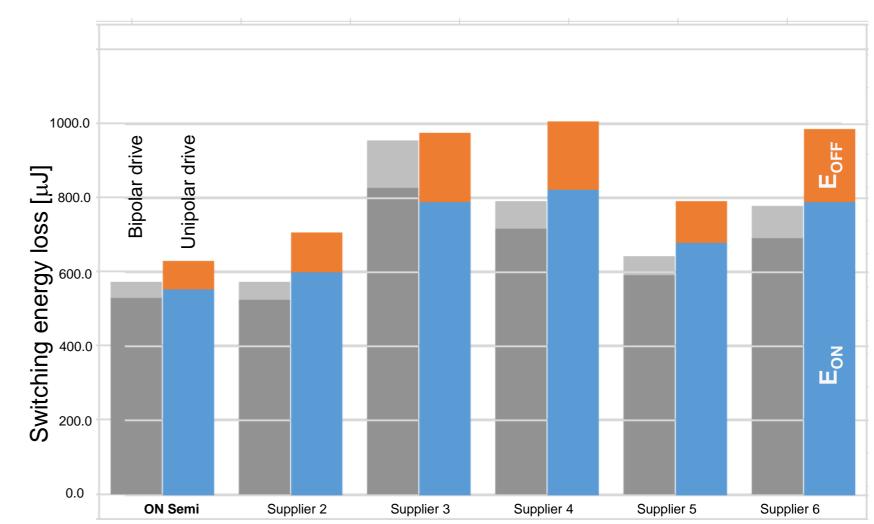

# Gate drive voltage range – bipolar vs unipolar drive?

For convenience and cost saving desire for unipolar drive (no negative supply required)

- → Increase of switching losses to be expected

- → risk for miller turn-on in half-bridge

- → Increase of reverse leakage

Not recommended but acceptable for most SiC MosFETs on the market

1200V 75 – 90m $\Omega$  devices – Double pulse test, 800V VDC, 20Am Rg=4.7 $\Omega$  Gate drive: as recommended vs VGS\_min = 0V using NCP51705 ON-Semi

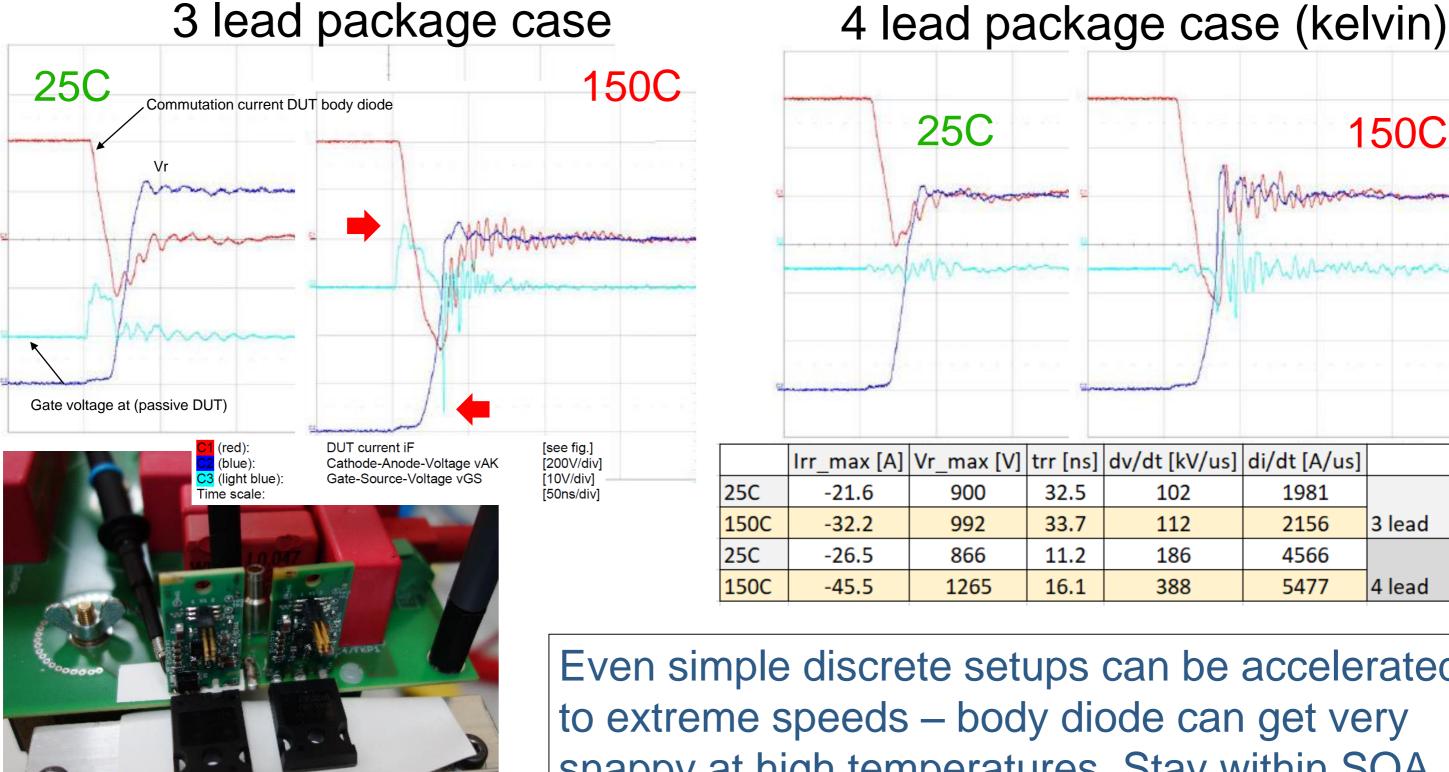

# Adopting SiC MOSFETs for high speed operation

- Extreme switching speeds put requirements on a lower inductance environment, especially source inductance and use of Kelvin source

- Methods to dampen oscillations from all sources, careful choice of Rg to design for speed but maintain a stable circuit

- Low internal Rg gives bigger design space, but require more from the designer to manage the switching speed and inductive environment

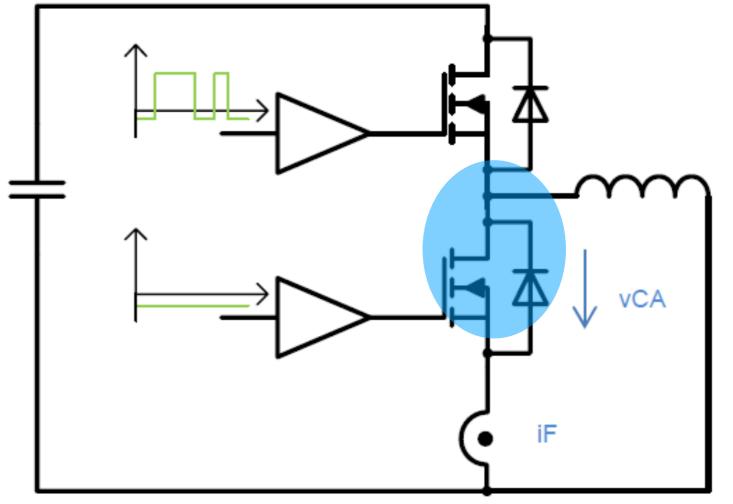

#### 1 Test circuit topology

a) DUT static off @ (-)5V VDC=800V, Ic=20A, VGS -5/+20V

## Adopting SiC MOSFETs for high speed operation

Even simple discrete setups can be accelerated to extreme speeds – body diode can get very snappy at high temperatures. Stay within SOA

150C

3 lead

4 lead

1981

2156

4566

5477

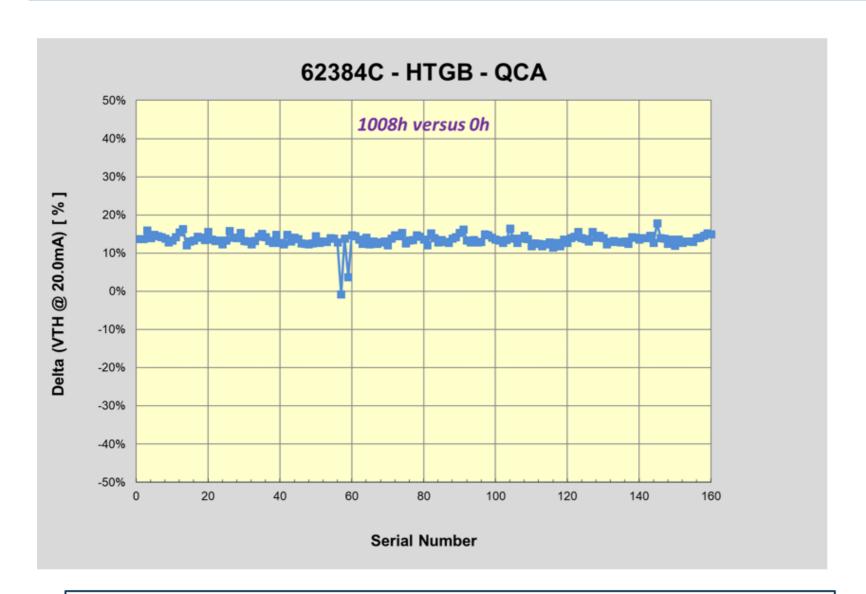

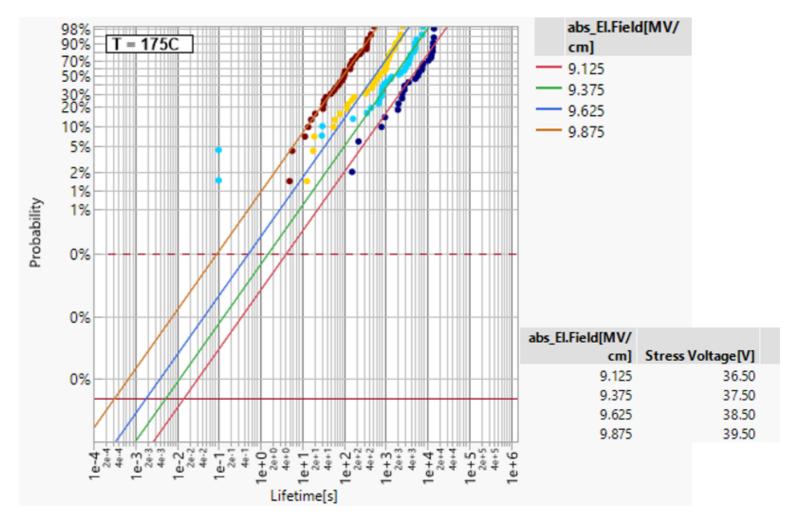

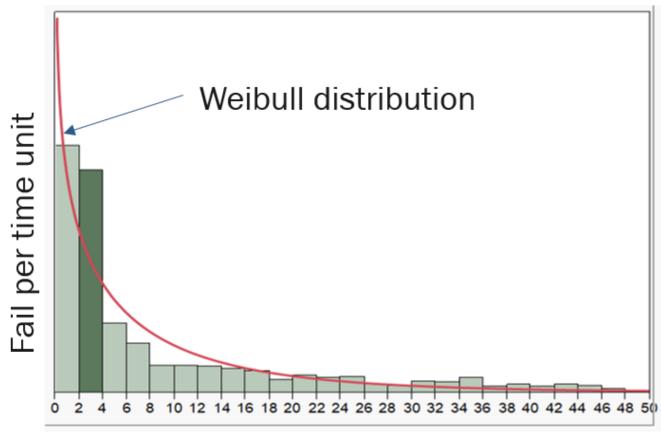

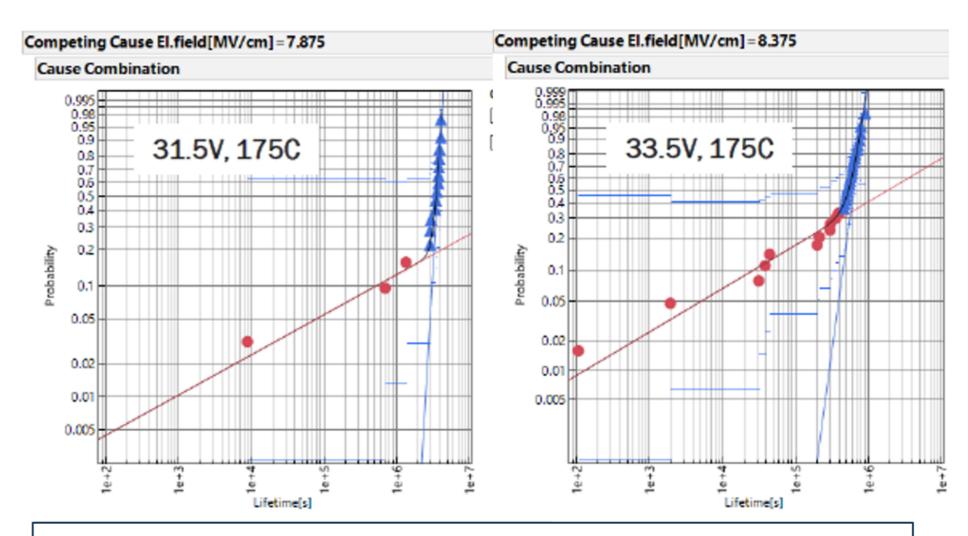

## Gateoxide reliability - intrinsic capability

Recoverable Vth drift after 1000hrs, 175C, Vgs=25V <20%

Intrinsic GOX comparable to planar Silicon devices.

| 900V WLR @ 6 cm <sup>2</sup> | Results | unit  |

|------------------------------|---------|-------|

| Tox                          | 400     | Å     |

| Temperature                  | 175     | °C    |

| Vgs op                       | 15      | V     |

| Weibull slope β              | 0.941   |       |

| E-model Gamma                | 3.03    | cm/MV |

| FIT @ 20yrs VGS_max          | <0.1    | ppb   |

#### How about extrinsic tail in SiC MosFETs?

#### Screening methodology:

- removal of crystal defects

- gate stress test

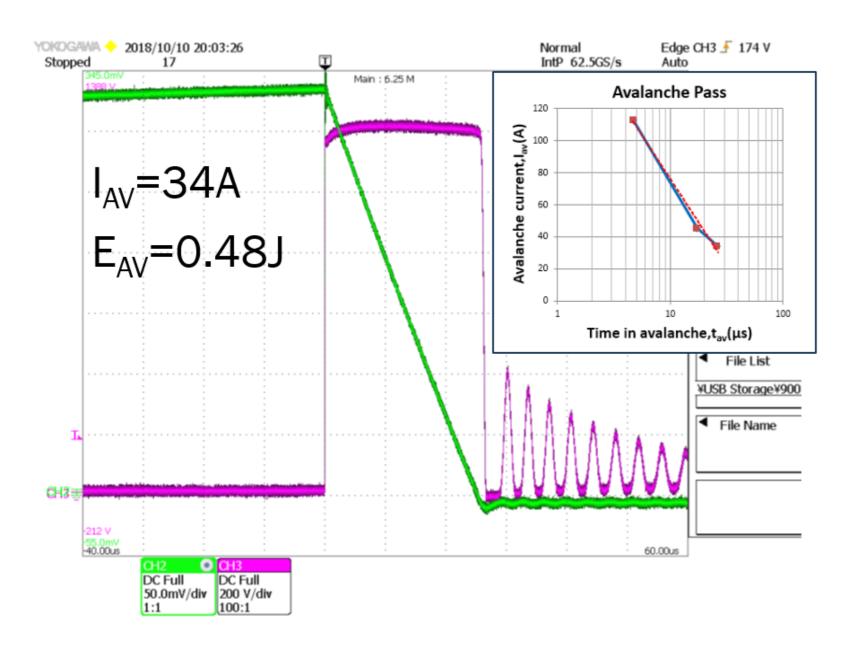

- avalanche stress test

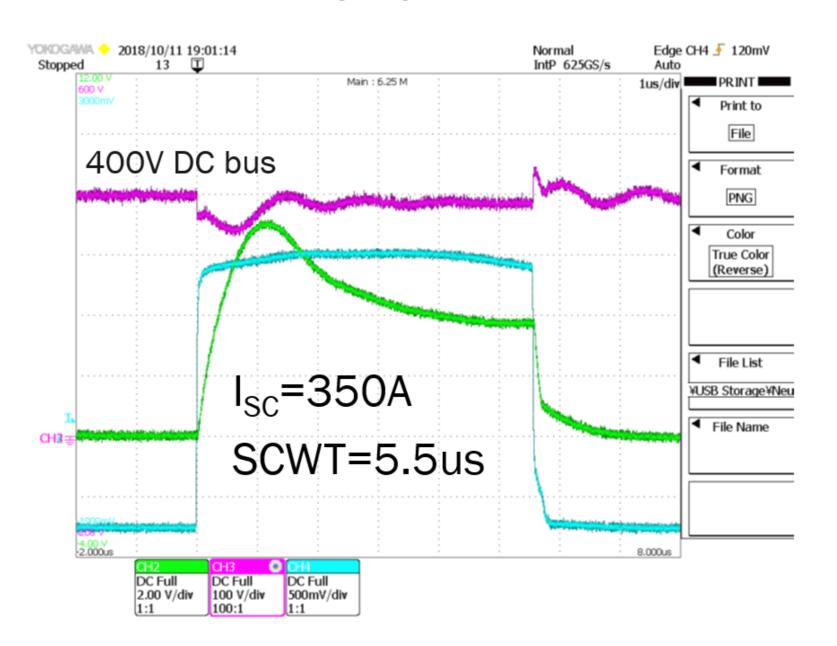

- parametric test on wafer and package level

- burn-in on wafer-level

Time [arbitrary units]

Well proven Silicon test screening methodology is not sufficient to prevent infant mortality

Post BI failure rate is extracted to be comparable to HV Silicon devices

#### Avalanche test 60m0hm (1mH)

#### Short Circuit capability (Type2)

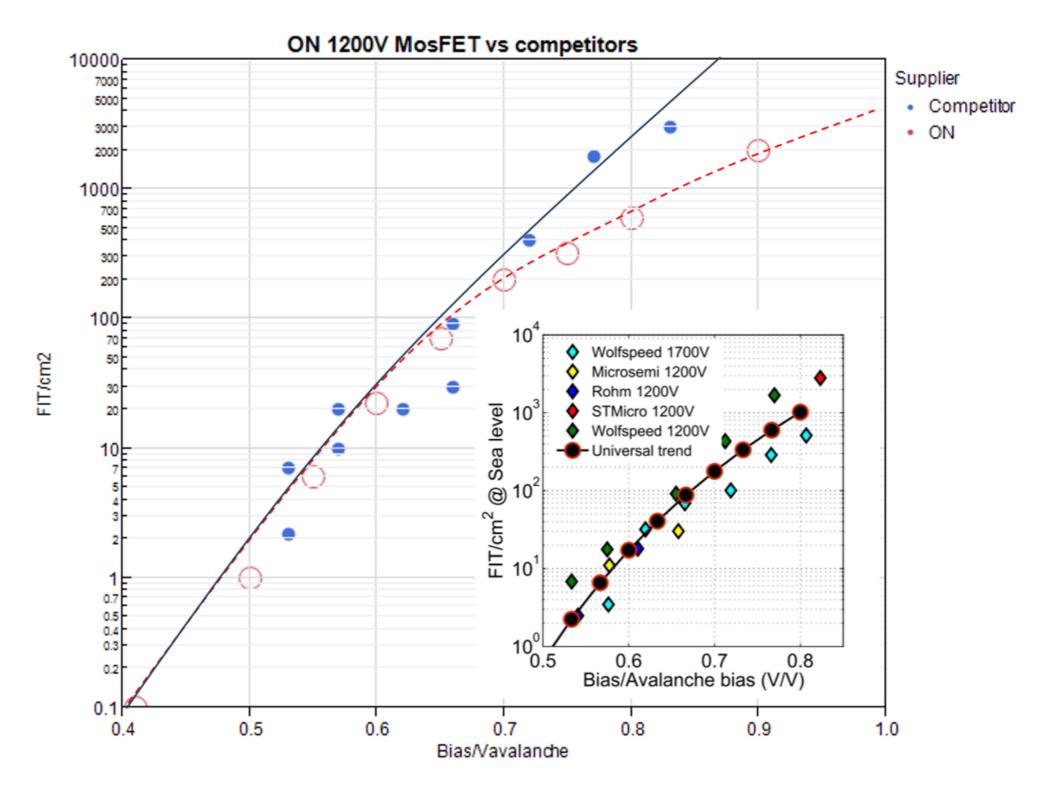

#### Ruggedness against cosmic rays (@sea level)

According to Akturk et al, there appears to be a universal dependency FIT vs bias

Device field optimization and drift layer design can significantly alter/improve this relationship at higher fields

Systematic optimization yields lowest failure rates

A. Akturk, J. McGarrity, N. Goldsman, D. J. Lichtenwalner, B. Hull, D. Grider, R. Wilkins, "The effects of radiation on the terrestrial operation of SiC MOSFETs," Int. Reliability Physics Symposium (IRPS), (11-15 March 2018).

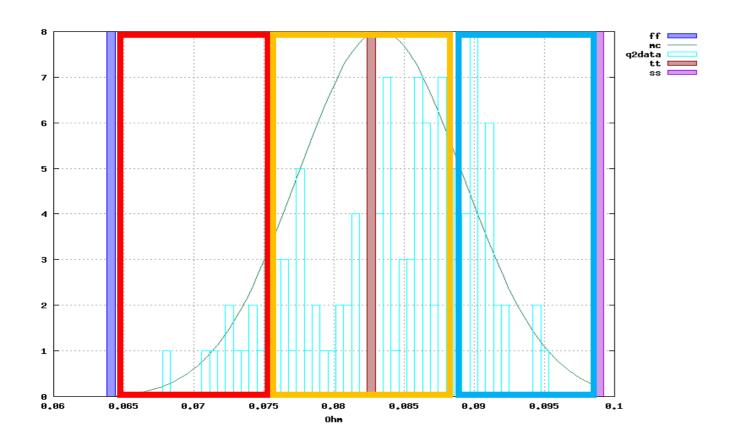

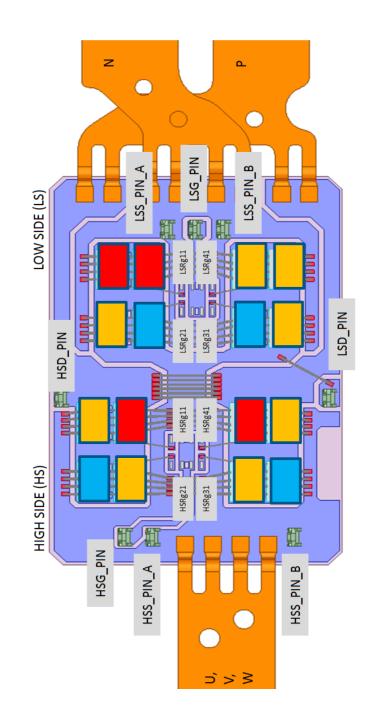

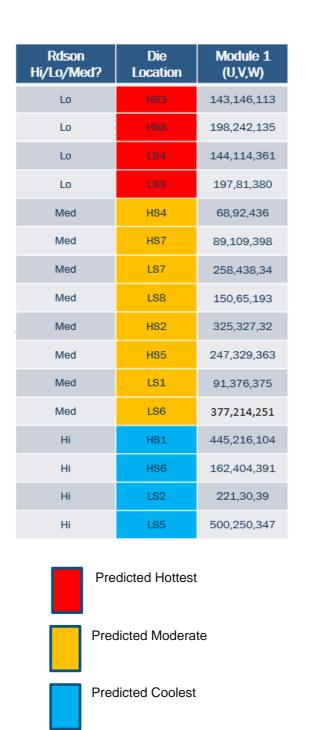

## SiC MosFET paralleling – exercise to assess Temperature offsets

- Production variation results in finite parameter distributions i.e Vth, Rdson, HVbr,...

- To enable high current ratings several large SiC MosFETs are being paralleled

- Statistical thermoelectrical models can be used to assess the dynamic effect of worst case (ref paper J. Victory)

- Cherry-pick assembly of extreme-offset Rdson are being used to confirm simulation prediction

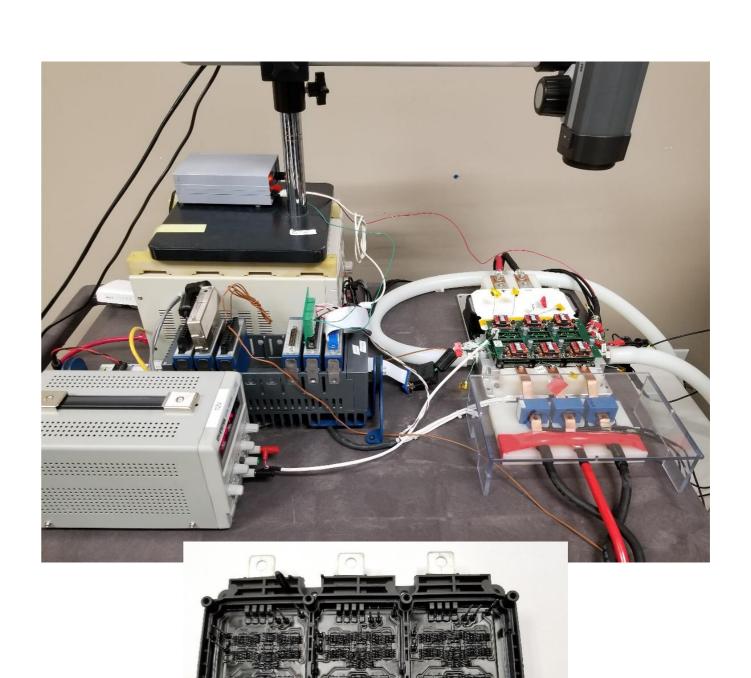

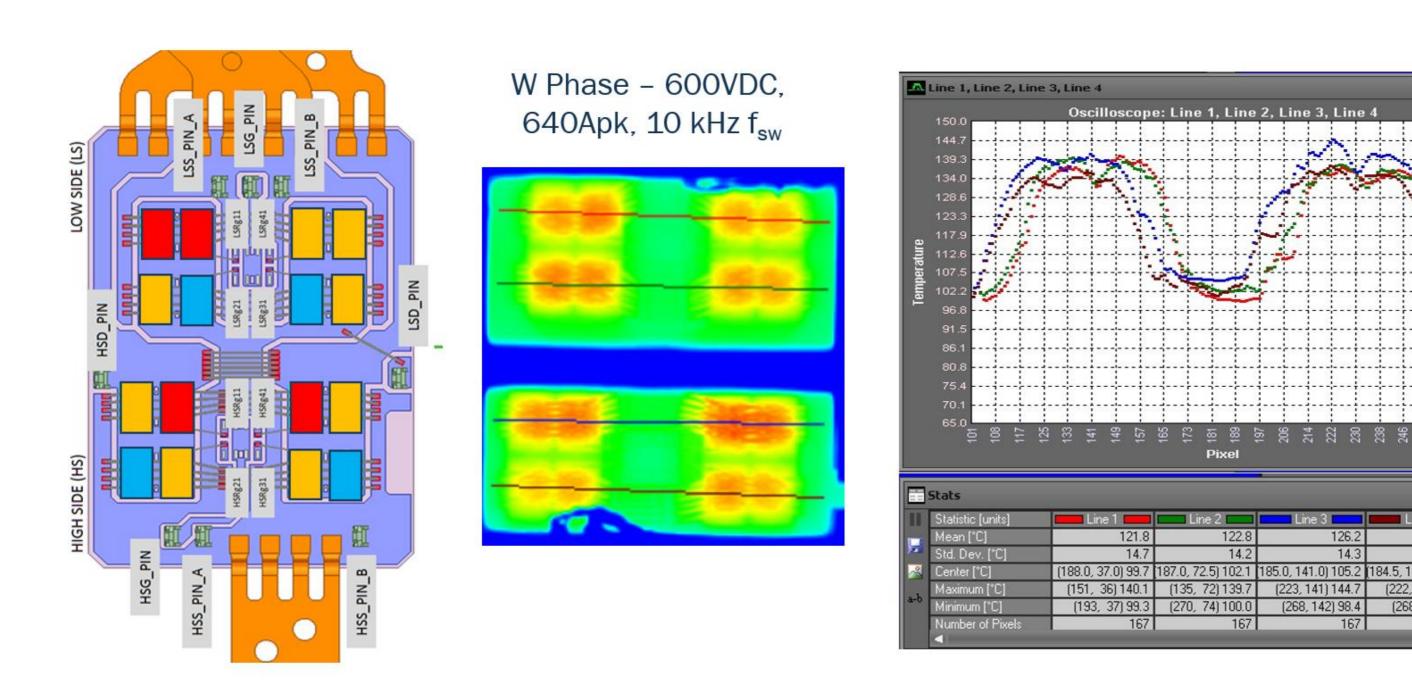

- Opened, black module, 3 phase drive at 600VDC, glycol/water cooling loop, Flir camera

### SiC MosFET paralleling – exercise to assess Temperature offsets

Typical distribution on a random SiC MosFET wafer – assembled onto module

### SiC MosFET paralleling – exercise to assess Temperature offsets

Oscilloscope plot shows about 5C per vertical division, or about 7C temperature difference from hottest to coolest die.

#### **OUTLOOK**

- 650V 1700V SiC devices are turning into a commodity

- Customization for volume application

- comparable ratings

- tradeoff btw current density and thermal performance

- High reliability and robustness standards are being established

- SiC device and package innovation will enable several more product generations