### Selected Topics on Power GaN and SiC Device Reliability

Sameh G. Khalil<sup>1</sup>, Hyeongnam Kim<sup>1</sup>, Jinming Sun<sup>1</sup>, Thomas Aichinger<sup>2</sup>, Ingo Voss<sup>3</sup>, Paul Salmen<sup>3</sup>, Tim McDonald<sup>1</sup>, Peter Friedrichs<sup>3</sup> and Alain Charles<sup>1</sup>

<sup>1</sup>Infineon North Americas Inc., <sup>2</sup>Infineon Austria AG, <sup>3</sup>Infineon Technologies AG

- Introduction

- 2 Qualification methodology for wide bandgap

- 3 Selected topics on power GaN reliability

- 4 Selected topics on power SiC reliability

- 5 Wide bandgap standards

- 6 Conclusions

Introduction

# Qualification methodology for wide bandgap Selected topics on power GaN reliability Selected topics on power SiC reliability

- 5 Wide bandgap standards

- 6 Conclusions

### Mega social trends

#### Mega Cities and

**Increased Population**

CO<sub>2</sub> Emission Automotive Electrification Security in Communiction

**Efficient Power Processing**

High Density Solutions

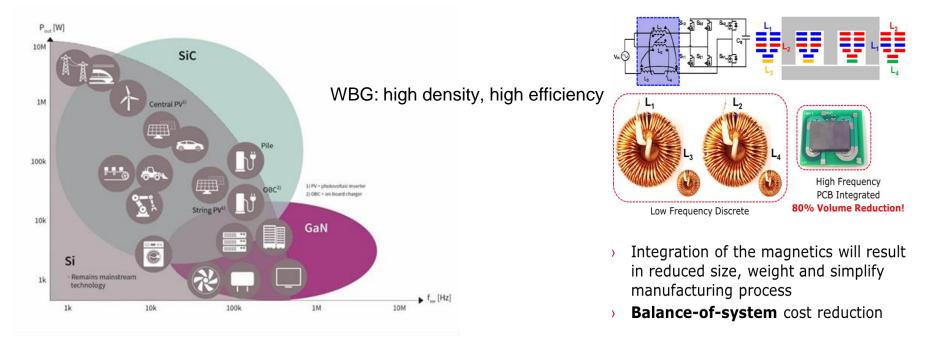

# Co-existence is expected between the three main material systems: Silicon, SiC and GaN

Ability to offer Si, SiC and GaN ensures impartial value proposition offering to the customer

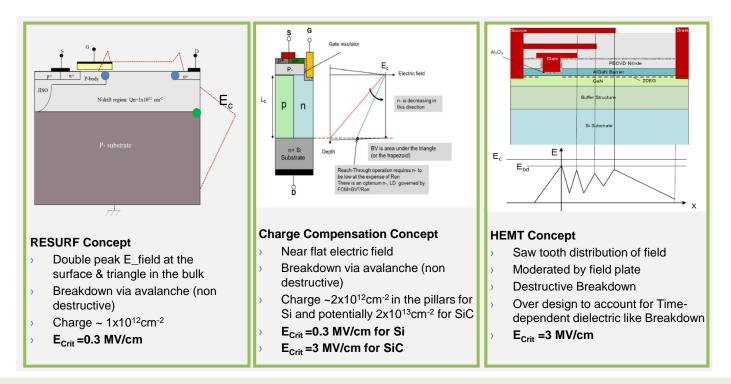

# Design of power devices – optimizing the drift region for low losses and smart electric field distribution

Breakdown voltage is reached when the electric field peak reaches the critical electric field  $E_{crit}$  of a material .

### Introduction Qualification methodology for wide bandgap 3 Selected topics on power GaN reliability 4 Selected topics on power SiC reliability 5 Wide bandgap standards Conclusions

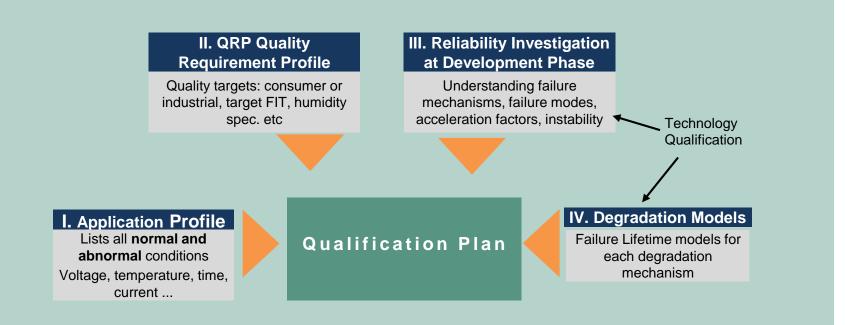

# The 4 main ingredients for WBG qualification involving technology & Product qualification

Introduction 2 Qualification methodology for wide bandgap Selected topics on power GaN reliability 3 4 Selected topics on power SiC reliability 5 Wide bandgap standards 6 Conclusions

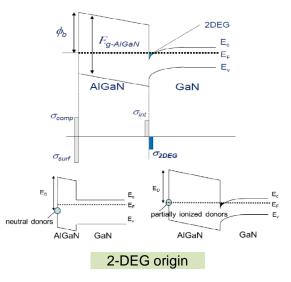

# Lateral e-mode GaN device structure (GIT) – major structural elements

operation **Chip Passivation** Power Metal Power Metal ILD Drain Source 1<sup>st</sup> level passivation p-GaN i-AlGaN1 2DEG i-GaN Fully recessed AlGaN1 GaN buffer Si substrate

P-GaN layer: hole injection promotes de-trapping of electrons during off-state and hard switching

Ohmic PGaN Gate: to deplete 2DEG below gate for Normally off

Heterojunction: high 2DEG density and high mobility for low R<sub>on</sub>

Buffer layer: highly resistive, high vertical breakdown voltage with minimum trap density. Has to address mismatch in lattice constant and thermal expansion coefficient between GaN and Silicon and ensure minimal stress in the GaN Epi stack (simplified view) Si Substrate: cost effective, potential monolithic integration with Si ICs and leverage economies of scale of Si technology

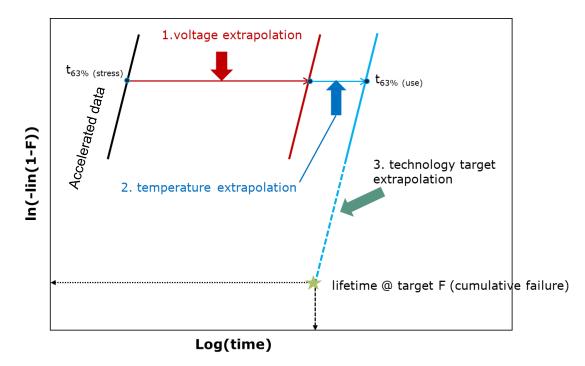

# Accelerated lifetime testing and extrapolation – principle of accelerated testing

Key factor for a reliable extrapolation is verified knowledge about acceleration factors (for bias and temperature e.g.)

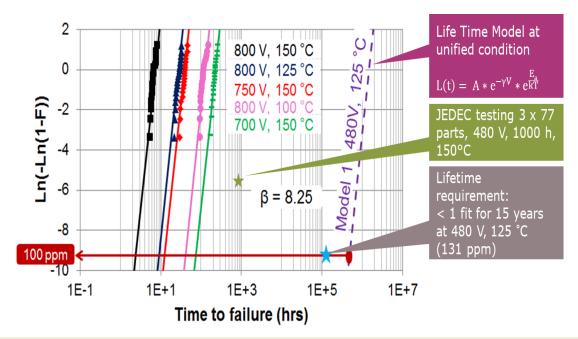

# Lifetime parameter extraction and extrapolation to use conditions (example TDDB like evaluation for GaN)

- > The acceleration model is developed for voltage and temperature

- The predicted lifetime is ~55 years at 100 ppm, (480 V and 125 ° C) which clearly exceeds the target for telecom rectifiers of 15 years

- > > 3X safety margin from Infineon's criteria

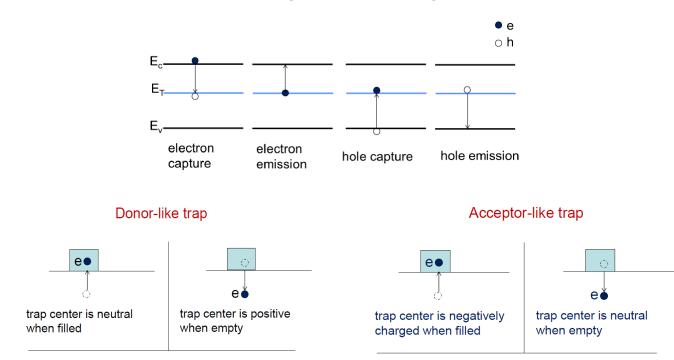

### Drift of essential device parameters – role and origin of traps

- > A trap is a defect originating from a structural defect or the presence of an impurity or a sudden loss of continuity in the crystal lattice (as in interfaces)

- A defect disrupts the periodicity of the crystal lattice and introduces an energy level within the bandgap (undesirable)

Stacking fault in the saguaro cactus

#### Charge trapping

Capture: trap center becomes more negative

Emission: trap center becomes more positive

Capture: trap center becomes more negative Emission: trap center becomes more positive

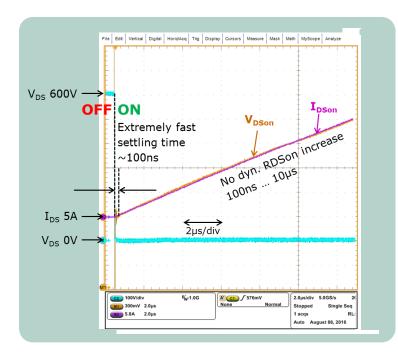

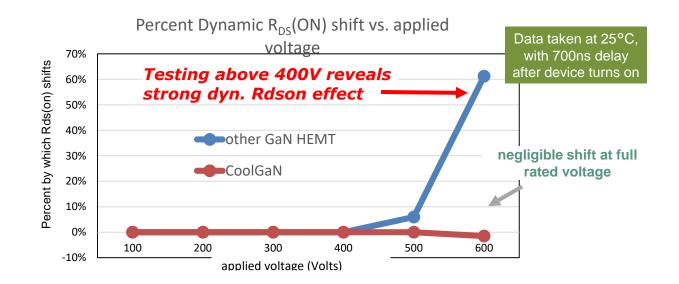

# A typical trap related effect in GaN HEMTs is the so called dynamic $R_{dson}$ : How to test?

- Charge trapping changes the effective Rdson → e.g. 40% dynamic R<sub>DSon</sub> turns a 35mΩ device into a 50mΩ one, characterization essential

- As implicated by it's name dynamic R<sub>DSon</sub> testing is strongly dependent on timing as the charge trapping relaxes with time

- Typically measured data for dynamic R<sub>DSon</sub> are stated at 2.5µs after turn-on for 400V

- For hundreds of kHz up to MHz switching this is not enough

- CoolGaN<sup>™</sup> has been characterized down to 100ns for at V<sub>dsmax</sub> 600V with no R<sub>DSon</sub> increase

- We have 100% of all shipped parts

tested with 600V / 700ns

- Test now adopted by JEDEC

# Dynamic R<sub>dson</sub> 600V CoolGaN™ technology reliability - application level test example

Dyn.  $R_{ds}$ ON measured real time during hard switching! At full rate

True application measurements taken a few hundreds ns after hard switching device turn on! Still no impacts on datasheet!

Introduction 2 Qualification methodology for wide bandgap 3 Selected topics on power GaN reliability Selected topics on power SiC reliability 4 5 Wide bandgap standards Conclusions

# SiC module qualification summary – standard tests complemented by mission profile based procedures

| Test      | Chips<br>in Test            | Test conditions                                                                                                                                              | stress time –<br>for product<br>release | Robustness validation                          |

|-----------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------|

| HTRB      | 72                          | V <sub>DS</sub> =1080V, T=150°C                                                                                                                              | 1000h                                   | +4000h                                         |

| HTGS      | 72                          | $V_{DS}$ =0V, $V_{GS}$ =+20/-20V, T=150°C                                                                                                                    | 1000h                                   | +4000h                                         |

| H3TRB     | 72                          | V <sub>DS</sub> =80V, T=85°C, rH=85%                                                                                                                         | 1000h                                   | +2000h                                         |

| HV-H3TRB  | 72<br>(std.)<br>700<br>(RV) | V <sub>DS</sub> =960V, T=85°C, rH=85%                                                                                                                        | 1000h                                   | 1000h<br>+2000h                                |

| PCsec     | 72                          | T <sub>vj,max</sub> =150°C, ΔT=80K                                                                                                                           | 25.000c (until<br>EoL)                  |                                                |

| PHV-H3TRP | 72                          | V <sub>DC</sub> =750V, V <sub>peak</sub> =950V,<br>T=85°C, rH=85%                                                                                            |                                         | 1000h                                          |

|           | 24                          | T <sub>cycle</sub> = -20 °C / 85 °C; rH = 93%<br>V <sub>DS</sub> = 400V / 800 V (AC); f = 16.000 Hz t <sub>on</sub><br>= 430 min; t <sub>off</sub> = 170 min | 21d (only SiC)                          | 120d                                           |

| PC        |                             | $T_{vj,max}$ =150°C, $\Delta$ T=80K ton=0.5s // 1.5s // 15s // 60s                                                                                           |                                         | EoL to define<br>t <sub>on</sub><br>dependence |

| TST       | 72                          | T=-40°C – 125°C                                                                                                                                              | 50c                                     |                                                |

- Tests extended beyond standardized test time

- Tests continue to run, to be updated

- Currently no EOL visible (occasional peculiarities, but predominantly not chip related resp. still better than observed with state of the art IGBT technology

- Special application oriented moisture tests added

- AC-HTC special outdoor test

- HV-H3TRB

- PHV-H3TRB

# Why do we need to define new tests – example AC-HTC and HV/PHV-H3TRB

#### HV/PHV-H3TRB

- Traditional moisture test does not reflect real stress in the device → 80V bias for a 1200V device creates just a very small electric field

- Increase of applied voltage and pulse pattern emulate real stress much better and can trigger more failure modes which are not seen with traditional H3TRB, but in the real operating environment

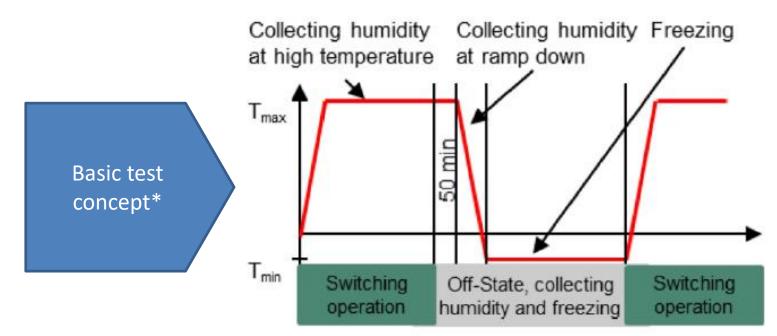

#### AC-HTC

- Solar systems are often located outdoor

- In winter time and during night system is off significant amount of moisture enters the system by bedewing

- If moisture reaches semiconductor surface combined with electric fields anodic oxidation can destroy the chip

- Technological measures developed to counteract moisture penetration

- Qualification process developed to verify effectiveness

- Rolled out to all outdoor relevant products

# Verification test for moisture resistance in solar - AC-HTC test

\*N. Kaminski, "Reliability Challenges for SiC Power Devices in Systems and the Impact on Reliability Testing", Materials Science Forum 2018, Vol.924. pp. 805-810.

### Weak devices usually detected already after a few cycles, test duration currently >100d

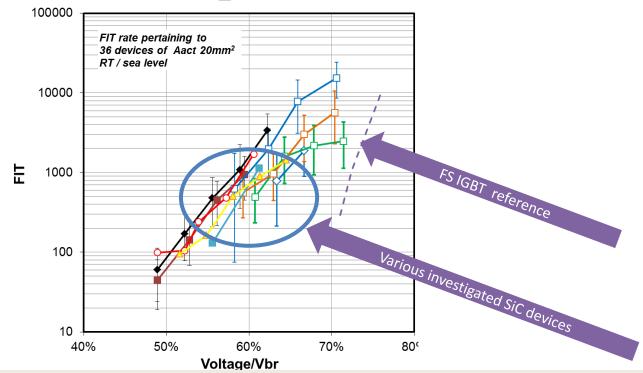

#### Cosmic ray and SiC

- General understanding of cosmic ray :

- Effect (FIT rates) heavily dependent on the actual electric field in the device → typical de-rating via reduced U<sub>DS</sub> in the application

- Case of SiC : about 10x higher internal fields as major benefit → what kind of influence has this on the cosmic ray behavior ?

- Findings :

- Despite the 10x higher electric fields SiC components come close to silicon performance

- Current status of investigations shows that de-rating efficiency is not as good as in silicon due to flatter dependence of FIT on  $U_{max}$  in the application

- Benefit of unipolar MOSFET :

- Adaption of maximum field with much smaller penalty on performance compared to IGBT

# FIT rate vs. $U_{DS}$ related to ACTUAL breakdown voltage (not $U_{DS_{max}}$ from datasheet)

FIT rate depends on electric field, flat slope compared to IGBT observed for the current state of the art

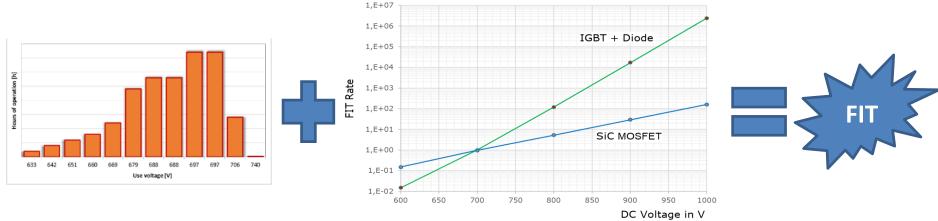

#### Cosmic ray and SiC

- Similar to the procedure in Silicon the device supplier can model cosmic ray fit rates based on experimental results

- With a mission profile given by the customer the FIT rate in a real application can be estimated

- Benefit of SiC vs. IGBT :

- The SiC MOSFET has a smaller active area than the Si IGBT/Diode for the same current.

- The SiC MOSFET does not need a free wheeling diode, which also contributes to CR FIT.

- Note Si FIT rate reduces much more with increasing T<sub>i</sub> than a SiC MOSFET

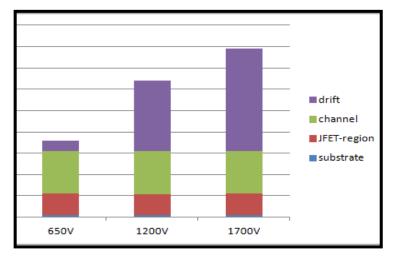

#### Effect of electric field adaption on the expected performance

- Adaption of electric field in order to meet FIT requirements is realized via the drift zone design

- Drift zone in SiC MOSFETs has a less significant contribution to R<sub>on</sub> compared to silicon

#### • Conclusion :

- Adaption of electric field in order to meet FIT rates with less impact

on performance than in silicon

- Mainly dynamic losses nearly not influenced at all

Introduction 2 Qualification methodology for wide bandgap 3 Selected topics on power GaN reliability 4 Selected topics on power SiC reliability 5 Wide bandgap standards Conclusions

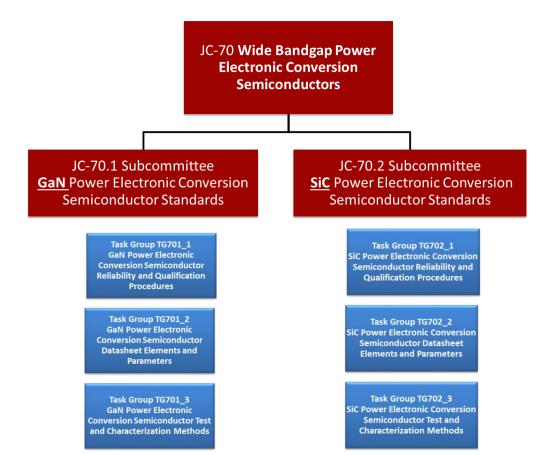

#### Wide bandgap standards JC-70

- **Motivation**: Establishing Wide Bandgap Standards (initially guidelines) is perceived as means to accelerate WBG customer acceptance and therefore is an accelerant to market penetration

- By harmonizing tests, datasheet requirements, reliability and qualification methods across the industry, the customer is assured of the test conditions and procedures thus removing ambiguity and uncertainty in the methodology and the data

- Significant support by Infineon was provided through the early incubation of GaN Standards for Power Electronic Conversion (GaNSPEC) and continued through the transition to JC-70

Introduction 2 Qualification methodology for wide bandgap 3 Selected topics on power GaN reliability 4 Selected topics on power SiC reliability 5 Wide bandgap standards **Conclusions**

### Conclusions

- Four ingredient methodology starting from product mission profile and involving rigorous technology and product reliability evaluation was presented.

- Performing accelerated life tests and modeling of the key failures are key to assure both the manufacturer and the customer of product quality including predicting FIT rate at use conditions.

- Key reliability topics in focus were highlighted for both GaN and SiC Power devices.

- An industry-wide effort to generate Standards (initially Guidelines) is supported by industry to accelerate adoption – also a clear evidence of the ongoing maturity of WBG technologies.