Significant Developments and **Trends in Embedded Substrate** and Component Technologies for Power Applications **Presented by PSMA Packaging Committee Brian Narveson and Ernie Parker, Co-Chairmen**

# **PSMA and 3D Power Packaging**

- Phase 1 Technology Report " 3D Power Packaging" (authored by Tyndall National Institute) determined the power industry was interested in and beginning to manufacture Embedded Substrate power products (published Feb. 2014)

- Phase 2 Technology Report "Current Developments in 3D Power Packaging with Focus on Embedded Substrate Technology" (authored Ltec Corporation) was published in March 2015, determined power supplies can be made now with embedded technology, but a lot more needs to be done.

- Researched 740 published articles from industry, government and academia

- Interviewed 30 Industry and Academic Experts

- Attended 10 trade shows, conferences and seminars

- Phase 3 Technology report on 3D Power Packaging planned for 2017

- PSMA primary financial sponsor of 3D-PEIM Symposium

- Packaging Committee has sponsored 3 Industry Sessions at APEC on 3D Packaging

## What is 3D Power Packaging

- Power supply products derived from the use of the z axis

- Incorporation of a variety of technologies to reduce footprint

- Solutions that increase power density (W/cm<sup>3</sup>)

- Manufacturing solutions that can print or construct interconnects or circuit layers

Embedding Actives or Passives in Substrate

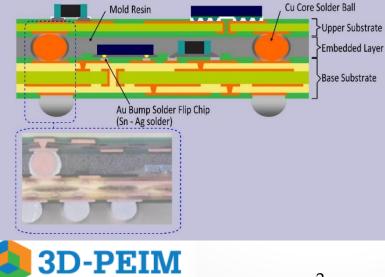

#### What is Embedded Substrate Technology

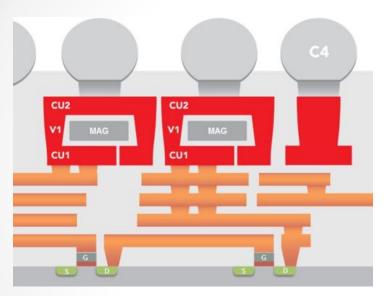

- A 3D Embedded Power Module is a "systems that use a combination of at least one controller/driver IC, at least one active component in the power train, and associated interconnect means, embedded in a single package."

- Component embedding is "the inclusion of at least one active or passive electrical component within the top and bottom conductive layers of a substrate."

- A *substrate* is defined for this study as "a planar structure having multiple conductive and insulating layers."

#### **Embedded Power Market Drivers**

- Digital functionality and power consumption increasing at a rate of "More than Moore"

- CMOS has hit the wall, transistor efficiency is not increasing, and processor clock speeds are stagnating.

- Advanced deep submicron semiconductor technology has hit a cost barrier

- Barrier overcome with a paradigm shift in digital semiconductor packaging

- Leading technologies are wafer thinning, through-silicon vias (TSV) and 2.5D and 3D integration

- Power requirements increasing 2 to 5 times, within the same footprint, in one generation

- Power density and efficiency improvement with wide bandgap galliumnitride (GaN), silicon-carbide (SiC), and gallium-arsenic (GaAs) are facing a "construction barrier"

- Optimum performance can only be achieved with packaging free of bond wires

- Embedded substrate technology is a disruptive technology that can lead to large increases in power density and efficiency, plus higher performance from wide bandgap devices

#### Why is Embedded 3D Packaging Important

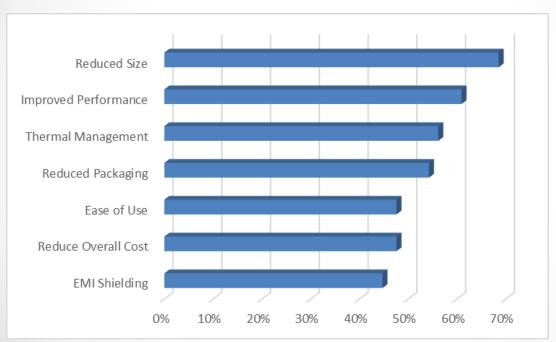

• What you told us: Motivation for using embedded packaging.

#### % of Available Score

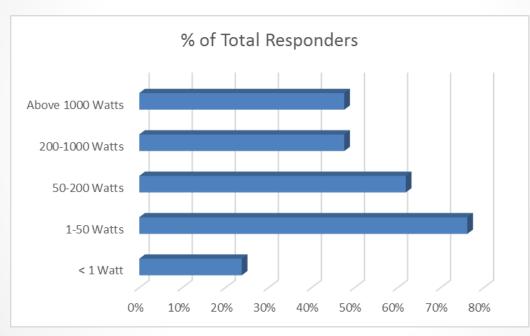

#### At what Power Levels are you Interested?

• What you told us:

7

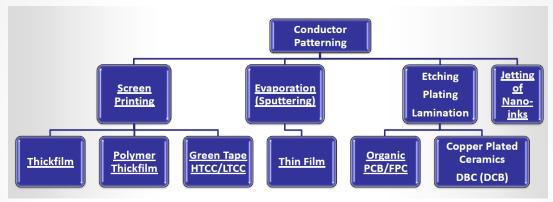

# **Technology Areas Studied**

- PCB's and Inorganic Substrates

- Semiconductors including High Temperature Die Attach and High-lead Solder Substitution

- Passives

- -Resistors

- -Capacitors

- -Magnetics

- Interposers

- Packaging Technologies

- Thermal Management

- Additive Manufacturing

- The phase 2 report is 10 Chapters, 335 pages, with 394 Publications cited and 172 links provided

#### Benefits of Embedded Substrate Technology

- Performance

- Reliability

- Ease of use

- Solution size

- Thermal management

- EMI shielding

- Reduced need for product-specific tooling

- Reduced need for additional packaging

- Fastp time to market

- Cost?

#### Standards for Embedded Substrate Technology

#### Substrates and Components

- IPC-2316: Design Guide for Embedded Passive Device Printed Boards

- IPC-4811: Specification for Embedded Passive Device Resistor Materials for Rigid and Multilayer Printed Boards

- IPC-4821: Specification for Embedded Passive Device Capacitor Materials for Rigid and Multilayer Printed Boards.

- IPC-4101: Specification for Base Materials for Rigid and Multilayer Printed Boards

- IPC-6012: Qualification and Performance Specification for Rigid Printed Boards

- IPC-7092: Design and Assembly Process Implementation for Embedded Components

- JCPA EB01-2013: Parts Built-in Electronic Circuit Board (Component Built-in Board) Data Format Design Guide – 2nd Edition

- JPCA EB02-2013: Standard on Device Embedded Substrate Terminology / Reliability / Test / Design Guide 4th Edition

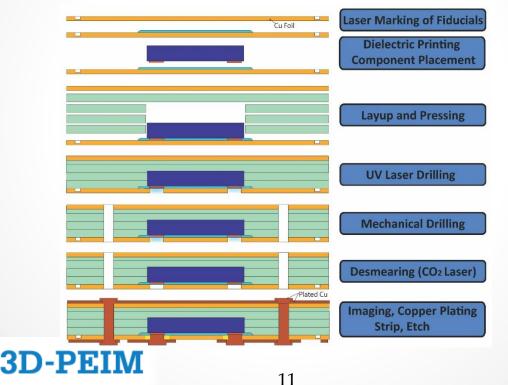

# AT&S Embedded Component Packaging (ECP<sup>™</sup>) Process Flow

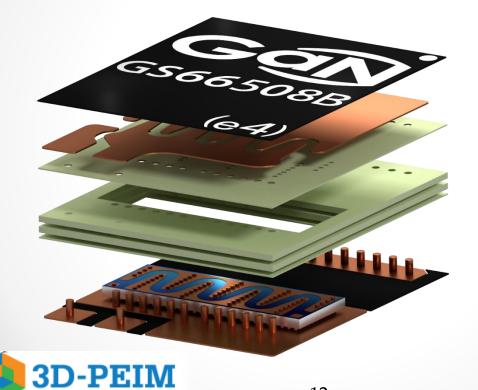

### GaN devices of GaN Systems Inc. embedded in AT&S (ECP<sup>™</sup>) process

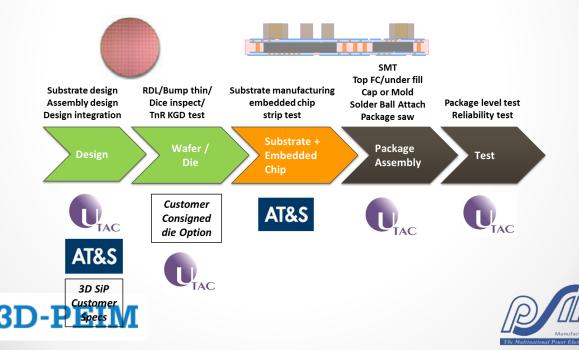

# UTAC and AT&S Collaborate on Turnkey Supply Embedded Chip in Substrate Technology

#### **Collaborative 3D SiP Supply Chain Flow**

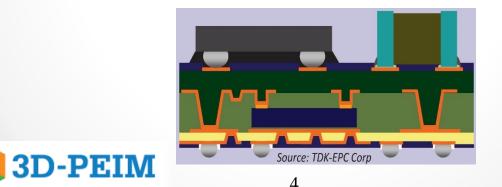

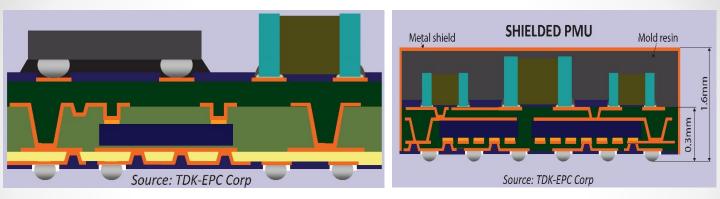

#### **TDK SESUB Process**

#### **3D Pattern Routing in SESUB**

Source: TDK

-Connection among IC and passives all within the module -PGND plane can be isolated from other GND plane -Switching energy can be routed in internal PGND return path -Switcher noise may be reduced by PGND isolation

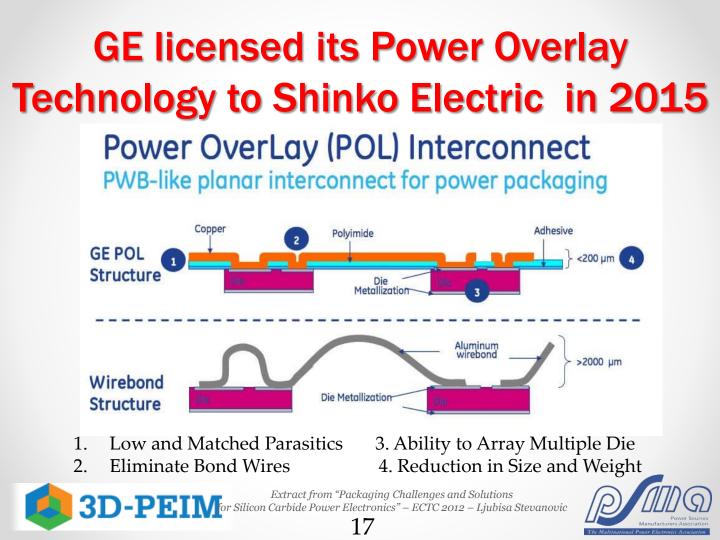

#### **General Electric's Power Overlay Technology**

|                    | ePOL                                                                          | WPOL                                                                                                                                                                                                | POL-MCM                                                                                                                                                                                   | POL-kW                                                                                                                                            |  |  |  |

|--------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DESCRIPTION        | Low-cost embedded<br>package leveraging high<br>volume PCB technologies       |                                                                                                                                                                                                     |                                                                                                                                                                                           | Ultra high power module<br>with leaded connectors<br>and advanced thermal<br>management                                                           |  |  |  |

| FEATURES, BENEFITS |                                                                               | Low to medium I/O, 400<br>single & MCM applications<br>with min. L/S 10/10um<br>30+ Volt<br>- Large sized POL frame<br>processing, enabling<br>excellent routing<br>capability<br>- Ultra thin, low | Medium Voltage ,1200V<br>- Multiple pwr devices and<br>ICs (10+)<br>- Multiple passives (30+)<br>- Low parasitics<br>- Heterogeneous die<br>integration combining<br>both power and logic | Higher power<br>1200V+<br>- Lowest possible parasitics<br>fast switching, low losses<br>- Double sided cooling,<br>superior thermal<br>management |  |  |  |

| APPLICATIONS       | Mobile, computing,<br>telecom<br>- Wireless<br>- RF FEM<br>- Power management | Mobile, computing,<br>telecom<br>- Wireless<br>- RF FEM<br>- power management                                                                                                                       | Computing, telecom,<br>industrial<br>- DC-DC converter<br>- Intelligent power<br>modules                                                                                                  | Automotive, aerospace,<br>- Motor drives<br>- Renewables<br>- High power conversion                                                               |  |  |  |

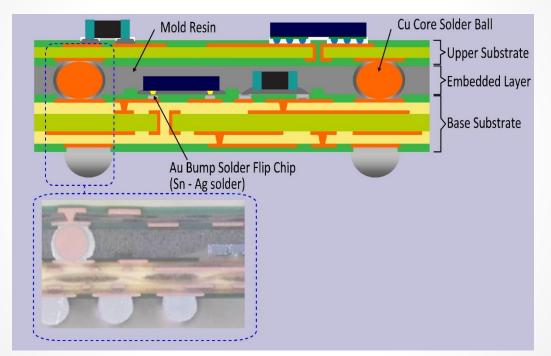

# Shinko Electric's Molded Core Embedded Package (MceP<sup>®</sup>)

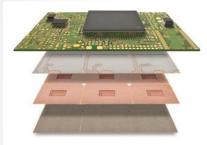

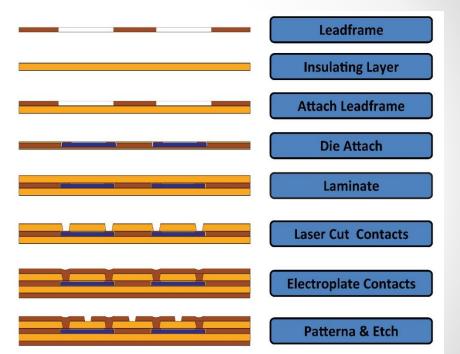

#### Schweizer's P<sup>2</sup>-PAK approach

p<sup>2</sup> Pack® module assembly with logic PCB

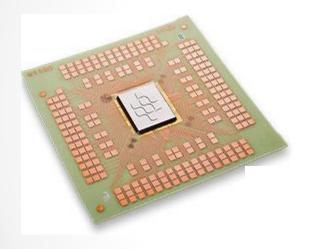

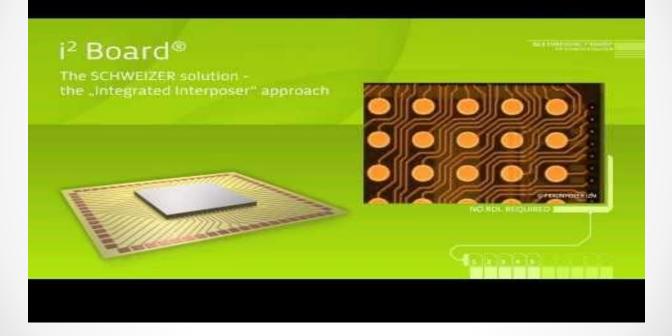

#### Schweizer's i<sup>2</sup> Board® approach

-Design an interposer board for embedding in host PCB -Interposer can contain both passives and actives -Conventional surface mount components can be embedded using the interposer

#### Schweizer's i<sup>2</sup> Board® approach

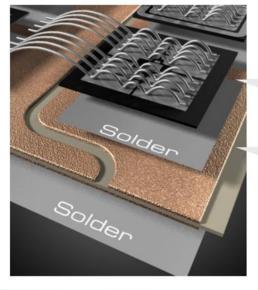

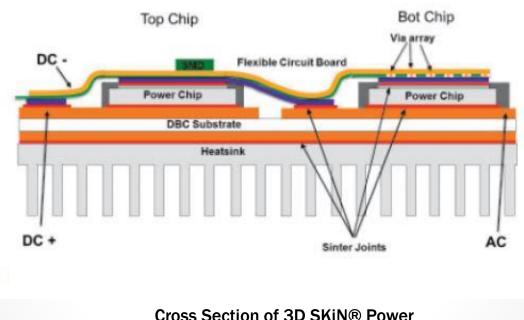

#### **Semikron's Sintered SKiN<sup>™</sup> PROCESS**

#### Standard Technology

#### **Semikron's Sintered SKiN<sup>™</sup> PROCESS**

Module with Sintered Joints

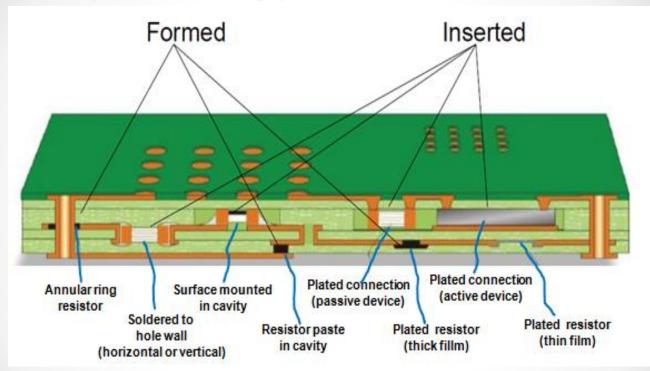

## **Component Types and Processes**

Example of an embedded assembly Source: IPC **3D-PEIM** International Technology Roadmap

24

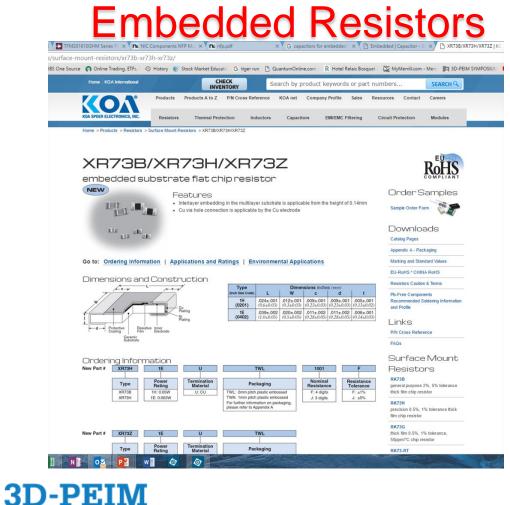

#### Resistors

#### Formed Technologies

Source: Micro Consulting Services

#### Inserted-Suppliers of embeddable resistors

- -KOA Speer Electronics, Inc

- -Aeroflex (A Cobham Company)

- -Panasonic

- Stackpole Electronics, Inc.

- -Vishay Intertechnology, Inc

- -Ohmega Technologies, Inc.

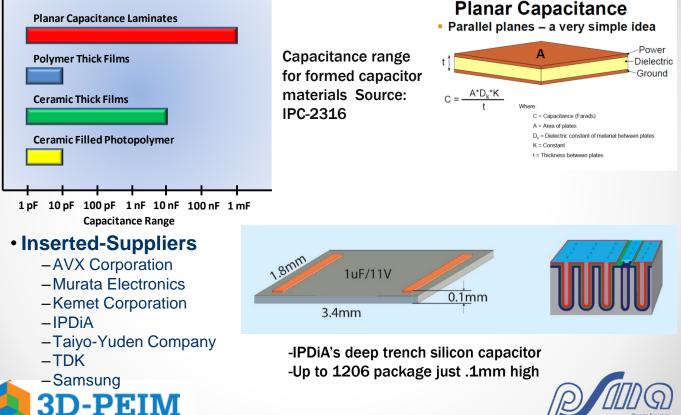

### Capacitors

#### Formed Technologies

#### **Embedded Capacitors**

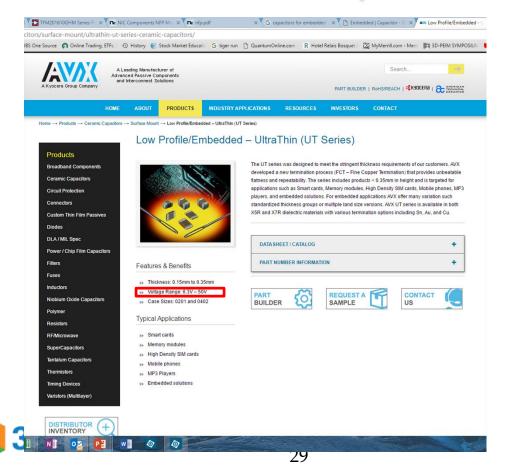

#### Embedded

Due to its low ESL characteristics, the products can be used as decoupling capacitors to supply current to the high-speed application processors (APs) of mobile devices (smartphones, tablet PCs) efficiently and stably.

The products are embedded inside substrates to correspond to devices or modules, securing mounting space. In addition, they help remove high-frequency noise, suffering less effects from external environmental stress.

#### General Features

Low ESL, Enhancing adhesive strength to epoxy

Various thickness 0.11mm ~ 0.33mm, Temperature range -55°C to +85°C, Case size 0603 to 1005

#### Application

FCBGA for application processor, PMIC module, Wearable devices

28

CATALOG DOWNLOAD

CATALOG DOWNLOAD

CONTRIBUTORS

CONTRIB

#### **Embedded Capacitors**

### Inductors

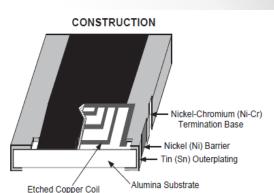

#### Formed Technologies

-NEC-Tokin flake magnetic material -Bel Fuse embedded transformers -Planar Magnetics

#### Inserted-Suppliers of embeddable inductors

- -Taiyo Yuden Co., Ltd

- -Coilcraft, Inc.

- –NTI Components Corporation –TDK-EPC

- –Kemet Electronics, Inc.–KOA Speer Electronics, Inc.

- -NEC-Token

DK thin film inductor

Bel Fuse Internal embedded multiple transformer construction

30

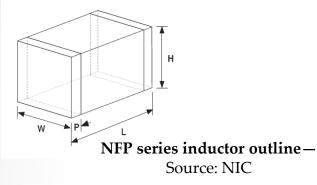

#### Inductors – Present Devices for Emedding

**DIMENSIONS (mm)**

| Case Size | L                 | W                 | Н                 | Р                |

|-----------|-------------------|-------------------|-------------------|------------------|

| 0603      | 1.6 <u>±</u> 0.15 | 0.8 <u>+</u> 0.15 | 0.5 <u>±</u> 0.1  | 0.3 <u>±</u> 0.2 |

| 0003      |                   |                   | 0.8 <u>+</u> 0.15 |                  |

|           | 2.0 +0.3/-0.1     | 1.25 ± 0.2        | 0.5 <u>±</u> 0.1  | 0.5 ± 0.3        |

| 0805      |                   |                   | 0.9 ± 0.1         |                  |

|           |                   |                   | 1.25 <u>+</u> 0.2 |                  |

| 0806      | 2.0 +0.3/-0.1     | 1.6 ± 0.2         | 0.9 ± 0.1         | 0.5 ± 0.3        |

| 0000      |                   |                   | 1.1 <u>+</u> 0.1  |                  |

| 1008      | 2.5 ± 0.2         | 2.0 +0.3/-0.1     | 0.9 <u>±</u> 0.1  | 0.5 ± 0.3        |

| 1000      |                   |                   | 1.1 <u>+</u> 0.1  |                  |

NTI thin film inductor construction — Source: NIC

# Ferric Inc. Magnetic Core Inductors

Process and designs are integrated on top of the chip or interposer

Flexibility in integration and implementation.

Ferric's magnetic core topologies provide >5A/mm<sup>2</sup> current density and utilization factor near 100%

- Electrical Test

- •Yield

- •Who owns the failure

- •How do share the losses

- Passives at rating and values we need

# Summary

- The digital world is going 3D to increase capability in the same footprint

- Digital 3D will greatly increase the need for power but not increase the available space to implement it

- Embedded Substrate technology is a viable path to increase power density

- Multiple substrate and semiconductor technologies are available at many power levels

- Both formed and inserted components are available from multiple suppliers

- Multiple power manufactures are shipping product utilizing embedded technology

- Less than 5% of the material in the reports has been presented. Contact PSMA to find out how to get a copy.

# Want to Participate or Learn More

- Participate in PSMA Packaging Committee

- Planning a Phase 3 3D-Packaging Technical Report in 2017

- Exact content will be discussed this fall

- Planning 3D Power Packaging Industry session at APEC 2017 in Tampa Florida, March 26-30 2017

- We are determining topics and recruiting speakers now

- Discussion of whether to hold another 3D-PEIM.

- Let us know if you would be interesting in hosting or participating on the organizing or technical committees

- If you would be interested in participating in committee meetings please contact <u>bcnarveson@gmail.com</u>. (PSMA membership encouraged but not required)

#### **Thank You**