# ipdia

## The 3D Silicon Leader

High performing wire bondable vertical Silicon Capacitors for RF power modules

3D PEIM 2016 Raleigh Catherine Bunel 2016 June 15

#### Content

- Introduction

- Technology

- WBSC Capacitor structure

- Performances

- Reliability

- Conclusion

#### Who are we?

- Independent European High Tech Company

- Specialized in leading edge Integrated Passive Devices, world leader in 3D Silicon capacitors

- Operating own 10 000 m<sup>2</sup> Silicon wafer facility

- 25% of financial resources allocated to R&D

- 25% of sales in EU, 25% US, 50% Asia

- Technology adopted by 3 of the top 5 leaders in medical electronics as well as by key players in the semiconductor area and Hi-Rel industry

#### Introduction

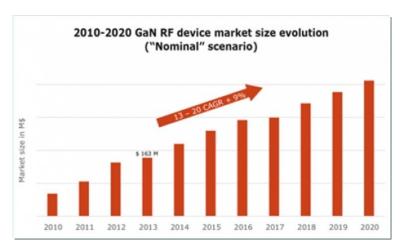

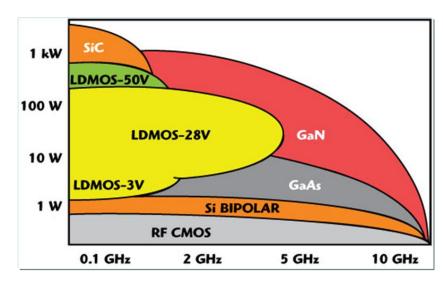

- The need for high-power and high frequency transistors is increasing.

- GaN has progressed significantly over the last years

- GaN device portfolio is covering a wide range of applications.

- LDMOS performance is continuously pushed to its limits.

www.semiconductor-today.com

www. microwave journal.com

#### Requirements for RF products:

- High efficiency

- High bandwidth and linearity

- High polarization voltage

- Low cost

- High reliability

- Smaller footprint

## Value proposition of the 3D Si capacitors:

- Proper decoupling of the power supply :quick, smooth response to the large current demands of the output circuit.

- Low parasitic loss.

- High capacitance density with high voltage

- Small footprint and low profile

- High performance and power efficiency by using larger capacitor value in a small package

- Cost saving due to the package size reduction.

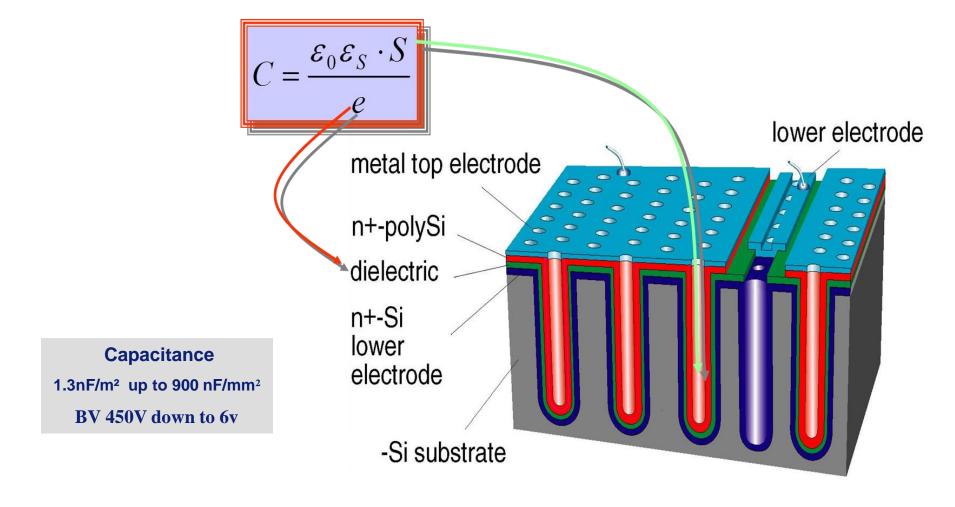

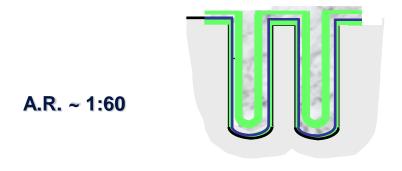

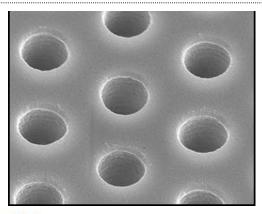

### **3D Capacitor Technology**

## **3D Capacitor Technology**

1.3nF/mm<sup>2</sup> up to 6nF/mm<sup>2</sup> VBD = 450V down to 150V

20nF/mm<sup>2</sup> up to 900nF/mm<sup>2</sup> VBD min = 100V down to 6V

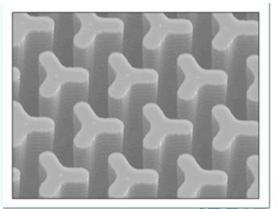

**Nitride Double stack**

**Tripods**

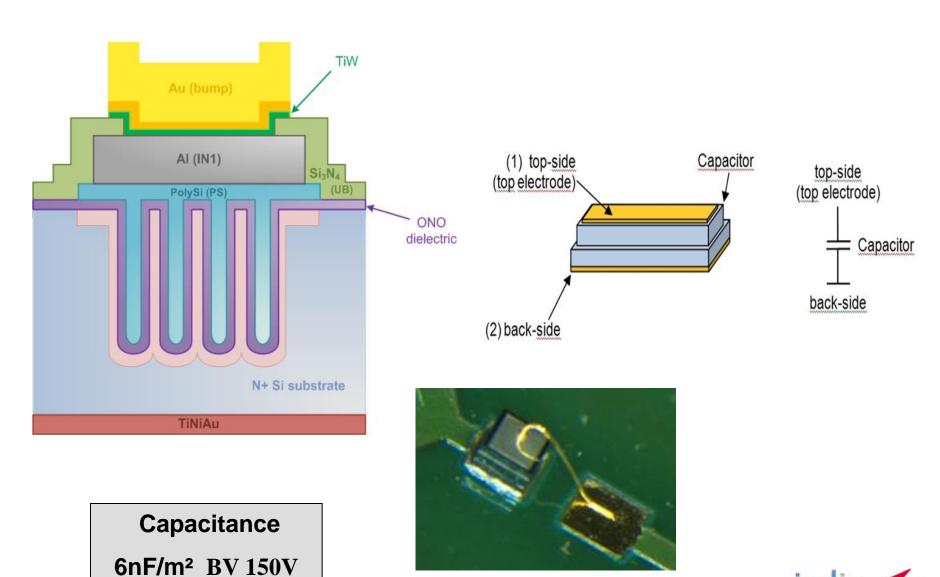

### **Vertical 3D Silicon Capacitors**

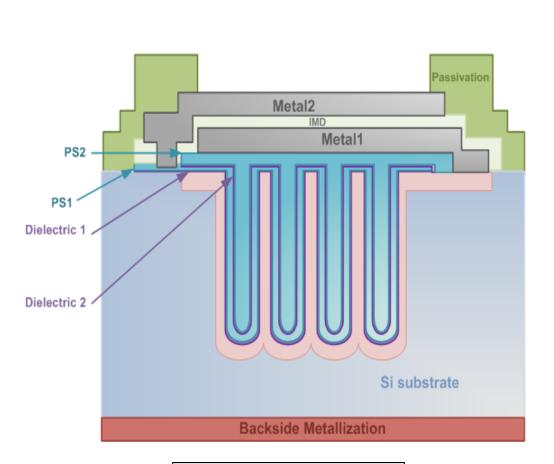

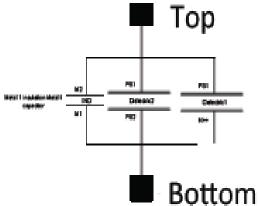

### **Vertical 3D Silicon Capacitors**

Capacitance

20nF/m<sup>2</sup> BV 100V

### Low profile

Large range of die thickness from 100μm up to 400μm TiW Au (bump) AI (IN1) Si<sub>3</sub>N<sub>4</sub> PolySi (PS)  $100 \mu m - 400 \mu m$ ONO dielectric → Selected thickness depends on the Backside Metallization and N+ Si substrate the package constraints **TiNiAu**

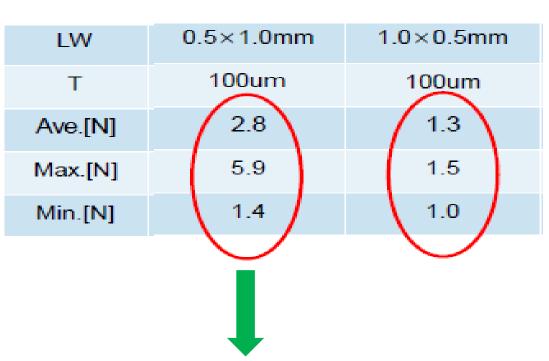

## Capacitor strength comparison between Ceramic and Silicon cap

#### Results after bending strength 3 points

**IPDIA SI CAP**

Ceramic CAP

0402 100nF 100µm thick Silicon Capacitor is stronger than Ceramic Capacitor

### Topside and backside metallization

- Topside: 3 to 5µm

- Pure Aluminum

- AlSiCu

- TiWAu

- TiCuNiAu T° >150° C, hermetic package

- Backside Metal : 3µm

- Pure Au

- TiNiAu

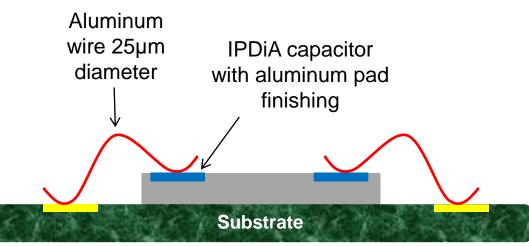

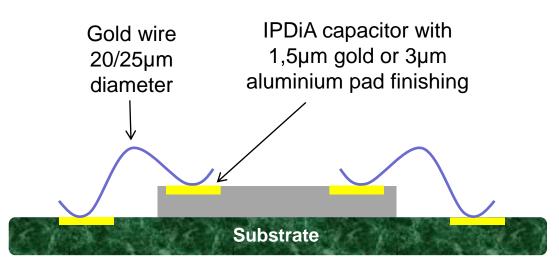

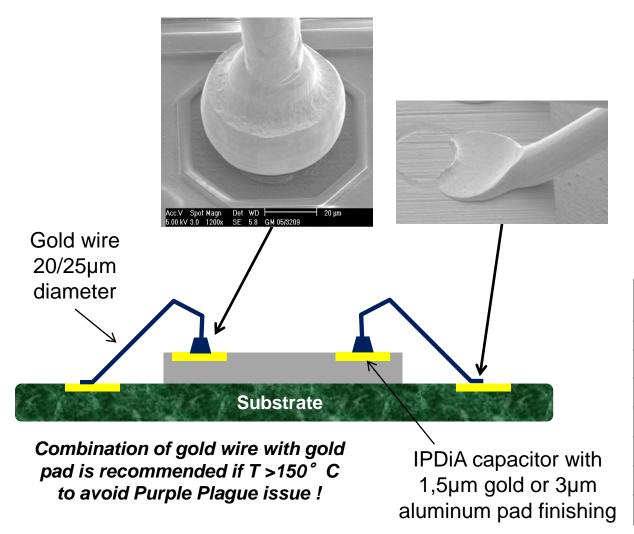

## Wire bondable vertical Silicon Capacitor:

- Wedge bonding

- Au wires

- Al wires

- Ball bonding

- Au wires

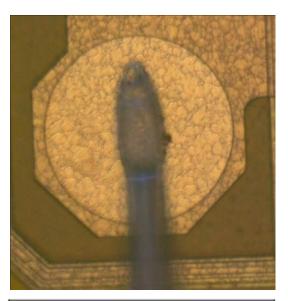

### Wedge bonding – Aluminum wire:

| Bonding process: Wedge Alu |                                      |  |  |  |

|----------------------------|--------------------------------------|--|--|--|

| Bonder                     | BJ820                                |  |  |  |

| Bonding Tool               | CCNOE-1/16-1"-45-C-2020-MP           |  |  |  |

| Wire                       | AL1%Si-SR-25-1-4%-17-19gf-12AL (SPM) |  |  |  |

| US                         | 20% (400-440 mW)                     |  |  |  |

| Force                      | 17 cN                                |  |  |  |

| Bonding time               | 10 ms - 20 ms                        |  |  |  |

| Deformation                | 25 - 35%                             |  |  |  |

| Temperature                | Ambiant                              |  |  |  |

Combination of aluminum wire with aluminum pad is recommended if T >150° C to avoid Purple Plague issue!

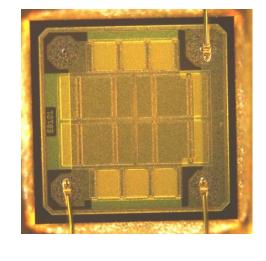

#### **Wedge bonding – Gold wire**

| Bonding process: Wedge/Gold wire |                                      |  |  |  |

|----------------------------------|--------------------------------------|--|--|--|

| Bonder                           | BJ820                                |  |  |  |

| Bonding Tool                     | FP45B-TI-2015-1.00-CGM               |  |  |  |

| Wire                             | Heraeus Au AW14<br>(>17cN et 0,5-3%) |  |  |  |

| us                               | 20 - 30% (420 -600 mW)               |  |  |  |

| Force                            | 20 – 30cN                            |  |  |  |

| Bonding time                     | 20ms                                 |  |  |  |

| Deformation                      | 25 – 35%                             |  |  |  |

| Temperature                      | 115°c                                |  |  |  |

Combination of gold wire with gold pad is recommended if T >150° C to avoid Purple Plague issue!

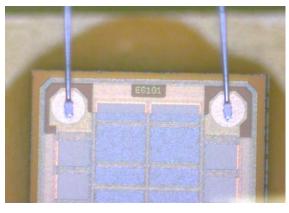

### **Ball bonding – Gold wire**

| Ball bonding/Gold wire |                              |  |  |  |

|------------------------|------------------------------|--|--|--|

| Bonder                 | 5810 BONDTEC                 |  |  |  |

| Bonding Tool           | UTS-38HG-AZM-1/16 16mm (SPT) |  |  |  |

| Wire                   | Heraeus HD2 (>7cN,2-6%)      |  |  |  |

| US                     | 215 – 230 mW                 |  |  |  |

| Force                  | 30 – 40 g                    |  |  |  |

| Bonding time           | 24 ms                        |  |  |  |

| Temperature            | 125°c                        |  |  |  |

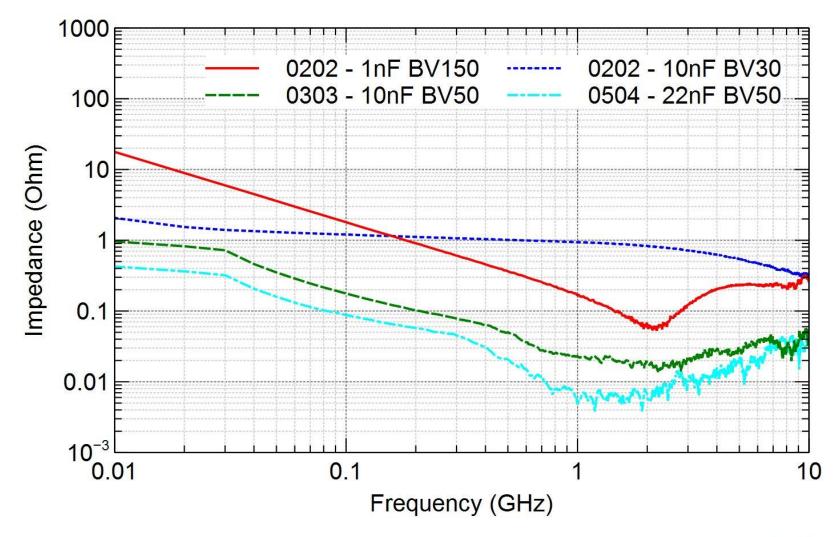

### **RF** performances

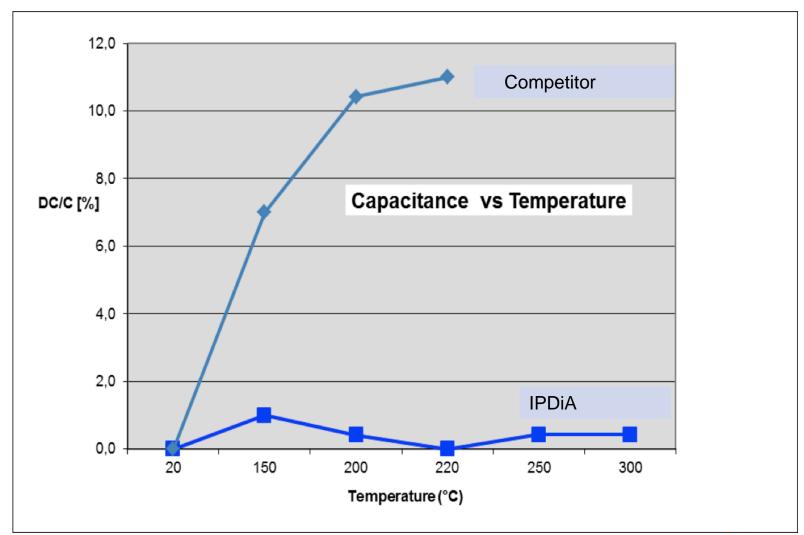

### Temperature behaviour of Si Caps

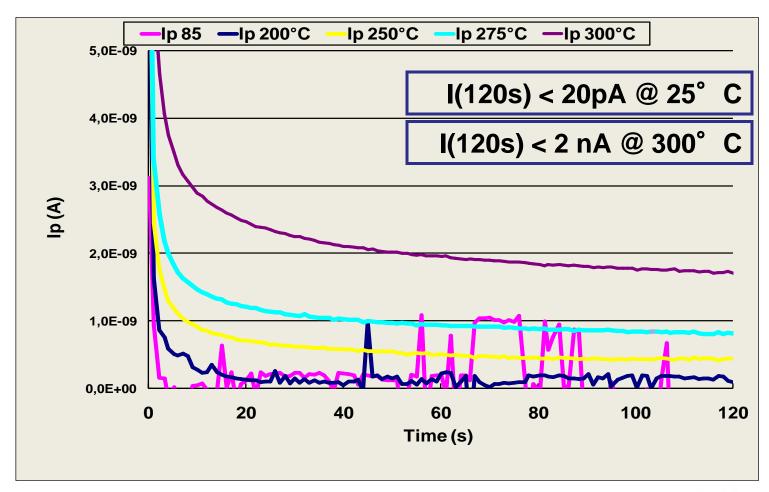

#### DC leakage current at high Temperature

C= 100nF (Amps @ 3V)

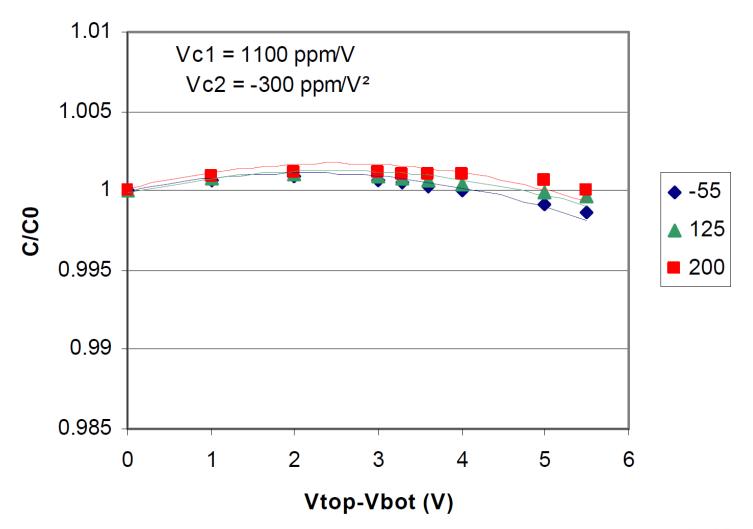

## Capacitance dependance on DC bias and temperature

#### **Performances**

- Low leakage current <1nA/mm²</li>

- Excellent temperature and voltage linearity

- High volume efficiency

- Low ESR , low ESL

#### **IPDiA Capacitor failure mode**

- Dielectric wear out accelerated under high voltage or high temperature conditions, getting visible by an increase of the leakage current to end up with a short.

- The main sensitivity or « degradation » factor is the increase of electrical field (voltage).

- There is no early failure

- The lifetime of 100 nF 0605 capacitor exceeds 18 000 hours at 200 °C.

- As a comparison, X8R capacitors show a useful life of 10 000 hours at 125° C at the rated voltage.

#### **Lifetime: Predictive models**

$$t_{bd} = A_0 \cdot \exp(\frac{E_{Ao}}{kT}) \cdot \exp(-\gamma \cdot E_{ox})$$

- $\rightarrow$  A<sub>0</sub> = time constant

- $\rightarrow$  E<sub>Ao</sub> = activation energy (eV) determined from the TDDB test

- $\rightarrow$  k = Boltzmann constant (8.6  $\times$  10-5 eV/K)

- $\rightarrow \gamma$  = field acceleration factor

- $\rightarrow$  E<sub>ox</sub> = field across the oxide given by the ratio of the applied voltage to thickness of the dielectric

#### PICSHV150

| Vg (V) | 37℃          | 100℃        | 150℃       | 225℃       |

|--------|--------------|-------------|------------|------------|

| 30     | 496676 years | 36581 years | 8022 years | 1458 years |

| 45     | 20090 years  | 1480 years  | 324 years  | 59 years   |

| 60     | 813 years    | 60 years    | 13 years   | 2.4 years  |

| 75     | 33 years     | 2.4 years   | 194 days   | 35 days    |

Lifetime predictions at different values of stress voltage and temperature using the TDDB E-model at 0.1% cumulative failure

## Take away on reliability

- IPDiA technology is facing numerous success stories with the high reliability top players.

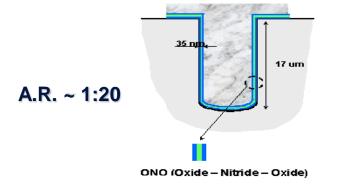

- This technology is featuring a composite ONO dielectric

- Si3N4 boost capacitance density

- Thermal oxide barriers enhance leakage and wear-out performance

- Wear out of the Capacitor is similar to CMOS

- Failure mechanisms are similar to FET gate

- Predictive reliability models (tddb) are available accounting for T and V derating

- EFR screening is part of the wafer test setup

- Does not require component burn-in

- No ageing

- No cătastrophic failures

- Not sensitive to moisture

## **Reliability results**

| Stress test                                | Abbr. | Stress Conditions                                  | Stress<br>Duration | Results               |

|--------------------------------------------|-------|----------------------------------------------------|--------------------|-----------------------|

| Life time at V use                         | TDDB  | 3T° & 3 Voltages                                   |                    | > 10 years<br>@ 100°C |

| Failure in Time                            | FIΤ   | 150°C                                              |                    | <1 @225°C             |

| High Temperature<br>Operational Life       | HTOL  | 150°C,Vuse                                         | 1008 hrs           | 0 failures            |

| Thermo-mechanical cycling                  | тс    | -65°C /+150°C                                      | 500<br>cycles      | 0 failures            |

| High Temperature<br>Storage Life           | HTSL  | 150°C,unbiased                                     | 1008 hrs           | 0 failures            |

| Unbiased Highly<br>Accelerated Stress Test | UHAST | Preconditioning<br>MSL3 260°C, 85%<br>RH, unbiased | 1056 hrs           | 0 failures            |

| Temperature Humidity<br>Bias Life Time     | THB   | 85°C,85%RH,V use                                   | 1008 hrs           | 0 failures            |

| Metallization Stress voiding               |       | 200°C                                              | 168 hrs            | 0 failures            |

| Stress Migration(stress induced voiding)   |       | 200°C                                              | 904 hrs            | 0 failures            |

| Corrosion                                  | THNB  |                                                    | 168 hrs            | 0 failures            |

| Passivation integrity                      |       | 45°C, H3PO4 or electroless NiAu                    | 40 mn              | 0 failures            |

#### **Conclusion**

- The need for high-power and high frequency transistors is increasing

- The miniaturization of the RF power modules is a must

- The WB Silicon Capacitor is providing performiniaturization: a combination of high performance and power efficiency thanks to low parasitics and high capacitance in a very small package on top of an outstanding reliability.

## Thank you for your attention!