# Decomposition and Electro-Physical Model Creation of the CREE 1200V, 50A 3-Ph SiC Module

3D-PEIM 2016 - Tuesday June 14, 2016

Speaker: Adam Morgan

Authors: Adam Morgan, Yang Xu Dr. Wensong Yu, Dr. Iqbal Husain, Dr. Douglas C. Hopkins

Emails: ajmorga4@ncsu.edu, yxu17@ncsu.edu, wyu2@ncsu.edu, ihusain2@ncsu.edu, dchopkins@ncsu.edu

dchopkins@ncsu.edu

NC STATE UNIVERSITY

### **Introduction – Motivation & Application**

#### NC STATE UNIVERSITY

PACKAGING RESEARCH IN ELECTRONIC ENERGY SYSTEMS

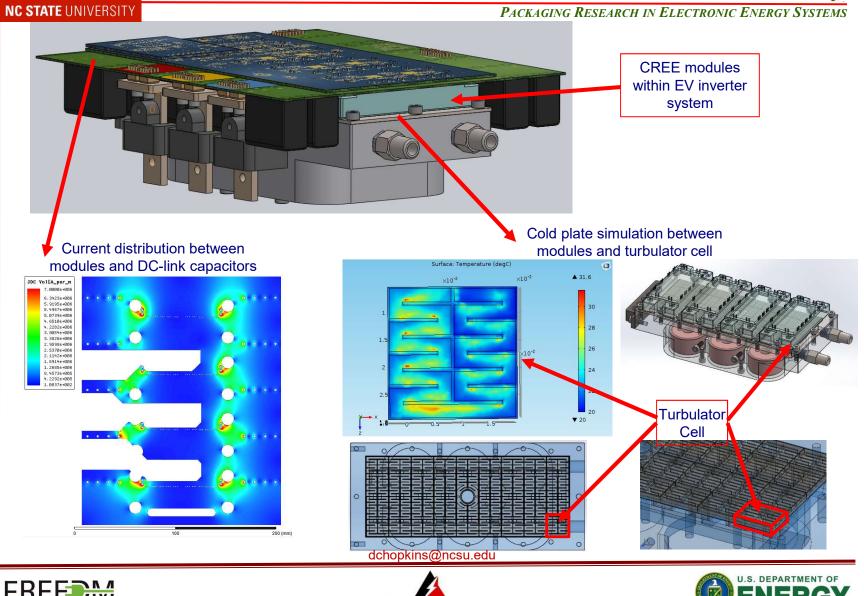

Development of an automotive EV inverter platform using WBG semiconductor power devices in an "open-source" manner

- DoE 2020 target for power density is 13.4 kW/L, achievable with WBG devices

- Enables shrinking of passive components → improvements over similar Sibased EV inverter systems:

- Volume reduction: 56%

- Weight reduction: 51%

- Loss reduction: 48%

- Simulate WBG-based power modules within their systems in order to witness multi-physical performance improvement → justify the cost, stimulate adoption

### **Tear-Down Approach of the CREE Module**

#### NC STATE UNIVERSITY

ILE **PREES** Laboratory

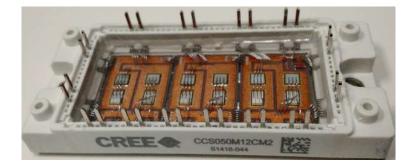

CREE Module: 1200V/50A, 25mΩ

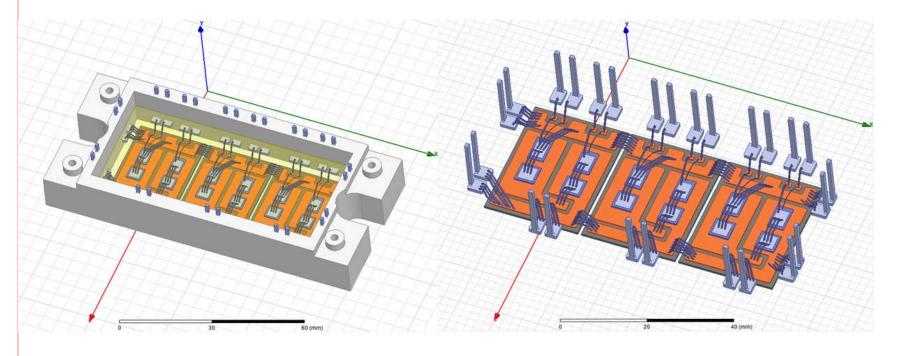

6-Pack SiC MOSFET module (CCS050M12CM2)

- Reverse-engineering technique is developed and applied to the CREE Module power stage

- Hesse Mechatronics BJ939 Heavy Wire/Ribbon Bonder digital camera system, accurate to within 10µm, was used to measure die, interconnect, and substrate length and width dimensions

• For opaque modules, use a minimal parasitic test circuit to analyze switching waveforms, compare with device datasheets, extract parasitic parameters

### **Tear-Down Approach of the CREE Module**

#### NC STATE UNIVERSITY

**PREES** Laboratory

PACKAGING RESEARCH IN ELECTRONIC ENERGY SYSTEMS

- Non-destructive measurement procedure was developed in order to not disturb the power stage of the power module and allow it to still be used in converter circuits after analysis

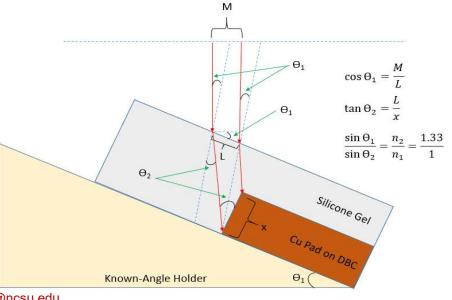

- Initial heights and thicknesses were measured through a 45° angled holder

- Trigonometric relationships in conjunction with Snell's Law were used for determining the internal layer thicknesses of the substrate and die

- 1. Place the opened module onto the known angled holder within BJ939

- 2. Use camera system target reticle to measure the horizontal distance, between the top and bottom edges of each material layer

- Calculate layer thicknesses using trigonometric relationships and Snell's Law

### **Destructive Tear-Down Validation**

#### NC STATE UNIVERSITY

PACKAGING RESEARCH IN ELECTRONIC ENERGY SYSTEMS

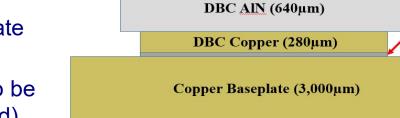

SiC MOSFET, JBS Diode

(180µm, 380µm)

DBC Copper (280µm)

PREES

Laboratory

Solder (50µm)

Solder (50µm)

- CREE module was disassembled and manually measured to within ±25.4µm (1mil), to validate the measurement procedure

- Solder layers were assumed to be 50µm (SEM technique not used)

| DBC AlN   | Nondestructive | Destructive | % Error |

|-----------|----------------|-------------|---------|

| Thickness | 24.2 mils      | 25 mils     | 3.2 %   |

| Length    | 1210 mils      | 1236 mils   | 2.1 %   |

| Width     | 885 mils       | 902 mils    | 1.9 %   |

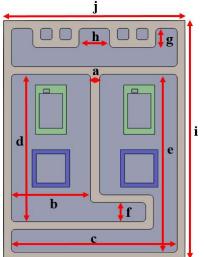

| Dimension | Size (mm) |

|-----------|-----------|

| a         | 1.2       |

| b         | 10.3      |

| с         | 21.6      |

| d         | 19.24     |

| e         | 23.24     |

| f         | 2.5       |

| g         | 2.5       |

| h         | 4.0       |

| i         | 31.24     |

| j         | 23.6      |

#### NC STATE UNIVERSITY

PACKAGING RESEARCH IN ELECTRONIC ENERGY SYSTEMS

- Complete 3D-CAD model of the power stage, based on the measured dimensions, was created in SolidWorks

- Model includes the module housing, baseplate, die attachment, DBC substrate, wire bonds, SiC MOSFETs and diodes, and terminals

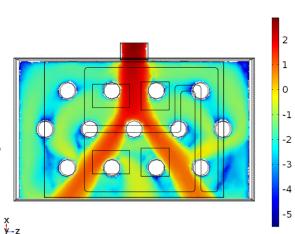

### **Parasitic Extraction & Current Distribution**

| Phase | Freq.<br>(Hz) | DC    | 10k   | 100k  | 1M    | 10M   | 100M  |

|-------|---------------|-------|-------|-------|-------|-------|-------|

| А     | L(nH)         | 115.7 | 102.2 | 83.66 | 78.91 | 74.16 | 73.43 |

| В     | L(nH)         | 81.73 | 74.8  | 61.9  | 56.52 | 54.78 | 54.22 |

| С     | L(nH)         | 47.39 | 46.49 | 40.89 | 37.41 | 36.23 | 35.86 |

| А     | R(mΩ)         | 7.33  | 8.13  | 12.49 | 47.26 | 73.16 | 219.1 |

| В     | R(mΩ)         | 6.11  | 6.61  | 9.83  | 20.76 | 55.55 | 165.6 |

| С     | R(mΩ)         | 4.54  | 4.71  | 6.56  | 13.44 | 35.48 | 105.3 |

|       |               |       |       |       |       |       | dchon |

| Phase | Freq.<br>(Hz) | DC    | 10k   | 100k  | 1M    | 10M   | 100M  |

|-------|---------------|-------|-------|-------|-------|-------|-------|

| А     | L(nH)         | 43.37 | 42.20 | 36.21 | 32.76 | 31.61 | 31.24 |

| В     | L(nH)         | 51.52 | 48.72 | 40.46 | 36.54 | 35.25 | 34.85 |

| С     | L(nH)         | 41.56 | 40.44 | 34.80 | 31.56 | 30.48 | 30.13 |

| А     | R(mΩ)         | 4.83  | 4.98  | 6.90  | 14.12 | 37.28 | 110.6 |

| В     | R(mΩ)         | 5.04  | 5.31  | 7.59  | 15.64 | 41.34 | 122.7 |

| С     | R(mΩ)         | 4.76  | 4.90  | 6.79  | 14.13 | 37.72 | 112.5 |

## **SPICE Model Development & Transient Characterization**

#### NC STATE UNIVERSITY

PACKAGING RESEARCH IN ELECTRONIC ENERGY SYSTEMS

Laboratory

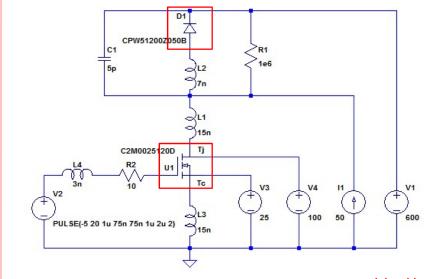

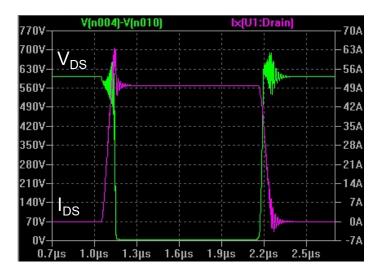

- Double-pulse test circuit simulated in LT- SPICE around the CREE module SiC MOSFET and JBS diode device models

- Major extracted parasitic parameters from ANSYS Q3D Extractor were included to observe packaging influences on transient performance

- Series parasitic inductance extending from the MOSFET has been modeled as 15nH on each side of the source and drain

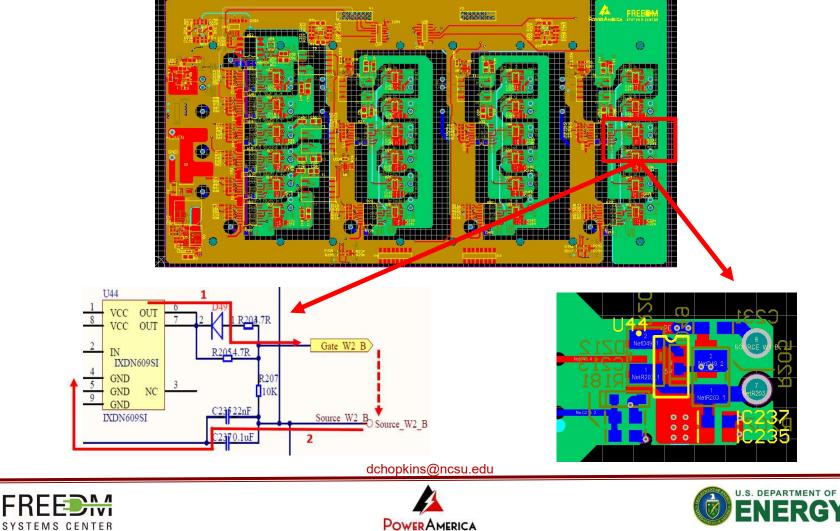

### **Parasitic Analysis of Altium Designer PCB**

#### NC STATE UNIVERSITY

PACKAGING RESEARCH IN ELECTRONIC ENERGY SYSTEMS

Electro-physical non-ideality interactions with connected gate drive PCB

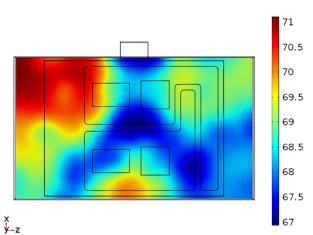

### **Thermal Model Extraction**

#### NC STATE UNIVERSITY

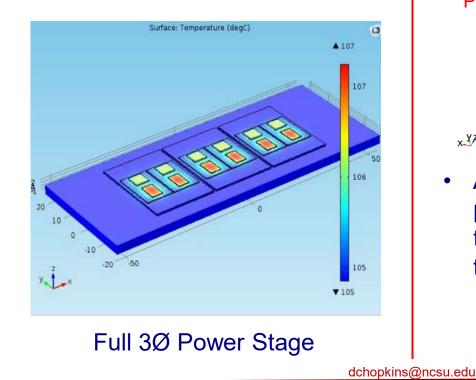

Surface: Temperature (degC)

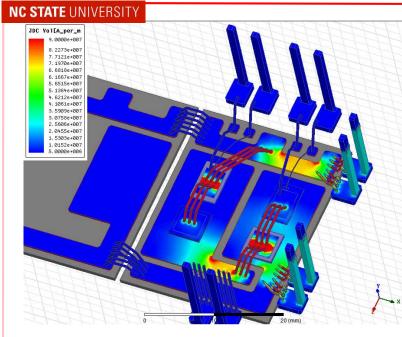

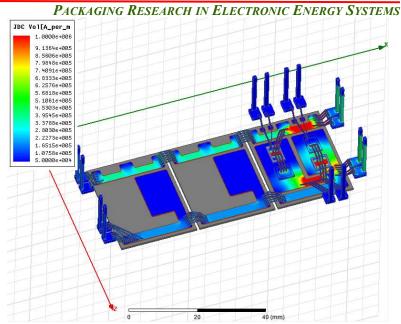

Multi-physics simulator provides in-situ thermal maps of the power stage for various application scenarios

### Single Phase-Leg

A thermal interface material and pin fin heat sink to capture the thermal spreading from junction to case

$R_{th,JC_D} = 0.41^{\circ}C/W$

R<sub>th,JC M</sub> = 0.47 °C/W

### **In-Situ Thermal Application Example**

#### NC STATE UNIVERSITY

**PREES** Laboratory

#### PACKAGING RESEARCH IN ELECTRONIC ENERGY SYSTEMS

### **Simulation Conditions**

- Thermal Interface material

- Thickness = 100µm

- Thermal conductivity = 1 W/m-K

- Pin-fin heat sink water inlet velocity = 0.1L/s

- Model is capable of yielding a detailed thermal map for a given TIM and heat sink application

- Vertical thermal profiles through the power stage are decomposed to capture the thermal spreading from junction to case

- Gain insight into what cooling method to use based upon the applied conditions to the back side of the CREE module

Slice: Temperature (degC)

Slice: Velocity magnitude

### **Large System Application Example**

### **Summary**

### NC STATE UNIVERSITY

Laboratory PACKAGING RESEARCH IN ELECTRONIC ENERGY SYSTEMS

PREES

- The developed non-destructive reverse engineering technique allows for an electro-physical model of the CREE module to be created

- Design engineers can use this open-source model to better understand WBG device performance within their systems

- Systems designed around Si-based technology can now be tailored to WBG-based technology → harness full capability of WBG devices

### Potential Design Applications

- Better understand how their level 2+ system packaging affects the electrical behavior of the WBG devices

- In-depth insight into how generated heat, under a given operating point, is spreading throughout the entire power stage

- Improve overall system robustness using simulation to design against:

- Harmful current and voltage overshoots

- Devices exceeding their allowable junction temperature

### Acknowledgements & Disclaimer

PACKAGING RESEARCH IN ELECTRONIC ENERGY SYSTEMS

The information, data, or work presented herein was funded in part by the Office of Energy Efficiency and Renewable Energy (EERE), U.S. Department of Energy, under Award Number DE-EE0006521 with North Carolina State University, PowerAmerica Institute.

The information, data, or work presented herein was funded in part by an *agency* of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

### References

dchopkins@ncsu.edu

#### NC STATE UNIVERSITY

PACKAGING RESEARCH IN ELECTRONIC ENERGY SYSTEMS

- 1. U.S. Department of Energy, Office of Energy Efficiency & Renewable Energy. (2015, July 21). Power America [Online]. Available: http://energy.gov/eere/amo/power-america

- 2. The White House Blog. (2014, January 15). Wide Bandgap Semiconductors: Essential to Our Technology Future [Online]. Available:https://www.whitehouse.gov/blog/2014/01/15/wide-bandgapsemiconductors-essential-our-technology-future

- 3. McKinsey&Company, GSA Semiconductor Leaders Forum Taiwan. (2012, November 7). Unleashing Growth in Wide Bandgap: The upcoming disruptions in power electronics [Online]. Available: http://www.gsaglobal.org/events/2012/1107/docs/slft2012\_wiseman.pdf

- 4. NDT Resource Center. (2015, April 13). Refraction and Snell's Law [Online]. Available: https://www.ndeed.org/EducationResources/CommunityCollege/Ultrasonics/Physics/refractionsnells.htm

- 5. The Engineering Toolbox. (2015, April 5). Refractive Index of Some Common Liquids, Solids, and Gases [Online]. Available: http://www.engineeringtoolbox.com/refractive-index-d\_1264.html

- 6. Z. Chen, "Characterization and Modeling of High-Switching-Speed Behavior of SiC Active Devices," M.S. thesis, Dept. Elec. Eng., VA Polytechnic Inst., Blacksburg, VA, 2009.

- 7. Modeling and experimental study of thin bond line thermal interface material failure Shidong Li (IBM Corp., Hopewell Junction, NY, United States); Sinha, T.; Davis, T.J.; Sikka, K.; Bodenweber, P. Source: 2013 IEEE 63rd ECTC, p 803-6, 2013

- In-situ thickness method of measuring thermo-physical properties of polymer-like thermal interface materials [microelectronics cooling applications] Smith, R.A. (Micro-Electron. Heat Transfer Lab., Waterloo Univ., Ont., Canada); Culharn, R.J. Source: Twenty First Annual IEEE Semiconductor Thermal Measurement and Management Symposium (IEEE Cat. No.05CH37651), p 53-63, 2005

- Effect of the thickness of a thermal interface material (solder) on heat transfer between copper surfaces Xiangcheng Luo (Composite Mater. Res. Lab., State Univ. of New York, Buffalo, Buffalo, NY, United States); Chung, D.D.L. Source: International Journal of Microcircuits and Electronic Packaging, v 24, n 2, p 141-7, 2001

- 10. Burress, T.; Campbell, S., "Benchmarking EV and HEV power electronics and electric machines," Transportation Electrification Conference and Expo (ITEC), 2013 IEEE , vol., no., pp.1,6, 16-19 June 2013, doi: 10.1109/ITEC.2013.6574498

- 11. Burress, T.; Campbell, S., "Benchmarking EV and HEV power electronics and electric machines," Transportation Electrification Conference and Expo (ITEC), 2013 IEEE, vol., no., pp.1,6, 16-19 June 2013, doi: 10.1109/ITEC.2013.6574498

- 12. M. Arun Noyal Doss, V.Ganapathy, R. Sridhar, S.S. Dash, D. Mahesh. "Analytical and Simulation Analysis of Stator Tooth on Cogging Torque of Brushless DC Motor Using Finite Element Analysis," in Proc. ICPERES 2014, pp. 1-8.

- 13. M. Valan Rajkumar, P.S. Manoharan. "Modeling and Simulation of Three-Phase DCMLI Using SVPWM for Photovoltaic System," in Proc. ICPERES 2014, pp. 39-45.

- 14. Schulz, M.; Allen, S.T.; Pohl, W., "The crucial influence of thermal interface material in power electronic design,"Semiconductor Thermal Measurement and Management Symposium (SEMI-THERM), 2013 29th Annual IEEE , vol., no., pp.251,254, 17-21 March 2013, doi: 10.1109/SEMITHERM.2013.6526839

- Gautam, D.; Wager, D.; Edington, M.; Musavi, F., "Performance comparison of thermal interface materials for power electronics applications," Applied Power Electronics Conference and Exposition (APEC), 2014 Twenty-Ninth Annual IEEE, vol., no., pp.3507,3511, 16-20 March 2014, doi: 10.1109/APEC.2014.6803814

- 16. Yafan Zhang; Belov, I.; Sarius, N.G.; Bakowski, M.; Nee, H.; Leisner, P., "Thermal evaluation of a liquid/air cooled integrated power inverter for hybrid vehicle applications," Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE), 2013 14th International Conference on , vol., no., pp.1,8, 14-17 April 2013, doi: 10.1109/EuroSimE.2013.6529944

- 17. Mantooth, H.A.; Kang Peng; Santi, E.; Hudgins, J.L., "Modeling of Wide Bandgap Power Semiconductor Devices—Part I," Electron Devices, IEEE Transactions on , vol.62, no.2, pp.423,433, Feb. 2015, doi: 10.1109/TED.2014.2368274

- 18. Santi, E.; Kang Peng; Mantooth, H.A.; Hudgins, J.L., "Modeling of Wide-Bandgap Power Semiconductor Devices—Part II," IEEE Trans. on Electron Devices, vol.62, no.2, pp.434,442, Feb. 2015, doi: 10.1109/TED.2014.2373373

### **PowerAmerica - Mission**

#### NC STATE UNIVERSITY

#### PACKAGING RESEARCH IN ELECTRONIC ENERGY SYSTEMS

- Eliminate 90% of the power losses in electricity conversion compared to current Sibased technology

- Speed up the proliferation of wide-bandgap (WBG) semiconductor devices into the market's commercial, consumer, and industrial sectors

- Enable design engineers to more easily simulate WBG-based power modules within their systems in order to witness multi-physical performance improvement

- Provide an open-source design tool that provides the basis to create an entire power module model library

PREES

Laboratory

## **Reference Slides**

#### NC STATE UNIVERSITY

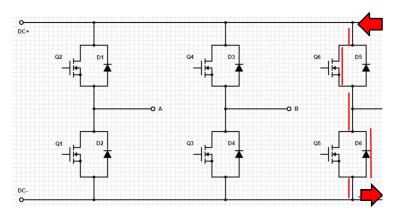

Connection configuration A and Q3D conduction path of CREE module terminals

### **PREES** Laboratory PACKAGING RESEARCH IN ELECTRONIC ENERGY SYSTEMS

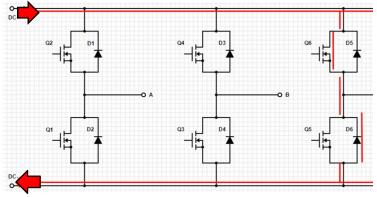

Connection configuration B and Q3D conduction path of CREE module terminals

FREEDAW SYSTEMS CENTER

**PREES** Laboratory PACKAGING RESEARCH IN ELECTRONIC ENERGY SYSTEMS

### Maximum Ratings (T<sub>c</sub> = 25°C unless otherwise specified)

| L <sub>stray</sub> Stray Inductance 30 nH Measured from pins 25-26 to 27-28 |

|-----------------------------------------------------------------------------|

|-----------------------------------------------------------------------------|

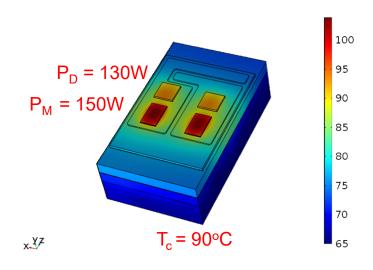

# **Comparison with Datasheet**

#### Thermal Characteristics

| Symbol                                                          | Parameter                                       | Min. | Тур. | Max. | Unit | Test Conditions                       | Note |

|-----------------------------------------------------------------|-------------------------------------------------|------|------|------|------|---------------------------------------|------|

| Rthacm                                                          | M Thermal Resistance Juction-to-Case for MOSFET |      | 0.37 | 0.40 | °c/w | $T_c = 90 \ ^{\circ}C, P_D = 150 \ W$ |      |

| R <sub>INICD</sub> Thermal Resistance Juction-to-Case for Diode |                                                 |      | 0.42 | 0.43 |      | $T_c = 90 \ ^{\circ}C, P_D = 130 \ W$ |      |